JED204B是什么?JESD204B的分类及优缺点介绍

接口/总线/驱动

描述

1、JED204B是什么?

一种新型的基于高速SERDES的ADC/DAC数据传输接口。ADC/DAC的采样速率变得越来越高,数据的吞吐量越来越大,对于500MSPS以上的ADC/DAC,动辄就是几十个G的数据吞吐率,采用传统的CMOS和LVDS已经很难满足设计要求,JESD204B应运而生。现在各大厂商的高速ADC/DAC上基本都采用了这种接口。

2、JESD204B的优缺点

2.1、优点:

a) 减少了PCB布板空间。

b) 减小了器件的引脚和封装大小。

c) 更简单的时序控制

2.2、 缺点:

a) 更复杂的电路设计,需要特殊的时钟电路

b) 增加了接口的传输延时

2.3、下表是JESD204B、LVDS接口之间的对比:

| 接口类型 | JESD204B | LVDS |

| 最高速率 | 12.5Gbps | 1Gbps(DDR) |

| 是否需要随路的时钟线 | 不需要,采用CDR技术从数据流中恢复时钟 | 需要时钟线:一条差分位同步时钟线,一条差分帧同步时钟线 |

| 是否需要链路对齐 | 不需要 | 需要数据线和时钟线之间严格对齐 |

| 引脚数(14bit,1GSPS采样) | 4条(2对数据差分线) | 32条(12对数据差分线+2对差分时钟线) |

3、JED204B种类

JESD204B一共有三种子类,分别是子类0,子类1和子类2。三个子类主要是根据同步方式的不同划分的,现在大部分ADC/DAC都使用的子类1,所以接下来主要讲解子类1。

JESD204B包括3个之类,分别是子类0,子类1,子类2;三个子类主要是根据同步方式的不同划分的。子类0兼容JESD204A,子类1使用SYSREF同步,子类2使用SYNC进行同步。只有子类1和子类2支持确定性延迟——发送端到接收端之间的链路延迟固定。

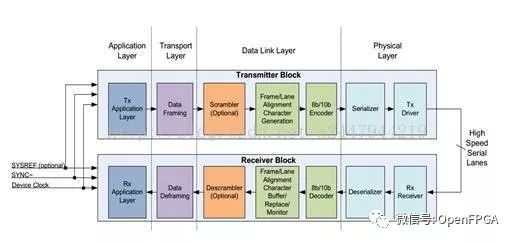

大部分的ADC和DAC都支持子类1,JESD204B标准协议中子类1包括:传输层,链路层,物理层。在少部分资料中也会介绍含有应用层,应用层是对JESD204B进行配置的接口,在标准协议中是不含此层,只是为了便于理解,添加的一个层。传输层负责将采样数据映射为数据帧。链路层负责链路的建立,数据传输。物理层负责数据的发送和接收。

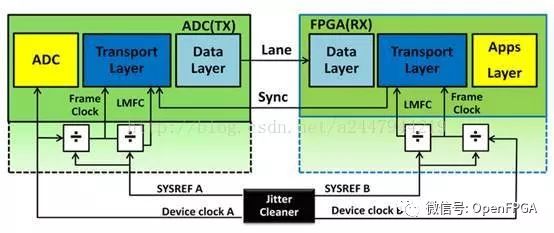

JESD204B相对于LVDS接口来说,不需要位同步和帧同步时钟,但是JESD204B仍然需要两个同源时钟对两端的发射设备和接收设备进行同步,JESD204B的物理连接如下图:

编辑:黄飞

-

JESD204B使用说明2024-12-18 3212

-

JESD204B规范的传输层介绍2023-11-28 680

-

JESD204B的优势2022-11-23 785

-

JESD204B协议介绍2022-11-21 964

-

JESD204B:适合您吗?2022-11-07 750

-

如何构建您的JESD204B 链路2022-11-04 991

-

如何去实现JESD204B时钟?2021-05-18 3150

-

JESD204B是什么工作原理?控制字符是什么?2021-04-06 1743

-

JESD204B串行接口时钟的优势2019-06-19 3759

-

JESD204B生存指南2019-05-28 1915

-

JESD204B的系统级优势2018-09-18 2419

-

JESD204B标准及演进历程2017-11-18 15057

-

JESD204B SystemC module 设计简介(一)2017-11-17 3642

全部0条评论

快来发表一下你的评论吧 !