I2C上拉电阻如何选择合适的阻值?

描述

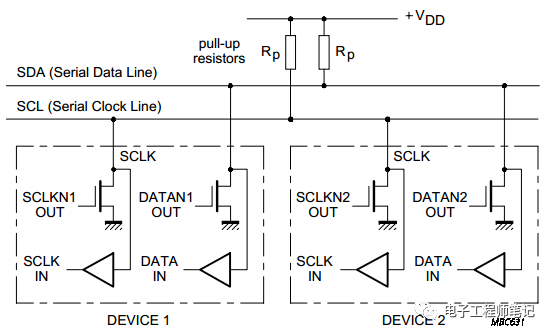

I2C总线是微电子通信控制领域中常用的一种总线标准,具备接线少,控制简单,速率高等优点。在I2C电路中常见的上拉电阻有1k、1.5k、2.2k、4.7k、5.1k、10k等等,但是应该如何根据开发要求选择合适的阻值呢?下图为I2C内部结构

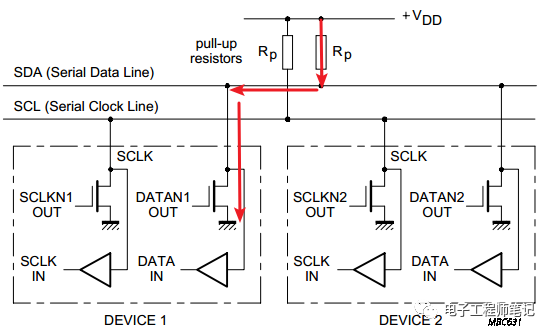

假设SDA输出低电平时,即MOS管导通。那么,可以求出上拉电阻R的阻值

上拉电阻:

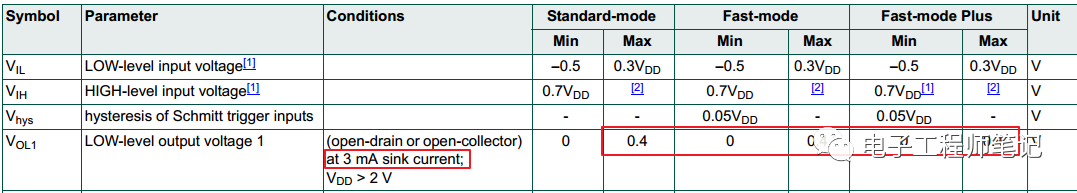

VOL定义为在漏极开路或集电极开路时,有3mA下拉电流时的低电平输出电压。IOL就是该端口的灌电流,即IOL=3mA。由上式可得,当VDD不变, VOL取最大值时,上拉电阻有最小值。

根据I2C协议,端口输出低电平的最高允许电压是0.4V。

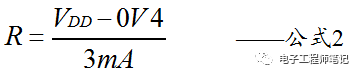

So,式1可以改为:

由式2可以得出:电源电压决定了上拉电阻的最小值。因此,当VDD=5V时,最小上拉电阻约为1.5k;当VDD=3V3时,约为1k。

由于I2C总线端口的高电平是通过上拉电阻实现,线上的电平从低变高时,电源通过上拉电阻对线上负载电容CL充电,这需要一定的上升时间。

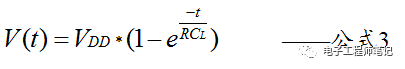

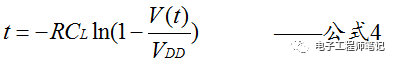

电容充电一般公式:

整理可得:

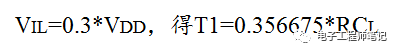

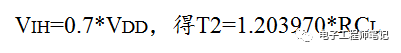

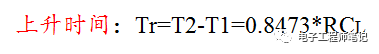

I2C规范将低于VIL或0.3VDD的电压定义为逻辑低电平,同样将高于VIH或0.7VDD的电压定义为逻辑高电平,由式4可以求得:

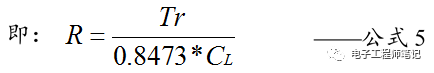

由式5可判断,当Tr取最大值,CL取最小值时,R有最大值。

由于不同模式下,上升沿的最大时间及总线负载最大容限要求不同,标准模式、快速模式、高速模式分别是:1000ns/400pF、300ns/400pF、120ns/550pF。

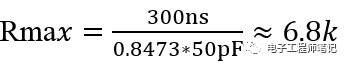

以快速模式下,负载电容50pF为例,则有:

结论:电源电压决定上拉电阻的最小值,总线负载电容决定上拉电阻的最大值。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

上拉电阻的含义、上拉电阻在I2C电路中的作用2022-09-08 8755

-

聊聊I2C总线上拉电阻2023-07-14 6743

-

I2C总线上拉电阻阻值如何确定?2024-12-27 3069

-

I2C总线应用中的几个问题2009-09-13 1336

-

tpa2051d3在I2C上拉电阻的选择2017-05-23 1597

-

上拉电阻的阻值选择2018-08-30 22058

-

i2c上拉电阻大小_i2c上拉电阻的作用2020-11-24 28684

-

I2C总线一定要接上拉电阻?上拉电阻阻值怎么确定?2021-06-21 16850

-

I2C上拉电阻设计2022-01-14 1388

-

I2C上拉电阻计算公式2022-09-02 5420

-

I2C为什么要接上拉电阻?上拉电阻阻值怎么确定?2023-02-06 2556

-

I2C的开漏输出和上拉电阻2023-07-02 7915

-

上拉电阻在I2C电路中的作用 I2C上拉电阻的计算方法2023-07-25 4875

-

如何选择I2C总线拉电阻2025-01-17 1811

-

上拉电阻阻值怎么选择2025-02-05 1806

全部0条评论

快来发表一下你的评论吧 !