如何设计一个USB电路板?有哪些注意事项?

描述

在 USB2.0 设计中,USB 差分 D+/ D- 工作于 480Mbps的高速模式,系统时钟可工作于 12 MHz、48 MHz 及 60 MHz,在硬件设计中属于高速设计部分,有许多方面需要特别注意,因为USB电缆容易形成单极天线,必须防止RF电流耦合到线缆上。

01当设计一个USB 电路板时,需要重点关注

D+/D- :高速差分信号,容易受到外界噪声的干扰,影响信号的传输质量。

供电信号VBUS :供电信号引脚上的电源纹波会对数据传输信号产生很大的干扰,因此必须经过滤波。 而且接地信号也要经过滤波,减少干扰。 对于大电流负载也要注意电压跌落。

02PCB Latout 注意

D+/D-等长控制 :当工作在高速模式或者USB3.0速率时,需要保证D+/D-等长布线。 D+和D–走线的长度差异不应超过50 mil(1.25 mm),从而可以避免信号时滞并防止对交变电压产生影响

D+和D–走线的长度要小于3 英寸(75 mm)。 推荐两条走线长度不大于1 英寸

布线中,应将直角进行两次45°的弯曲或变成圆角(而不是90°的直角弯曲)

阻抗控制 :D+/D-差分布线,阻抗控制90Ω±10%

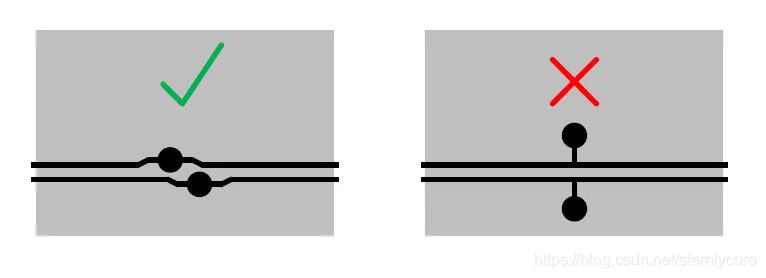

No Stub(无支点) :当增加测试点或一些器件时,尽量保证差分信号无支点,如下示意:

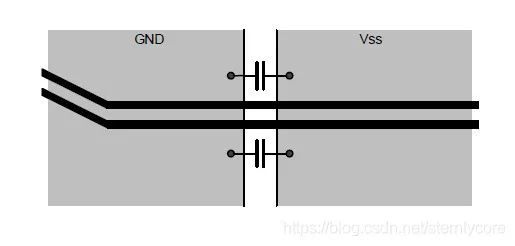

完整参考平面:D+/D-阻抗实现需要完整参考平面,不能出现分裂参考平面。 如果不得以出现分离参考平面,需要连接跨接电容,如下示意:

03问题具体分析原理设计

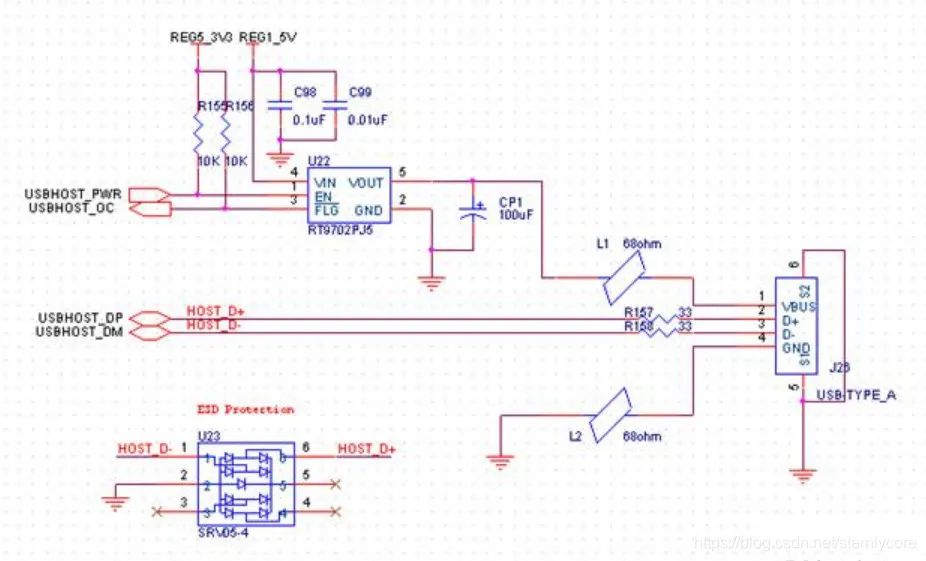

现在芯片集成度很高,USB_Host外围设计比较简单,如下示意:

USB控制器信号 :USB_PWR,DP,DM,USB_OC,USB_VBUS

限流器件 :RT9702,USB2.0规范负载从VBUS最高索取500mA电流,超过500mA会关断

静电保护 :SRV05 防止静电把连接器信号打坏,靠近USB接口放置

磁珠L1/L2 :消除电源信号上的高频噪声,增强抗抖动性能。 磁珠的电阻值介于47ohm至1000ohm之间(100MHz信号频率时),靠近连接器放置

R157/R158 :匹配电阻,防止信号过冲,阻值一般在10Ω-33Ω之间,靠近USB控制器放置

CP1 :大电容保证插拔瞬间或大数量数据传输时导致VBUS电压跌乱过大,靠近USB接口放置

审核编辑:汤梓红

-

PCBA加工电路板返修注意事项2023-04-06 2700

-

电路板焊接需要重点关注的注意事项2023-03-06 7098

-

设计高速电路板的注意事项.zip2022-12-30 742

-

ULLGA 封装的电路板安装注意事项2022-11-15 983

-

布局浪涌抑制电路板的注意事项2022-03-29 5366

-

<b>04:</b>混合信号电路板设计注意事项2021-04-28 789

-

用PROTEUS7.5制作印制电路板的注意事项是什么2021-04-26 3755

-

柔性电路板怎么焊接_柔性电路板焊接注意事项2019-05-21 6944

-

PCB设计高频电路板的布线技巧和注意事项详细概述2018-10-14 7469

-

在Hercules电路板设计中的注意事项(1)2018-08-20 4474

-

在Hercules电路板设计中的注意事项(2)2018-08-08 4074

-

设计高速电路板的注意事项2016-12-14 1175

-

印制电路板的版面设计注意事项2009-11-19 1792

全部0条评论

快来发表一下你的评论吧 !