ARM SMMU Data structures之Stream Table

描述

incoming transaction的StreamID可以找到一个STE。SMMU支持两种Stream table格式,格式由Stream table base registers设置。

传入的StreamID会根据指定的table size进行范围检查,StreamID超出范围,则transaction就会被terminated,并且记录事件C_BAD_STREAMID。

当支持两个Security states时,如SMMU_S_IDR1.SECURE_IMPL == 1所示,使用SEC_SID标识transaction 是 Secure or Non-secure,后续使用各自独立的软件接口和数据结构。

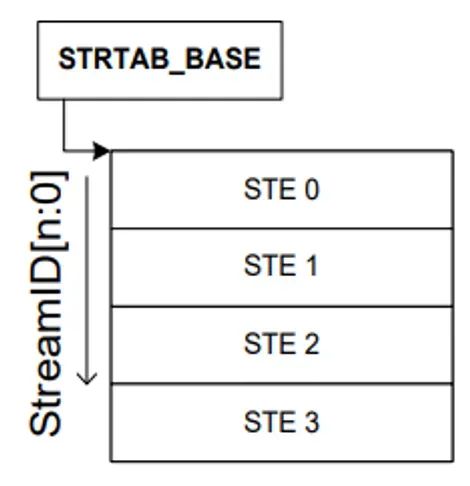

Linear Stream Table

Linear Stream Table

linear Stream table是 STE 的连续数组,由 StreamID 从 0 开始索引。该大小可配置为2^n ,最多为 SMMU 在硬件中支持的最大 StreamID 位数。

2-level Stream Table

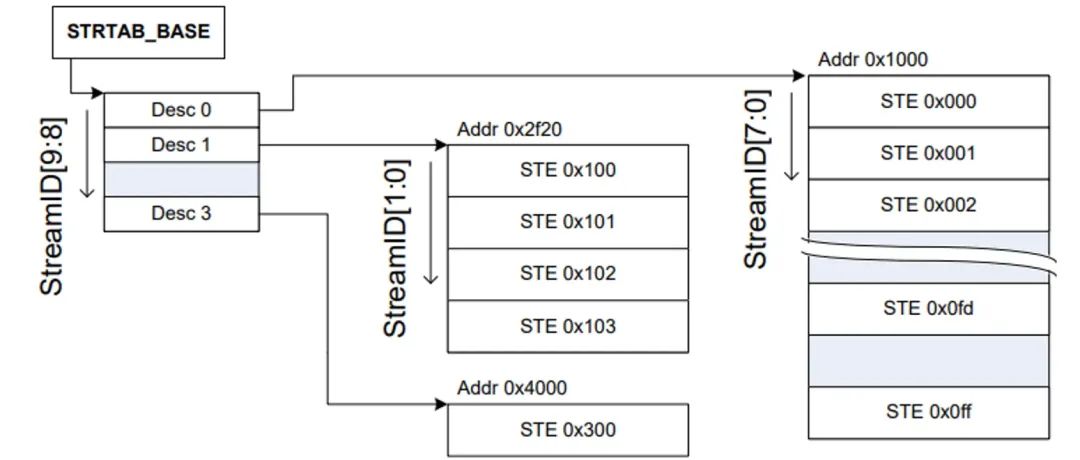

Two-level Stream Table with SPLIT == 8

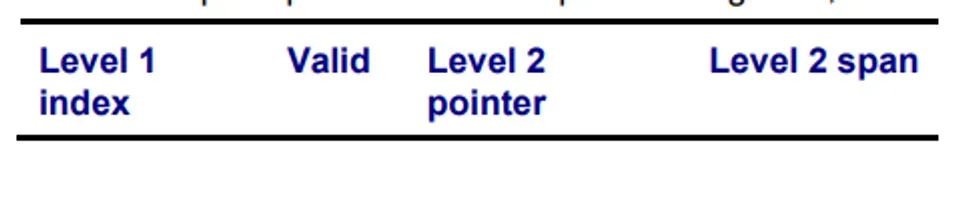

2-level Stream table包含一个top-level table,该表包含指向多个second-level tables(STE 线性数组)的指针。整个结构涵盖的 StreamID 范围可配置为 SMMU 支持的最大数量,但second-level tables不必完全填充,并且大小可能会有所不同。这节省了内存并避免了对非常大的 StreamID 空间进行大量连续分配物理空间的要求。top-level descriptors包含指向second-level table的指针以及该second-level table表示的 StreamID 范围。每个second-level table的指针(descriptor )也可以标记为invalid。

top-level table由 StreamID[n:x] 索引,其中 n 是覆盖的最高 StreamID 位,x 是由 SMMU_(S_)STRTAB_BASE_CFG.SPLIT 给出的可配置分割点。second-level tables 的索引最多为 StreamID[x - 1:0],具体取决于每个表的跨度(span)。

SMMU_IDR0.ST_LEVEL 字段可以指示是否支持2-level Stream table。在支持2-level Stream Tables的情况下,可以使用 6、8 和 10 位的分割点。SMMU实现可以支持linear Stream Table,或者同时支持 linear和2-level Stream Table。

支持超过 64 个 StreamID(6 位 StreamID)的 SMMU 必须支持2-level Stream tables。

支持少于64个StreamID的SMMU实现也可能支持 2-level Stream Tables,但这样做通常没有用,因为所有streams 可以填充到一个second-level table。意味着当linear Stream table的最大大小而无法容纳进一个4KB页面时,就必须支持two-level tables。

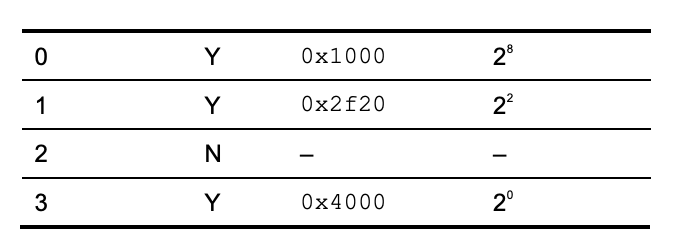

在这个例子中:

• StreamIDs 0-1023(4 × 8-bit level 2 tables)被表示,但不是所有level 2 tables都有效。

• StreamIDs 0-255 由位于 0x1000 的 STE 数组。

• StreamIDs 256-259 由位于 0x2F20 的 STE 数组。

• StreamIDs 512-767 都是无效的。

• StreamID 768 的STE 位于0x4000。

审核编辑:刘清

-

ARM系统内存管理单元架构规范SMMU架构2.0版2023-08-12 926

-

SMMU VA->PA的转换流程介绍2023-05-15 1916

-

ARM SMMU Data structure之Context Descriptors2023-05-11 1828

-

ARM SMMU具有三种接口供软件使用2023-05-08 1149

-

SMMU数据结构格式之Level 1 Stream Table Descriptor介绍2023-05-06 1917

-

SMMU数据结构格式之Stream Table Entry...V和Config介绍2023-05-04 2450

-

SMMU数据结构格式2023-04-28 1676

-

SMMU学习这一篇就够了2023-02-23 4665

-

多个设备是否可以共用一个SMMU StreamID?2022-11-07 6181

-

ARM系列之SMMU总线资料合集2022-04-11 5854

-

arm smmu的原理2020-10-09 5642

-

ARM720T DATA2017-10-25 912

-

Algorithms and Data Structures The Science of Computing2016-03-28 1652

全部0条评论

快来发表一下你的评论吧 !