在高速ADC中增加SFDR的局限性分析

电子说

描述

了解模数转换器 (ADC) 中的两个非线性源、无杂散动态范围 (SFDR) 和 SNR(信噪比)。

无杂散动态范围 (SFDR)是 表征电路线性性能的常用方法。该规范在处理通信系统时特别有用。通过检查 AD 转换器 (ADC) 的一般功能,本文试图解释限制 ADC SFDR 性能的两个主要非线性源,即采样保持 (S/H) 电路和 ADC 的编码器部分。

我们还将了解 ADC 中 SFDR 和SNR(信噪比)之间的一般权衡,并为以后有关应用抖动技术改善 ADC SFDR 的有趣讨论奠定基础。抖动是一种故意向 ADC 输入添加适当的噪声分量以改善 AD 转换系统的某些性能方面的技术。认为添加噪声可以改善 SFDR 这听起来很神奇。

然而,在深入探讨之前,让我们快速回顾一下什么是 SFDR 及其重要性。

什么是无杂散动态范围 (SFDR)?为什么 SFDR 很重要?

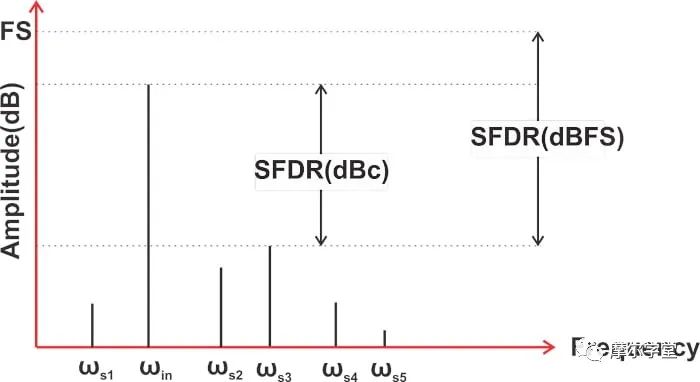

有几种不同的规范可用于表征电路线性度。一种常用的规范是 SFDR 指标。该指标定义为所需信号幅度与感兴趣带宽内最大杂散的比率(图 1)。

图 1. 显示 SFDR 指标的图表。

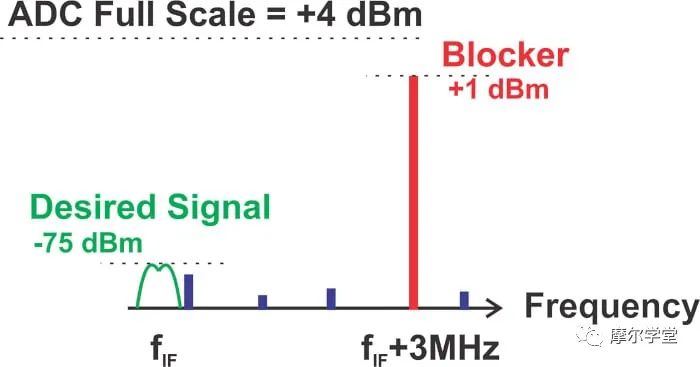

对于 ADC,SFDR 展示了 ADC 如何在存在大信号的情况下同时处理小信号。例如,考虑一个接收器应用程序。假设 ADC 输入包含一个 +1 dBm 阻塞信号和一个 -75 dBm 所需信号。在这种情况下,由于ADC 非线性,大阻断器会在 ADC 输出端产生不需要的杂散。这些不需要的杂散在图 2 中以紫色组件显示。

图 2. 以紫色显示不需要的杂散的图表。

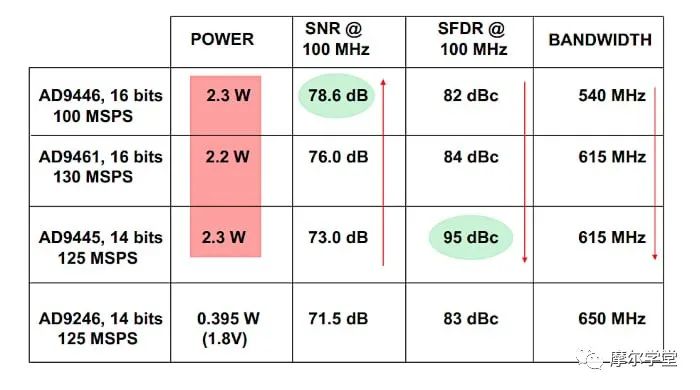

如果杂散距离所需信号足够近并且足够大,它可能会将 SNR 降低到不可接受的水平。当今通信系统的严格要求可能需要 95 dB 范围内的高 SFDR 值。然而,普通的 ADC 无法提供这种级别的线性度。下面的表 1 比较了 Analog Devices 的四种高性能 ADC 的一些关键参数,应该可以帮助您了解高性能 ADC 中的 SFDR 范围。

表 1. 四种高性能 ADC 的关键参数。数据由Analog Devices提供

此外,该表强调了 SNR 和 SFDR 指标之间的权衡。对于此表中的前三个 ADC,它们使用相同的 IC 技术并具有相同的功耗,SFDR 和 SNR 之间存在反比关系。我们稍后会在本文中探讨这种权衡的起源。在此之前,让我们回答一个重要问题:在高速 ADC 中增加 SFDR 的主要限制是什么?

ADC 中的静态和动态线性度

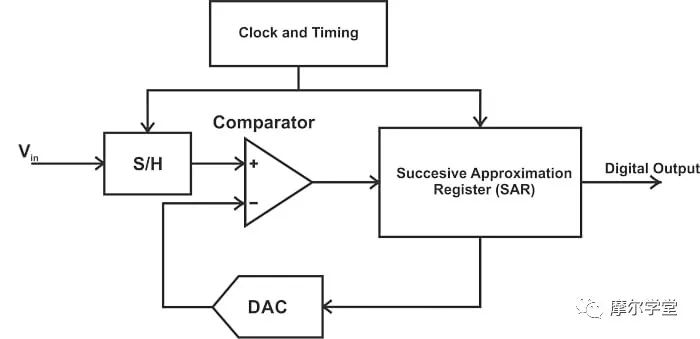

ADC 是基于许多不同电路架构设计的复杂系统,例如闪存、SAR、delta-sigma (ΔΣ)和流水线结构。根据架构和特定的电路实现,不同的电路组件可能是非线性的主要来源。尽管有许多设计,但我们仍然可以认识到在高速 ADC 中增加 SFDR 的两个主要限制,即 S/H 电路和 ADC 的编码器部分。为了更好地理解这一点,请考虑图 3 中描绘的 SAR ADC 的框图。

图 3. SAR ADC 的框图。

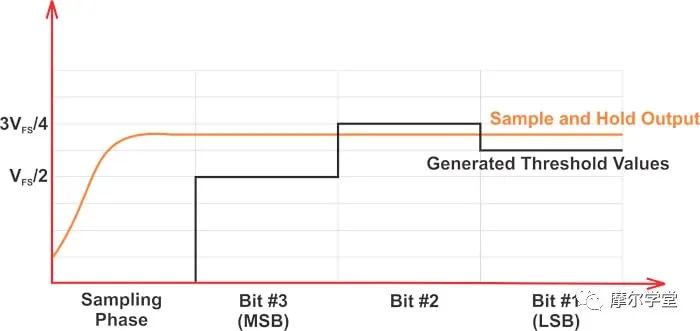

SAR 数字化算法的第一步是采样阶段,在此期间 S/H 获取输入值。该样本将在整个转换阶段保留。在转换阶段,将采集的样本连续与适当的阈值水平进行比较,以找到输入的数字等效值。要确定输出的每一位,需要一个时钟周期。假设采样阶段也需要一个时钟周期,对于一个 N 位 SAR ADC,我们需要 N + 1 个时钟周期。图 4 显示了 3 位 SAR ADC 的 S/H 输出和阈值波形。

图 4. 3 位 SAR ADC 的 S/H 输出和阈值波形。

这里的要点是,对于给定的转换阶段,无论输入频率是多少,S/H 之后的电路元件都理想地处理直流信号。因此,SAR ADC 的比较器或内部DAC(数模转换器)内的任何非线性 都不会随输入频率而变化。我们可以说 ADC 编码器部分的非线性会导致系统的静态(或 DC)非线性。静态非线性的特征在于 ADC 传递函数中的DNL(微分非线性)和INL(积分非线性)误差。

S/H 非线性如何?与有效处理直流信号的编码器部分不同,S/H“看到”交流信号。我们将在下一节中讨论 S/H 非线性的重要部分如何随输入频率变化。因此,S/H 决定了 ADC 的动态(或 AC)线性度。

S/H 电路非线性

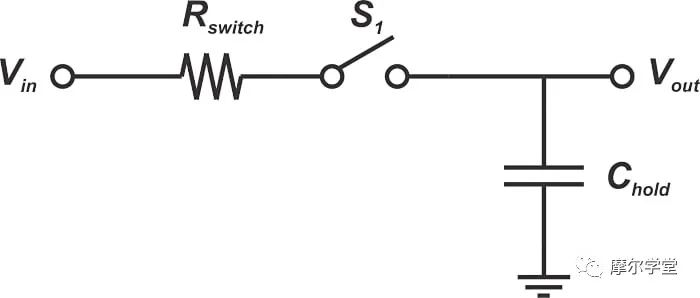

要了解 S/H 非线性,请考虑图 5 中所示的简单 S/H 电路。

图 5. S/H 电路示例。

这个基本的 S/H 由一个采样开关 S1 和一个保持电容(C hold ) 组成,后者用于存储采集的样本。

电路操作包括两种模式:采样(或采集模式)和保持模式。在采样模式下,开关导通,电容电压跟踪输入。在采样瞬间,开关关闭并断开 C hold 与输入的连接。这将启动保持模式,其中电容器保持采集的样本。

实际上,我们不可能有零电阻的理想开关。为了强调这一点,上图明确显示了开关电阻 R switch。开关电阻的热噪声是高分辨率奈奎斯特速率 ADC 中的主要噪声来源。为了解决这个问题,保持电容的值通常选择得足够大以限制带宽 ,从而限制系统的噪声。然而,有限的带宽意味着 S/H 的输出无法立即达到其最终值。这是由于 RC 网络的时间常数,由下式给出

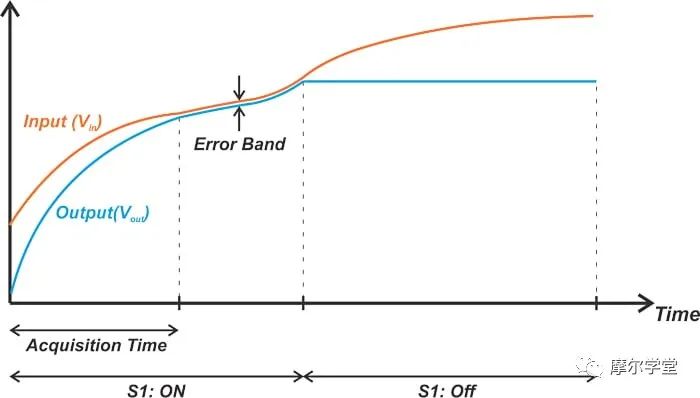

图 6 显示了 S/H 操作的一个周期的示例波形。

图 6. S/H 电路操作一个周期的示例波形。

S/H 需要一些时间(如图中的“采集时间”所示)才能稳定在最终值附近的指定误差范围内。在采集时间之后,S/H 能够以较小的误差跟踪输入。采集时间取决于 R switch、 C hold 和最大允许误差的值。此外,采集时间对 ADC 的最大采样率设置了上限。

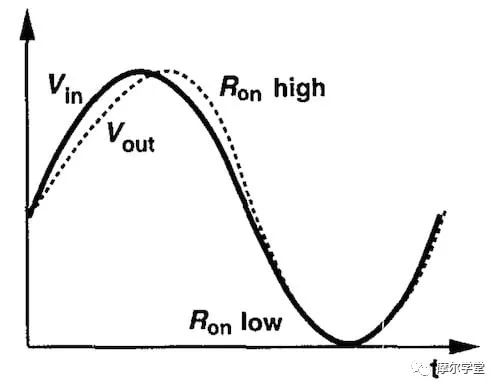

实际上,开关电阻不是恒定的,会随着输入电平的变化而变化。R switch 对输入的依赖性会导致输入相关的相移,从而导致谐波失真。图 7 显示了 R开关随输入电平增加的情况的示例波形 。

图 7. R开关 随输入电平增加时的示例波形。图片由B. Razavi提供

请注意,此相移(或非线性)随频率变化。例如,在比 RC 网络的极点小得多的频率下,相移为零,R开关的微小变化 对线性度的影响可以忽略不计。然而,随着我们增加频率,相移变得越来越显着。

值得一提的是,R开关 随输入的变化只是 S/H 非线性的一个来源。开关的输入相关电荷注入以及输入相关采样瞬间等机制是导致 S/H 非线性的其他现象。后一种机制是指开关关闭的瞬间可以随输入电平的变化而变化。

转换率限制问题

S/H 电路的频率相关非线性也可以通过注意到驱动保持电容器的电路具有有限的转换速率来解释。图 8 更详细地显示了典型 S/H 电路的框图。

图 8. 更详细的 S/H 电路框图。图片由Analog Devices提供。

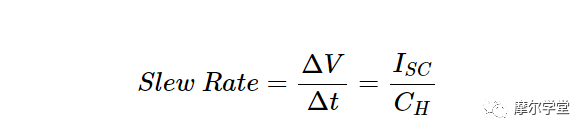

在该电路中,第一个放大器通过向信号源呈现高阻抗来缓冲输入。它还提供电流增益来为保持电容器充电。右侧放大器用作输出缓冲器,并防止 S/H 输出电压在保持模式期间被后续电路的输入阻抗放电。假设输入缓冲器的短路输出电流为I SC。这是缓冲器可以提供给 C H的最大电流。因此,压摆率(或 S/H 输出的最大变化率)由公式 1 给出。

等式 1。

对于正弦波输入:

信号的最大变化率由下式给出:

对于给定的大信号输入,增加频率可以使信号的变化率大于 S/H 的压摆率。在这种情况下,S/H 输出无法足够快地跟随输入,从而导致信号失真问题。缺乏显示足够转换率以跟上快速变化的模拟输入的 S/H 是许多 ADC 无法在超过几兆赫信号带宽的情况下表现良好的一个关键原因。

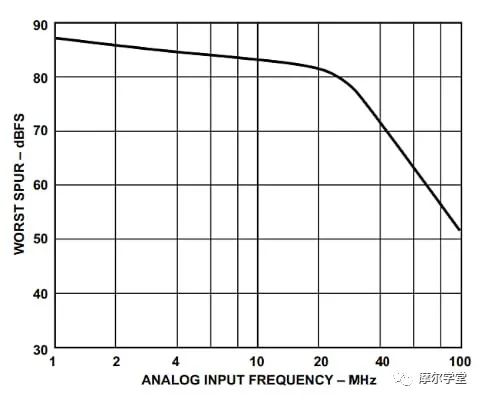

例如,考虑Analog Devices 的AD9042 。尽管 AD9042 是专门设计有宽带、高 SFDR 前端的转换器,但其 SFDR 仍会随着输入频率而降低,如图 9 所示。

图 9. 显示 AD9042 的 SFDR 如何随输入频率降低的图表。图片由Analog Devices提供。

SNR-SFDR 权衡

上述讨论还解释了我们在本文前面提到的 SNR-SFDR 权衡。请注意,较大的保持电容器会导致较低的转换率(公式 1)和较高的失真(或较低的 SFDR)。另一方面,较大的电容器会降低系统带宽并改善噪声性能(更高的 SNR)。

应用抖动改善 SFDR

如上所述,改进 SFDR 有两个主要限制:S/H 电路产生的非线性和 ADC 编码器部分产生的非线性。没有任何外部措施可以减少 S/H 电路产生的失真。然而,抖动技术可以降低 ADC 编码器部分的非线性。这将在本系列的下一篇文章中讨论。

-

34063的局限性2011-06-12 5327

-

FPGA的优势与局限性2017-12-20 7607

-

无线网络有什么局限性?2019-08-23 3339

-

MySQL优化之查询性能优化之查询优化器的局限性与提示2020-06-02 2111

-

超声波液位计的局限性及安装要求2020-06-19 1866

-

运算放大器的精度局限性是什么2021-03-11 2000

-

基于FPGA的神经网络的性能评估及局限性2021-04-30 1738

-

RS-485自动换向电路设计的局限性2015-12-21 907

-

基于EPON在广电网络中的局限性2017-09-20 1135

-

WSN中LEACH协议局限性的分析与改进2021-09-15 944

-

ChatGPT在自然语言处理中的局限性和挑战2023-04-18 2811

-

千兆光模块存在哪些局限性?2023-10-16 1479

-

在高速ADC中增加SFDR的主要限制是什么?2023-10-31 1679

-

WDM技术的缺点和局限性2024-08-09 2566

-

在高速ADC中通过校准改进SFDR2024-08-30 440

全部0条评论

快来发表一下你的评论吧 !