深刻理解跨时钟域的三个主要问题和解决方案

描述

如今,SoCs正变得越来越复杂,数据经常从一个时钟域传输到另一个时钟域。

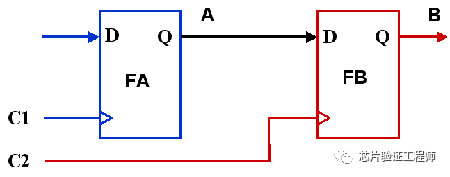

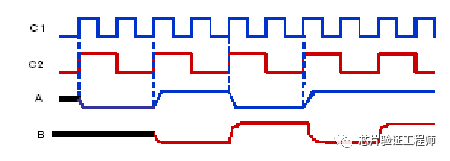

上图信号A由C1时钟域触发,被C2时钟域采样。 根据这两个时钟之间的关系,在将数据从源时钟传输到目标时钟时,可能会出现不同类型的问题,并且这些问题的解决方案也有所不同。

本文讨论了不同类型的跨时钟域,以及每种类型中可能遇到的问题及其解决方案。 在接下来的所有部分中,都直接使用了上图所示的信号名称。 例如,C1和C2分别表示源时钟和目标时钟。 类似地,A和B分别被用作源触发器输出和目标触发器输出。 此外,源和目标触发器被假定为正沿触发。

跨时钟域问题

本节描述了在出现跨时钟域时可能出现的三个主要问题,然后还描述了这些问题的解决方案。

A.亚稳态问题。

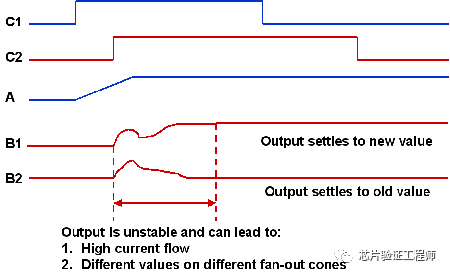

如果信号A上的翻转发生在非常接近时钟C2的边沿处,它可能会导致在目标触发器“FB”处的setup 或hold 违反。 结果,输出信号B进行无限振荡。 因此,输出是不稳定的,在C2的下一个时钟边缘到达之前也可能会稳定到某个稳定的值。 这种现象被称为亚稳态,或者说触发器“FB”已经进入亚稳态。

从设计的角度来看,亚稳态又会产生以下后果:

1、 如果不稳定的数据被输入到设计中的其他几个地方,它可能会导致大电流,在最坏的情况下甚至导致芯片烧坏。

2、 不同的 fan-out可能会读取不同的信号值,并可能导致设计进入未知的功能状态,导致设计出现功能问题。

3、 目标时钟域输出可能稳定到新值或返回到旧值。 然而,传播延迟可能很高,会导致时序问题。

如下图,如果输入信号A在非常接近C2时钟的上升沿翻转,则目标触发器的输出可以是亚稳态的。 因此,它可以不稳定,并可能最终稳定到信号B1和B2所描述的1或0。

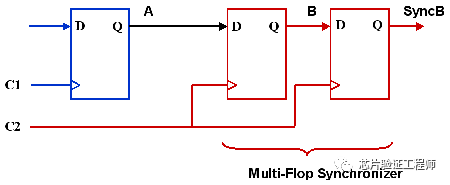

可以通过在目标域中添加同步器来避免亚稳态问题。 同步器允许振荡在足够的时间稳定下来,并确保在目标时钟域获得稳定的输出。 一个常用的同步器是一个级联触发器,如下图所示。

该结构主要用于设计中的控制信号和单比特数据信号。 多位的数据信号需要其他类型的同步方案,如MUX recirculation、握手和FIFO。

B.数据丢失

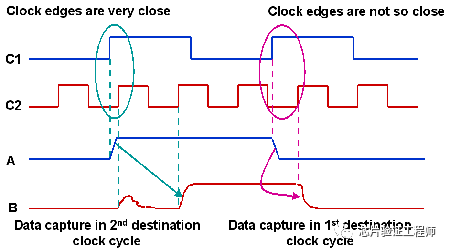

每当生成一个新的源数据时,由于亚稳态性,它可能不会在目标时钟的第一个周期中被目标域捕获。 只要源信号上的每个翻转都在目标域中被捕获,数据就不会丢失。 为了确保这一点,源数据应在一段最短的时间内保持稳定,以便满足对目标时钟的至少一个边沿的setup 和hold 时间的要求。

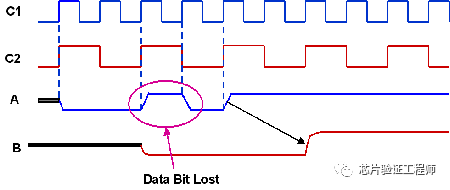

如果C1和C2的时钟边沿非常靠近,则在源数据A翻转之后的C2的第一个时钟边沿无法捕获它。 该数据最终被时钟C2的第二个时钟边沿捕获,如下图所示。

但是,如果在数据A翻转和时钟C2的边沿之间有足够的时间,则在C2的第一个周期捕获数据。 因此,源时钟域数据和目标时钟域数据之间可能不会一一对应。 无论如何,一般情况下源数据上的每个翻转都应该在目标时钟域中被捕获。

假设源时钟C1的速度是目标时钟C2的两倍,并且这两个时钟之间没有相位差。 进一步假设在时钟C1的正边沿生成的输入数据序列“A”为“00110011”。 在时钟C2的正边沿捕获的数据B将为“0101”。 在这里,由于信号A上的所有翻转都被B捕获了,所以数据不会丢失。

但是,如果输入序列为“00101111”,则目标域中的输出将为“0011”。 这里输入序列中的第三个数据值“1”丢失。

为了防止数据丢失,数据应该在源时钟域中保持足够长的时间不变,以便在目标时钟域中正确捕获。 换句话说,在源数据上的每次转换之后,至少有一个目标时钟边沿应该到达没有违反setup或hold的地方,以便在目标时钟域中正确地捕获源数据。

C. 数据一致性

如前一节所示,每当在源时钟域中生成新数据时,可能需要1个或多个目标时钟周期来捕获它。 考虑这样一种情况,即多个信号从一个时钟域传输到另一个时钟域,并且每个信号使用多级触发器同步器分别进行同步。 如果所有信号同时发生变化,并且源时钟和目标时钟边沿接近,那么一些信号可能在第一个时钟周期中在目标域中被捕获,而另一些信号可能通过亚稳态在第二个时钟周期中被捕获。 这可能会导致目标端信号上的值组合无效。 也就是说,在这种情况下,数据的一致性已经丢失了。

如果这些信号一起控制着设计的某些功能,那么这种无效的状态可能会导致功能错误。

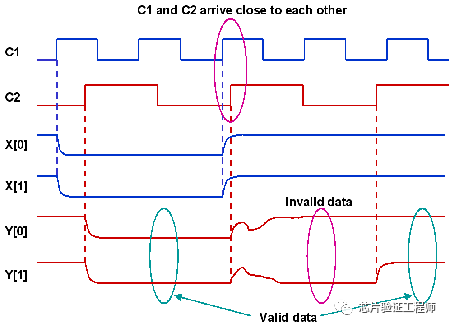

例如:假设“00”和“11”是由时钟C1生成的信号X[0:1]的两个有效值。 最初在X的两个位上都有一个从1->0的过渡。 这两个转变在第一个周期本身都被时钟C2捕获。 因此,信号Y变成了“00”。

接下来,在信号X的两个比特位上都有一个从0->1的转换。 在这里,时钟C2的上升沿接近于信号X的翻转。 X[0]上的翻转在第一个时钟周期中被捕获,而X[1]上的翻转在C2的第二个时钟周期中被捕获。 这将导致Y[0:1]上的一个中间值为“10”,这是一个无效的状态。 在这种情况下,数据的一致性丢失了。

在上面的示例中,问题的原因是所有比特没有在相同的目标时钟周期中捕获。 如果所有比特在同一周期中保留其原始值或更新值,则设计要么保持原始状态,要么进入正确的新状态( 参考异步FIFO )。

如果电路的设计方式是,在将设计从一种状态更改到另一种状态时,只需要更改一个位,那么该位将更改为一个新值或者保留原始值。 由于所有其他位在这两种状态下都有相同的值,所以在这种情况下,完整的总线要么变为新值,要么保留原始值。

这反过来又意味着,如果总线是格雷编码的,那么这个问题将会得到解决,并且将永远不会得到一个无效的状态。

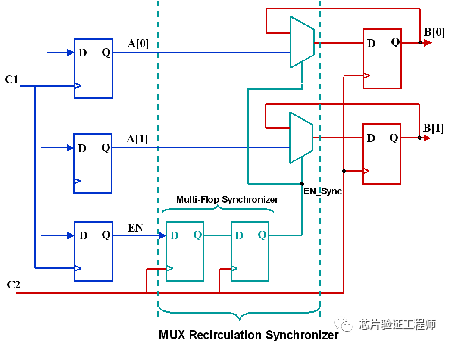

但是,这仅适用于控制总线,因为无法对数据总线进行格雷编码。在这种情况下,可以使用握手、FIFO和MUX recirculation(如下图)等其他技术来生成一个公共的控制逻辑来正确地传输数据。

这里,在源时钟域中产生的控制信号EN使用多级触发器同步器在目标域中进行同步。同步控制信号EN_Sync驱动mux的选择引脚,从而控制总线A所有位的数据传输。通过这种方式,总线的各个位不会单独同步,因此不存在数据不一致性。但是,重要的是要确保当控制信号被激活时,源域数据A[0:1]应保持不变。

审核编辑:汤梓红

-

FPGA设计中解决跨时钟域的三大方案2020-11-21 5268

-

跨时钟域控制信号传输设计方案2020-10-16 1562

-

跨时钟域的解决方案2024-01-08 1973

-

如何处理好FPGA设计中跨时钟域问题?2020-09-22 2398

-

探寻FPGA中三种跨时钟域处理方法2020-10-20 2391

-

三种跨时钟域处理的方法2021-01-08 2344

-

三种FPGA界最常用的跨时钟域处理法式2021-02-21 4462

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1720

-

讨论跨时钟域时可能出现的三个主要问题及其解决方案2022-06-23 2388

-

cdc路径方案帮您解决跨时钟域难题2017-11-30 8840

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2671

-

深刻理解PLC的扫描过程和执行原理2021-04-08 9928

-

关于跨时钟域的详细解答2021-04-27 5293

-

深刻理解Python中的元类(metaclass)2021-09-24 631

-

跨时钟域电路设计总结2023-05-18 1574

全部0条评论

快来发表一下你的评论吧 !