FPGA设计:GPIO怎么走全局时钟网络

可编程逻辑

1396人已加入

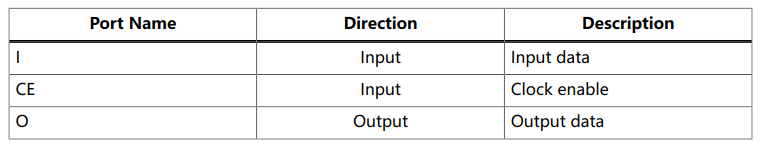

描述

易灵思提供了原语文档,可以查看每个原语。经常有人会问,如果普通的GPIO怎么走全局时钟网络,其实很简单,打开原主文档,找到EFX_GBUFCE,该部分提供了verilog和VHDL的用法。

EFX_GBUFCE既可以让GPIO走全局时钟网络也可以用于为时钟添加使能控制,当并不是随时需要该时钟时可以把时钟禁止以节省功耗。

CE_POLARITY用于控制CE是高有效还是低有效,如果为1则高有效,反之则低有效。

CE是时钟O的输出使能。

EFX_GBUFCE # ( .CE_POLARITY(1'b1) // 0 active low, 1 active high ) EFX_GBUFCE_inst ( .O(O), // Clock output to global clock network .I(I), // Clock input .CE(CE) // Clock gate );

另外要补充下,

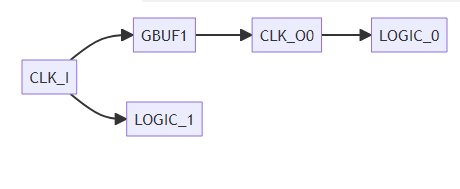

如果用了EFX_GBUFCE,并用CLK_O0作为时钟去控制逻辑,那CLK_I就不能再次自动上GBUFCE当作时钟来控制逻辑。如下图,这种方式是不支持的。

Quantum 钛金系列 Primitives User Guide (elitestek.com)

编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思FPGA全局时钟网络结构详解2013-11-28 14475

-

全局时钟资源和网络的路径和组件组成2022-07-14 4651

-

FPGA全局时钟约束(Xilinx版本)2012-02-29 9169

-

例说FPGA连载17:时钟与复位电路设计2016-08-08 10840

-

AD画一个圆形的板子,怎么走线也是大的圆弧2018-12-18 6983

-

FPGA器件的时钟电路2019-04-12 2188

-

请问AD割铜命名走线怎么走圆弧型?2019-09-04 3654

-

FPGA的全局时钟是什么?2021-07-29 1313

-

FPGA中的全局时钟怎么用啊2021-11-01 2233

-

FPGA全局时钟资源相关原语及使用2010-09-10 2654

-

FPGA全局时钟和第二全局时钟资源的使用方法2017-02-11 5515

-

Xilinx全局时钟的使用和DCM模块的使用2017-11-22 12814

-

FPGA架构中的全局时钟资源介绍2021-03-22 15353

-

华为鸿蒙系统未来十年怎么走?2021-06-02 2455

全部0条评论

快来发表一下你的评论吧 !