晶圆背面研磨(Back Grinding)工艺简介

制造/封装

描述

经过前端工艺处理并通过晶圆测试的晶圆将从背面研磨(Back Grinding)开始后端处理。背面研磨是将晶圆背面磨薄的工序,其目的不仅是为了减少晶圆厚度,还在于联结前端和后端工艺以解决前后两个工艺之间出现的问题。半导体芯片(Chip)越薄,就能堆叠(Stacking)更多芯片,集成度也就越高。但集成度越高却可能导致产品性能的下降。所以,集成度和提升产品性能之间就存在矛盾。因此,决定晶圆厚度的研磨(Grinding)方法是降低半导体芯片成本、决定产品质量的关键之一。

1. 背面研磨(Back Grinding)的目的

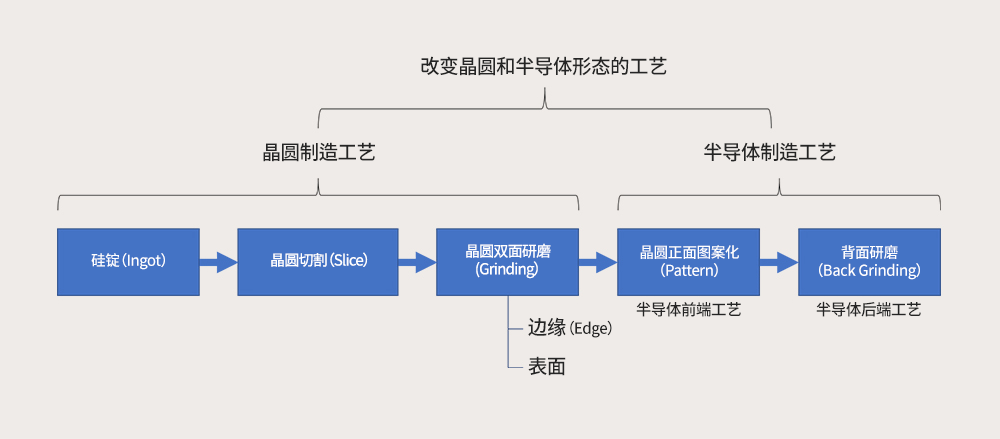

图1. 晶圆制造工艺和半导体制造工艺中的形态变化

在由晶圆制成半导体的过程中,晶圆的外观不断发生变化。首先,在晶圆制造工艺中,晶圆的边缘(Edge)和表面会进行抛光(Polishing),这一过程通常会研磨晶圆的两面。前端工艺结束后,可以开始只研磨晶圆背面的背面研磨工序,能去除在前端工艺中受化学污染的部分,并减薄芯片的厚度,这非常适用于制作搭载于IC卡或移动设备的薄型芯片。此外,这一工序还有减少电阻、降低功耗、增加热导率而迅速散热至晶圆背面的优点。但与此同时,由于晶圆较薄,很容易被外力折断或翘曲,使得处理步骤更加困难。

2. 背面研磨(Back Grinding)详细工艺流程

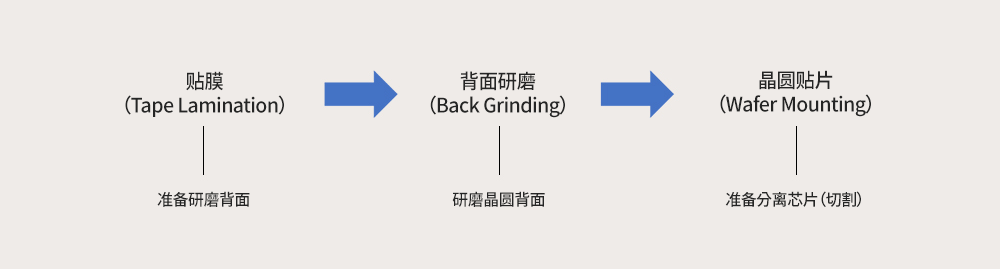

图2. 背面研磨三步骤

背面研磨具体可以分为以下三个步骤:第一、在晶圆上贴上保护胶带贴膜(Tape Lamination);第二、研磨晶圆背面;第三、在将芯片从晶圆中分离出来前,需要将晶圆安置在保护胶带的晶圆贴片(Wafer Mounting)上。晶圆贴片工艺是分离芯片(切割芯片)的准备阶段,因此也可以包含在切割工艺中。近年来,随着芯片越来越薄,工艺顺序也可能发生改变,工艺步骤也愈发精细化。

3. 保护晶圆的贴膜(Tape Lamination)工艺

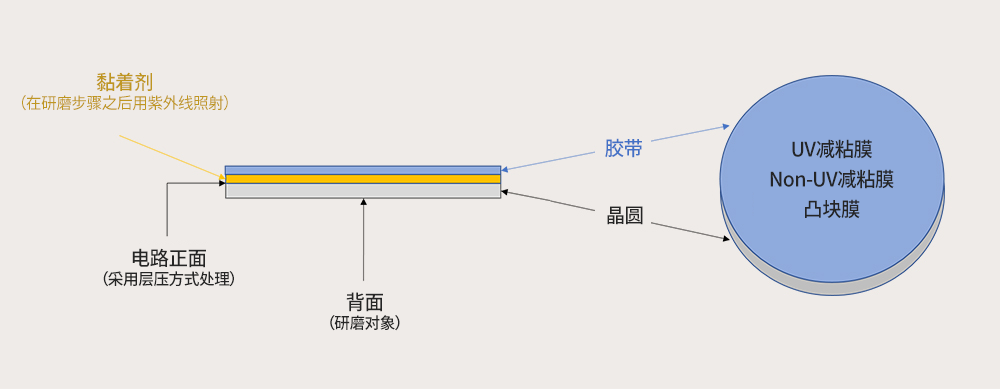

图3. 贴膜工艺和晶圆正面

背面研磨的第一步是贴膜。这是一种将胶带粘到晶圆正面的涂层工艺。进行背面研磨时,硅化合物会向四周扩散,晶圆也可能在这一过程中会因外力而破裂或翘曲,且晶圆面积越大,越容易受到这种现象的影响。因此,在背面研磨之前,需要贴上一条薄薄的紫外线(Ultra Violet, 简称 UV)蓝膜用于保护晶圆。

贴膜时,为了使晶圆和胶带之间没有间隙或气泡,需要提高粘合力。但在背面研磨后,晶圆上的胶带应通过紫外线照射降低粘合力。剥离后,胶带的残留物不得留在晶圆表面。有时,该工艺会使用粘合力较弱且容易产生气泡的非紫外线减粘膜处理,虽然缺点多,但价格低廉。此外,还会用到比UV减粘膜厚两倍的凸块(Bump)膜,预计在未来会有越来越高的使用频率。

4. 晶圆厚度与芯片封装成反比

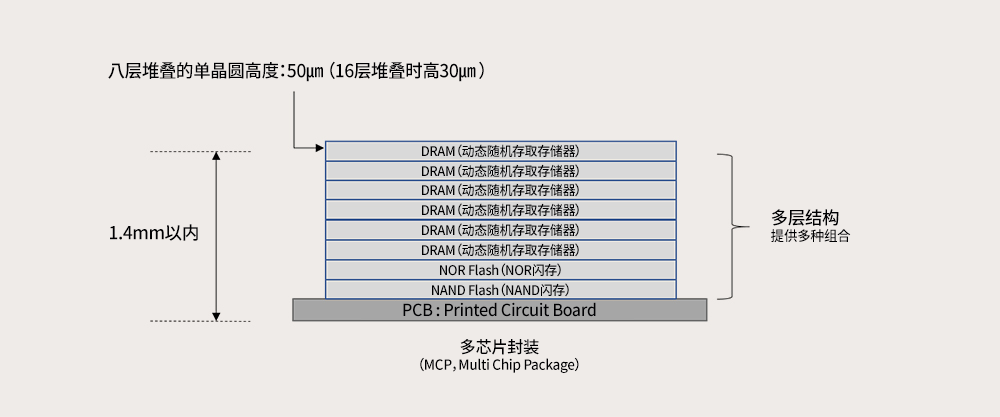

图4. 多芯片封装(MCP,Multi Chip Package)结构

经过背面研磨的晶圆厚度一般会从800-700㎛减少到80-70㎛。减薄到十分之一的晶圆能堆叠四到六层。近来,通过两次研磨的工艺,晶圆甚至可以减薄到大约20㎛,从而堆叠到16到32层,这种多层半导体结构被称为多芯片封装(MCP)。在这种情况下,尽管使用了多层结构,成品封装的总高度不得超过一定厚度,这也是为何始终追求磨得更薄的晶圆。晶圆越薄,缺陷就会越多,下一道工序也越难进行。因此,需要先进的技术改进这一问题。

5. 背面研磨方法的改变

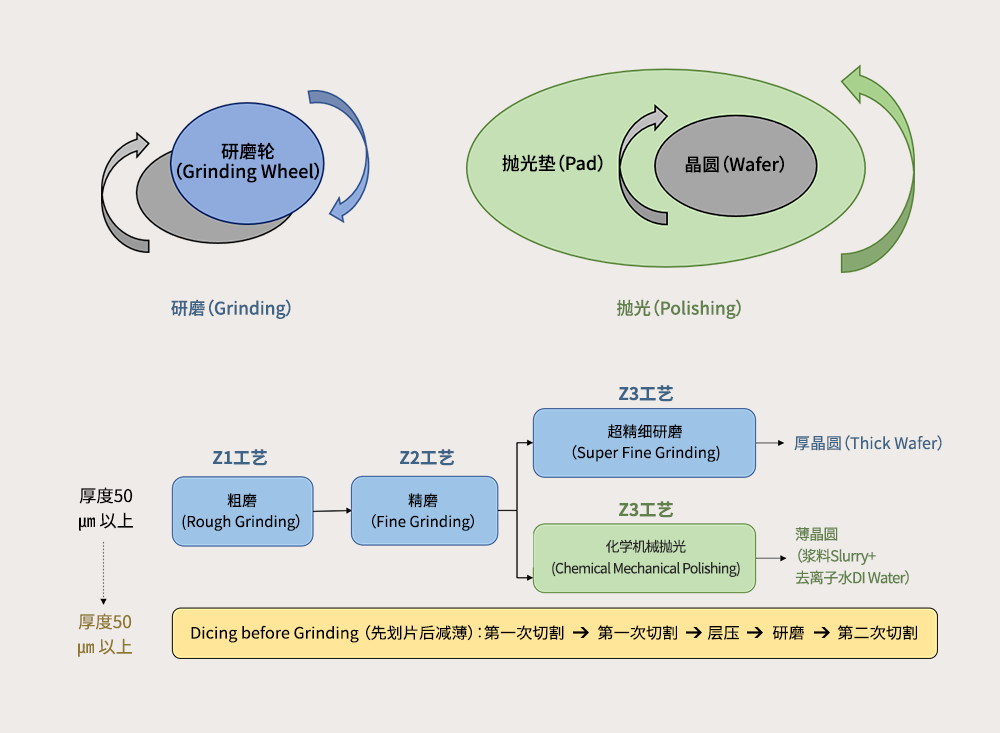

图5. 根据晶圆厚度而不同的研磨方法

通过将晶圆切割得尽可能薄以克服加工技术的局限性,背面研磨技术不断发展。对于常见的厚度大于等于50㎛的晶圆,背面研磨有三个步骤:先是粗磨(Rough Grinding),再是精磨(Fine Grinding),两次研磨后切割并抛光晶圆。此时,类似化学机械抛光(Chemical Mechanical Polishing,简称 CMP)一样,一般会在抛光垫和晶圆之间投入浆料(Slurry)和去离子水(Deionized Water)。这种抛光工作能减少晶圆和抛光垫之间的摩擦,使表面光亮。当晶圆较厚时,可以采用超精细研磨(Super Fine Grinding),但晶圆越薄,就越需要进行抛光。

如果晶圆变得更薄,在切割过程中容易出现外部缺陷。因此,如果晶圆的厚度为50㎛微米或更小,可以改变工艺顺序。此时,会采用先划片后减薄(DBG,Dicing Before Grinding)的方法,即在第一次研磨之前,先将晶圆切割一半。按照划片(Dicing)、研磨和划片的顺序,将芯片从晶圆安全地分离出来。此外,还有使用坚固的玻璃板来防止晶圆破裂的特殊的研磨方法。

随着电器小型化对集成度的要求越来越高,背面研磨技术也应不但克服其局限性,继续发展。同时,不仅要解决晶圆的缺陷问题,还必须为未来工艺可能出现的新问题做好准备。为了解决这些问题,可能需要调换工艺顺序,或引入应用于半导体前端工艺的化学蚀刻技术,全面开发新的加工方法。为了解决大面积晶圆固有的缺陷,正对研磨方法进行多种探索尝试。此外,关于如何回收利用研磨晶圆后产生的硅渣的研究也正在进行。

审核编辑:汤梓红

-

介绍芯片键合(die bonding)工艺2023-03-27 17883

-

晶圆背面研磨(Back Grinding)工艺简介2023-05-22 2833

-

晶圆级封装的工艺流程详解2023-11-13 6817

-

晶圆凸起封装工艺技术简介2011-12-01 5432

-

单片机晶圆制造工艺及设备详解2018-10-15 7169

-

晶圆背面研磨与湿式刻蚀工艺2022-03-23 1892

-

晶圆减薄工艺的主要步骤2022-03-31 6011

-

BGA 封装工艺简介2023-05-23 6056

-

BGA封装及晶圆切割工艺解析2023-06-09 5238

-

晶圆背面涂敷工艺对晶圆的影响2024-12-19 620

-

背金工艺的工艺流程2025-02-12 2869

-

晶圆减薄工艺分为哪几步2025-05-30 2306

-

梯度结构聚氨酯研磨垫的制备及其对晶圆 TTV 均匀性的提升2025-08-04 910

-

聚氨酯研磨垫磨损状态与晶圆 TTV 均匀性的退化机理及预警2025-08-05 1097

全部0条评论

快来发表一下你的评论吧 !