基于DWC2的USB驱动开发-0x04 DWC2 USB2.0 IP 架构介绍

基于DWC2的USB驱动开发-0x04 DWC2 USB2.0 IP 架构介绍

描述

| 嵌入式USB开发 |

| ------------------------------------------------------------------------------------------ |本文转自公众号,欢迎关注

基于DWC2的USB驱动开发-0x04 DWC2 USB2.0 IP 架构介绍 (qq.com)

话说上传图片限制的数量也太小了,后面还有几张图片传不上去没办法只能空着了。

前言

这一篇先对IP的架构进行一些介绍,内容比较多所以重点关注和软件相关的内容。后续编程具体涉及时,可能再返回过来详读某一个部分。

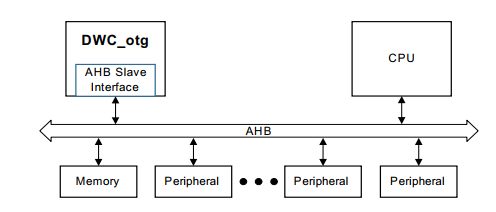

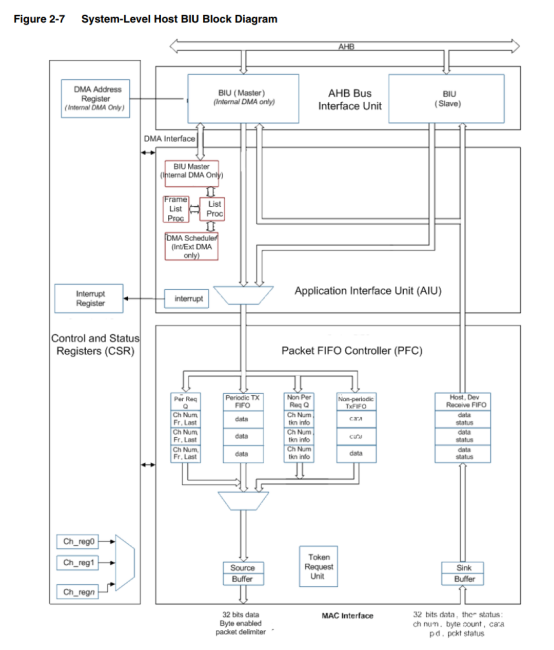

系统级架构

IP可以配置为Slave-Only模式,Internal DMA模式,External模式。如果配置为DMA模式则也支持Slave模式可以软件禁用DMA,而配置为Slave-Only模式则不支持DMA模式。只能在初始化时要么选择DMA要么选择Slave模式,不能动态修改。

Slave-Only模式

该模式可以减少IP的面积,此时需要CPU去执行memory到DWC-otg之间的数据搬运,占用CPU的带宽效率比较低。

此时CPU是AHB的主设备,CPU负责搬运数据。

Internal DMA模式

使用DWC-otg内部的DMA,由其进行memory到DWC-otg之间的数据搬运,不占用CPU的带宽,CPU只需要负责完成中断和错误等处理。

此时内部DMA是AHB的主设备,负责搬运数据。

该模式又分为

Buffer DMA和Scatter/Gather DMA模式两种。

前者一次只能处理一个缓冲区,而后者一次处理一个链表的缓冲区效率更高。

注意使能了内部DMA模式还是可以使用Slave模式的,所以上图由AHB Slave和AHB Master两个接口。而Slave-Only的配置只有AHB Slave接口。

External DMA Controller 模式

类似于内部DMA模式,只是使用的外部的DMA,此时DWC_otg和AHB之间只有AHB Slave接口。

如下图使用的是DW_ahb_dmac的DMA,和DWC_otg之间有一个Gasket中间接口转换。

DW_ahb_dmac也可以换为其他的DMA。

同样使能外部DMA模式还是可以使用Slave模式的。

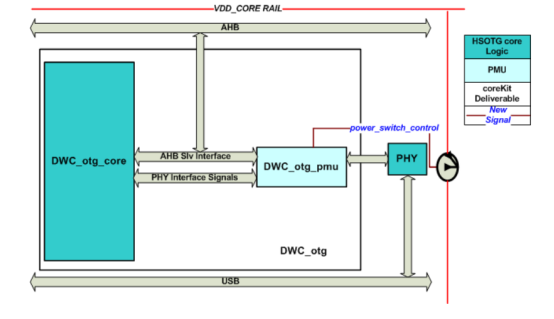

PMU模块

实现以下功能

- 休眠Hibernation:suspend期间完全关闭DWC_otg

支持以下配置:OTG 模式, OTG 和 Non-OTG的主机设备模式。

UTMI+, ULPI, HSIC, IC_USB 和FS 专用接口

内部Buffer DMA

内部Descriptor Based DMA

External DMA

External DMA

- ADP

SPRAM和控制器必须处于同一电源域。

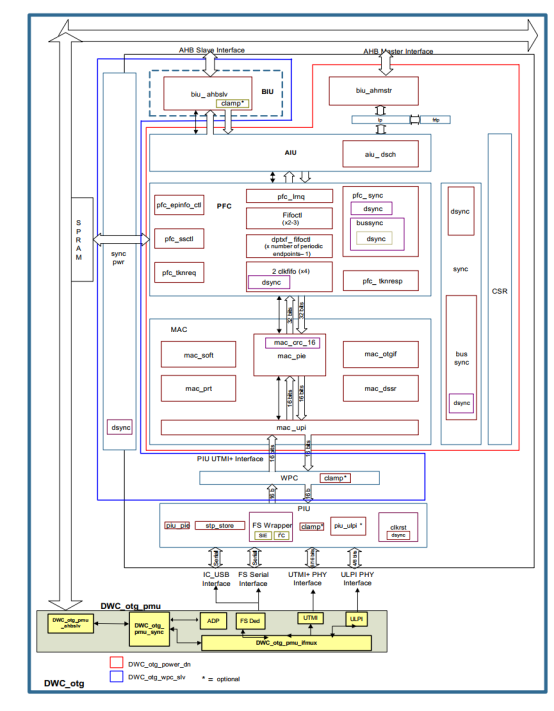

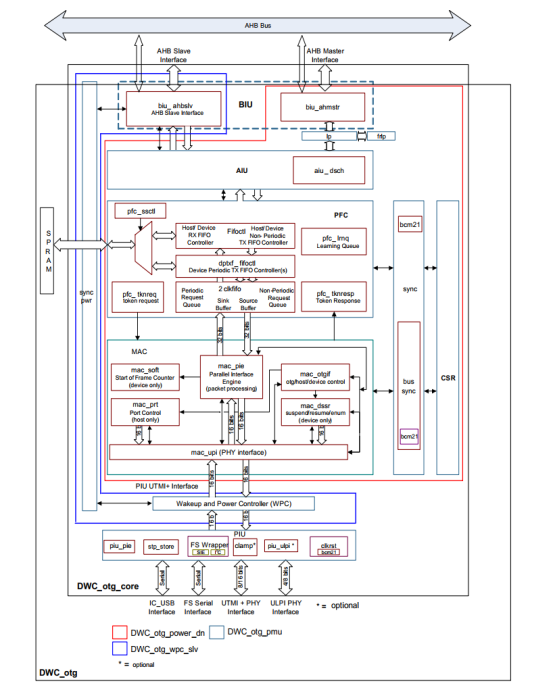

层次结构

框图如下

功能框图

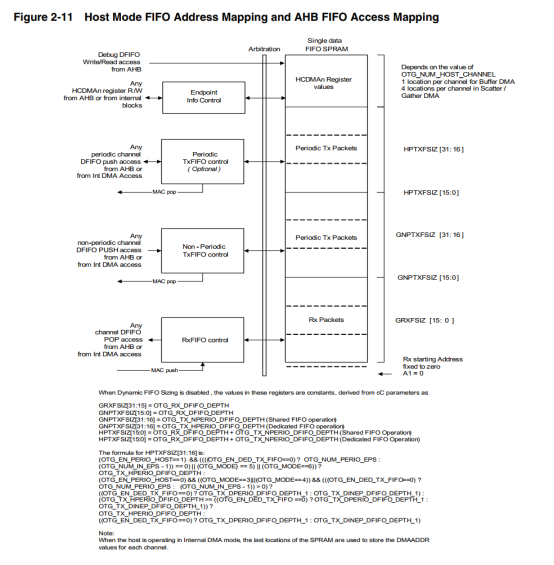

主机架构

主机的非周期OUT传输使用一个发送FIFO

所有的周期OUT传输使用另一个发送FIFO

这些FIFO用于缓存USB的数据包的payload。

主机通过请求队列(一个用于周期性队列,一个用于非周期性队列)传输USB事务。

请求队列中的每个条目都保存in或OUT通道号以及在USB上执行事务的其他信息。

将请求写入队列的顺序决定了USB上的事务顺序。

主机首先处理周期性请求队列,然后在每个(微)帧的开头处理非周期性请求排队。

主机的所有周期和非周期接收到只使用同一个FIFO,用于缓存接收的USB数据包的payload,接收到的每个数据包的状态也进入FIFO,状态条目保存IN信道号以及其他信息,例如接收的字节计数和有效性状态,以在AHB上执行事务。

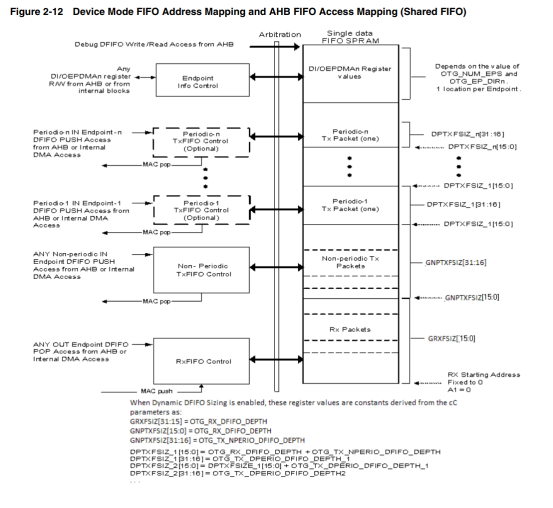

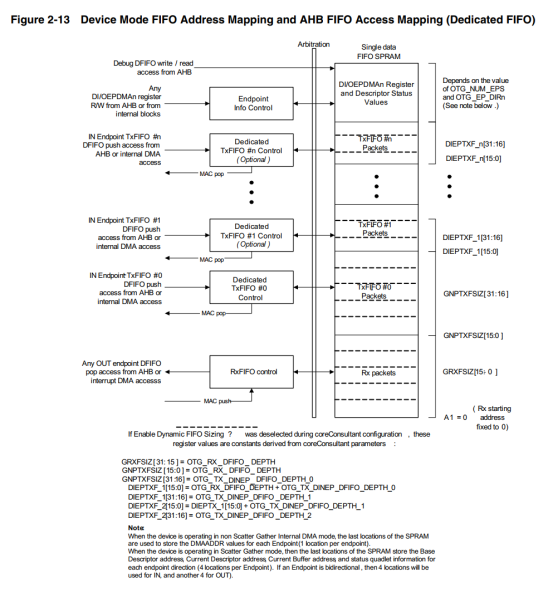

设备架构

发送支持共享缓冲区和独立缓冲区两种方式

由IP配置参数OTG_EN_DED_TX_FIFO配置

Shared Transmit FIFO

配置OTG_EN_DED_TX_FIFO=0为该模式

该方式减少了IP的门数,适用于同一时间只有一个非周期IN端点工作的场景,因为非周期端点只有一个缓冲区。需要软件去管理当前缓冲区给哪个端点使用。并且一旦出现错误软件需要进行处理重新使能端点,这一点需要注意。

注意的是这里是非周期端点公用一个发送缓冲区,对于非周期端点需要管理当前给哪一个端点使用。对于周期端点还是每一个周期端点独享一个发送缓冲区的。

FIFO由DMA或者由CPU写入数据。在收到IN令牌后硬件自动从FIFO中搬运数据到USB总线中去。

设备模式周期FIFO(FIFO-1),和主机模式周期FIFO (PTxF 1)共用。根据实际周期IN个数后面使用FIFOs 2 到 n。

Dedicated Transmit FIFO

配置OTG_EN_DED_TX_FIFO = 1

不需要处理FIFO的错误。

FIFOs 2 到 n给所有IN端点使用,不管是周期还是非周期端点每个都独立使用一个,和Shared模式只有周期端点才独立拥有FIFO不一样。

当选择DMA模式时,控制器还支持发送和接收方向上的阈值设置,此时FIFO可以设置为小于一个USB包的大小。

阈值设置:

支持同步和非同步发送阈值分别使能;

支持AHB 和MAC传输设置两种阈值值。

控制器自动管理溢出,发送下溢时,即控制器想要从FIFO中取数据发送时发现没有数据可取产生下溢出underrun,此时会反转CRC值使得其变为错误数据包。

而在接收上溢时overflow,接接收到USB数据往FIFO里写时发现FIFO满了,此时自动产生NAK,并且指针绕回。所以最好设置FIFO是两倍阈值大小,进行ping-pang。

Single Receive FIFO

以上介绍的是发送FIFO,对于接收FIFO只有一个。即所有OUT端点都是使用一个FIFO。

接收FIFO保存接收数据包的状态,例如字节计数、数据PID和接收数据的有效性。

DMA或CPU在接收数据时从接收FIFO中读取数据。

DWC_otg_core

使能 Dynamic FIFO Sizing时可以动态修改FIFO的大小。

AHB总线接口单元BIU

即AHB总线接口单元

主机模式

设备模式

分为AHB主和AHB从接口。

AHB从总线接口单元 (BIUS)

AHB从接口单元将AHB cycles转换为CSR写入/读取、数据FIFO读取/写入和DFIFO push/pop信号。DFIFO读/写访问仅用于测试目的。

完全兼容AMBA 2.0-Compliant AHB Slave

支持INCR4, INCR8, INCR16, INCR 和 SINGLE

支持忙和提前终止

CSR和DFIFO读取/写入必须始终为32位;8位和16位写访问将未知值写入DFIFO。

仅生成OK响应

不生成SPLIT、RETRY或ERROR响应

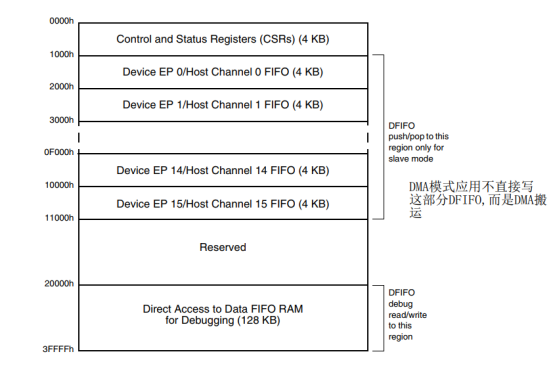

站在CPU软件角度,作为AHB主,可以看到如下地址空间

CSR寄存器部分

DFIFO部分,Slave模式CPU直接访问,DMA模式由DMA复制和系统memory之间搬运数据。

还有最后一部分用于调试的直接访问DFIFO地址空间

注意在SPRAM中还会存储一些寄存器信息

Scatter/Gather DMA模式每个端点需要占用4x35位的空间(SRAM中WORD单位是35位的,因为要存其他信息),

DMA 和 Slave模式,每个端点占用1x35位空间。

以上每个4k空间对应一个端点的FIFO数据。

读这些4k空间实际就是读RXFIFO

写设备的非周期IN端点和主机的非周期OUT通道对应TxFIFO

主机模式写任意周期OUT通道也是写公用的TxFIFO

在设备模式访问周期IN端点或者Dedicated FIFO模式的所有IN端点映射到对应的周期 (Dedicated FIFO的周期或非周期 ) Tx FIFO。设备端点控制寄存器的位30:27将端点映射到特定周期FIFO。

Shared FIFO模式IN INTERRUPT可以映射到Non-periodic Tx FIFO或者单独的Periodic Tx FIFO。

SRAM映射

AHB主总线接口单元 (BIUM)

即控制器deDMA作为AHB主,负责控制器内部RAM和系统memory之间搬运数据。

完全兼容AMBA 2.0-compliant AHB Master

支持burst类型:SINGLE, INCR, INC4, INC8,和 INC8

选择INC4, INC8, 或 INC16 时可能使用SINGLE 和 INCR

剩余长度不足burst长度,SPLIT后的数据传输,RETRY后的数据传输时使用INCR

处理AHB拆分、RETRY、ERROR条件和提前终止

应用程序需要时可插入BUSY cycle

处理AHB 1KB边界

AHB传输数据地址总线都是32位对齐,控制器可以传输2字节和1字节。

控制和状态寄存器CSR

软件的角度需要注意

寄存器PCGCCTL和GINTSTS的b[31:29]不位于AHB时钟域,所以 Power Down模式这些寄存器还是有效的。

主机和从机共享寄存器地址节省空间,但是如果入籍模式访问设备寄存器或者反之则会产生GINTSTS.ModeMis中断。

应用接口单元AIU

包括AHB主,AHB哦那个 包FIFO控制,CSR

包括DMA调度DSCH等功能

包FIFO控制器PFC

实现USB数据包的管理,以及包到内部SRAM的传输等。

需要注意下在SPRAM的最后,有一个EPINFO_CTL用于管理端点的信息。

MAC

该模块处理USB传输,设别,主机,OTG的协议才是真正的核心部分。

PHY接口单元PIU

支持不同的PHY接口

唤醒和功耗控制WPC

用于Suspend唤醒管理等

链表处理器

实现Descriptor-Based Scatter/Gather DMA的处理

电源管理单元架构

DWC_otg_pmu模块支持休眠,

包括

- PMU Slave,支持CPU通过AHB控制PMU的逻辑,即作为AHB的从接口。即访问寄存器GPWRDN。

- PMU Logic模块,实现不同PHY类型的唤醒逻辑。

UTMI+ 和HSIC 接口

IC_USB 和 FS专用接口

ULPI接口

控制器休眠时驱动PHY接口信号,

为DWC_otg_pmu_ifmux模块解码lineestate

- PMU IfMux 模块 该模块实现多路line_state复用,检测line_state改变,多路复用不同接口的状态,检测状态的改变,OTG Revision 2.0 和 OTG Revision 1.3 SRP的检测。

- PMU Sync 模块 用于同步DWC_otg_pmu_ahb_slv和PMU接口逻辑的时钟域信号。

- ADP模块 支持ADP:Attach Detection Protocol探测和活动感知,需要IP配置OTG_ADP_SUPPORT=1

对于软件来说其细节可以稍微看一下即可。

需要注意有几个寄存器是位于pmu域的:

GPWRDN

系统时钟和复位

DWC_otg有以下输入时钟

Hclk:AHB域的时钟。

Pmu_hclk:PMU域的时钟,休眠和/或ADP 时使用。

utmi_clk:选择UTMI PHY时使用。

ulpi_clk:选择ULPI PHY时使用。ULPI使用DDR模式时 负边沿也使用。

utmifs_clk48: OTG_FSPHY_INTERFACE != 0时才有。

ref_clk:OTG_SERV_INT_ENH使能时才有。

DWC_otg_clkrst模块还会产生以下输出时钟

phy_clk: 受门控,从ULPI, UTMI+, USB 1.1 FS 时钟, USB 1.1FS 时钟/8 中选择。

wpc_clk:不受门控,OTG_EN_PWROPT不为0时才有。从ULPI, UTMI+, USB 1.1 FS 时钟中选择。

hclk_gated: OTG_EN_PWROPT不为0才有,hclk门控后的输出,以优化功耗。

utmifs_clk6:ULPI, UTMI+, 或 USB 1.1 FS 时钟/8,USB 1.1 FS Serial Transceiver 接口使能才有。

系统时钟速度配置如下

系统时钟对最小包间间隙和设备支持的级联集线器数量的影响

当DWC_otg控制器充当设备时,根据UTMI规范,对于接收后紧接着的接收,有最坏情况下的响应时间。这种最坏情况下的响应时间取决于AHB时钟频率。AHB时钟快处理的快,这个时间就小。

控制器寄存器在AHB域中,并且在更新这些寄存器值之前,控制器不接受另一个令牌。

当AHB时钟与PHY时钟相同时,此最坏情况值为七个PHY时钟。当AHB时钟较快时,该值较小。

以下场景可能产生接收后紧接着接收的情况:

- 来自主机的任何响应令牌(ACK/NAK/NYET/STALL),后跟一个令牌。

- 作为一种特殊情况,ISOC OUT数据包,后面紧跟着下一个令牌。

系统级影响

在系统级别,上述这种限制可能会降低设备控制器的性能,因为当令牌太靠近前面的ISOC OUT令牌的末尾时,控制器会丢弃或向主机发送NAK。

对于批量、中断和控制事务,系统会随着主机重试令牌而恢复,事务最终会完成。

而对于等时ISO事务,因为没有重发机制,主机进行到为间隔bInterval安排的下一个事务。

在以下情况下会出现显著的性能下降:

该设备连接到一个主机,该主机能够在88-96位时间内一致地发送令牌,也就是说,从前面的ISOC OUT令牌结束算起,有六到七个PHY时钟

该设备通过多层集线器连接到主机,使得ISOC OUT令牌和后续令牌之间的数据包间间隙缩小到小于七个PHY时钟

但是,在这两种情况下,系统都不会停止响应或进入不可恢复状态,只会影响性能。

此时控制器的行为

以下是ISOC OUT Token紧接着下一个Token时的控制器信号

(缺图)

- 在PHY时钟域 (PCLK) 处理ISOC OUT token。

- 更新AHB时钟(HCLK)域中的相关寄存器。

- 在处理UTMI接口上接收的下一个令牌之前,等待从AHB时钟域到PHY时钟域的完成握手。

- ti_trans_done信号是在PHY时钟域中生成的用于更新AHB时钟域寄存器的触发信号。控制器等待来自AHB时钟域的握手,以便此寄存器更新接受下一个令牌

- sh2pt_reg_vld信号是来自AHB时钟域的握手信号,其指示寄存器更新在AHB时钟域中完成。

- txrx_state信号在将接收到的数据推送到RxFIFO时处于RCVD_DATA状态,在计算CRC时处于CHKCRC16状态,以及在推送包的接收状态时处于DATA_to_STS状态。

- 在解码接收到的令牌时,tkn_state信号处于tkn_DECODE状态

M5-M3:RX开始延迟,DP/DM线上SYNC域的第一位与RXACTIVE有效之间的时间。

M2-M1:RX结束延迟,EOP的最后一位和RXACTIVE无效之间的时间

M3-M1:在DP/DM线路上测量的RX到RX数据包间延迟

M4-M2:

对于16位UTMI模式:从rx_active无效到CRC计算的一个PHY时钟周期

对于8位UTMI模式:从rx_active无效到CRC计算的三个PHY时钟周期

从RXACTIVE无效到txrx_state之间的时间为CHK_CRC16

M5-M4:接收数据包状态推送的三个PHY时钟周期,DATA_TO_STS状态下txrx_state信号所用的时间.

M6-M5:寄存器更新触发脉冲同步延迟+寄存器更新tog脉冲握手同步延迟。ti_trans_done信号切换到sh2pt_reg_vld脉冲之间的时间。

M6-M5:在PIE接收和解码令牌的七个PHY时钟周期。RXACTIVE有效和tkn_state之间的时间为tkn_END。

计算所需的最低AHB时钟频率

为了计算克服ISOC OUT包间间隙限制所需的最小AHB时钟频率,需要确定控制器完成以下两个过程所需的时间:

接收到ISOC OUT令牌后,更新AHB时钟域中的控制器寄存器

解码下一个接收到的令牌

为了克服这一限制,使得控制器不会丢弃在ISOC OUT令牌之后太近接收到的任何令牌

更新AHB时钟域中的控制器寄存器所需的时间应该小于或等于解码下一个接收到的令牌所需的时刻。此条件构成计算所需最小AHB时钟频率的基础。

给定UTMI PHY 位宽和最小包见间隙,下表列出了AHB 为了满足不丢弃任何包必须达到的最小频率。

(缺图)

对于32 HS bit 时间间隙,UTMI8位宽时,最少要96-MHz HCLK。

系统时钟对设备支持的级联集线器数量的影响

(缺图)

对于在多层集线器上使用等时OUT端点的设备,建议使用8位UTMI模式和96MHz或更高的AHB时钟频率。

系统时钟和复位产生

有两个外部复位输入,复位是软件初始化时需要做的。

hreset_n: hclk 和pmu_hclk域复位

prst_n: phy_clk 域复位

DWC_otg控制器的所有输入复位都可以异步复位,但解除复位必须与配置中选择的时钟同步。

每当软件在重置后更改PHY选择位(USB 1.1 FS收发器、UTMI+或ULPI)时,它必须复位软件重置,因为PHY部分位会更改PHY接口单元的时钟。

USB 1.1 FS收发器接口

发送数据

(缺图)

接收数据

(缺图)

支持Micro-AB 插座的嵌入式主机

IP参数配置OTG_MODE=0,1, 或者 5支持该功能.

在不支持SRP的配置中,需要外部逻辑来基于ID值控制PHY DRVVBUS,因为控制器内部不含OTG状态机,并且PHY DRVBUS没有连接到DWC_OTG控制器。

在这种配置为了支持Micro-AB插座,当ID对应于主机时, DRVVBUS必须asserted,当ID对应于设备时,必须de-asserted。

为了在控制器充当嵌入式主机时启用Micro-AB 插座支持,utmiotg_idig输入信号也仅存在于支持SRP的主机模式(OTG_mode=5)中。如果嵌入式主机仅支持标准A连接器,则将DWC_otg控制器的utmiotg_idig输入信号线硬连接到零。

总结

以上从整体框架上去了解了IP,先不必要全部理解,内容很多大概知道框架即可,后面编程有需要再回过头来参考。

审核编辑 黄宇

-

新思 DWC2 的参考手册从哪里可以下载2025-01-22 10577

-

基于DWC2的USB驱动开发-数据不能发送问题分析案例2023-08-08 5051

-

基于DWC2的USB驱动开发-抽丝剥茧再论切换到状态阶段标志DOEPINTn.StsPhseRcvd2023-07-24 4221

-

基于DWC2的USB驱动开发-设备类驱动框架2023-07-16 3025

-

基于DWC2的USB驱动开发-高速设备枚举为全速设备问题案例分析2023-07-10 2956

-

基于DWC2的USB驱动开发-USB连接详解2023-07-07 5777

-

基于DWC2的USB驱动开发-IAD描述符详解2023-06-27 494860

-

基于DWC2的USB驱动开发-0x07 DWC2 USB2.0 IP 配置参数2023-05-17 4634

-

基于DWC2的USB驱动开发-0x02 DWC2 USB2.0 IP功能特征介绍2023-05-09 14756

-

基于DWC2的USB驱动开发-0x01开篇介绍与新思DWC2 USB2.0控制器简介2023-05-08 6955

-

无法让USB主机正常工作是我做错了什么吗?2022-12-02 929

-

如何对基于hal库的DWC2 USB IP进行调试呢2022-06-14 1296

-

RK3399平台上USB控制器和PHY的连接方式和配置说明2022-05-12 8562

全部0条评论

快来发表一下你的评论吧 !