基于FPGA的半加器设计

描述

数电基础

加法器用于两个数或者多个数的加和,加法器又分为半加器(half adder)和全加器(full adder)。半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。而全加器除了加数和被加数之和外还要加上上一级传进来的进位信号。如果没有理解,看真值表和逻辑式就理解了。

| A | B | C | S | A+B={C,S} |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | S=A⊕B |

| 0 | 1 | 0 | 1 | C=AB |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 |

| A | B | Ci-1 | Ci | S | A+B+Ci-1={Ci,S} |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | |

| 0 | 1 | 0 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 1 | 1 |

全加器可看作两个半加器和一个或门组成。

设计规划

本例中我们实现最简单的半加器。这个示例中,采用两个按键作为信号输入A和B,两个LED灯作为输出C和S。按下按键为低电平,LED灯为低电平时点亮。需要实现的功能是,按下AB时CS点亮,按下其中一个时只有C点亮,都不按下时只有S点亮。

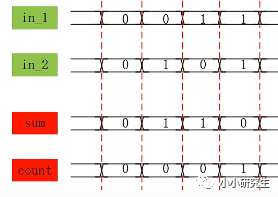

根据真值表很容易画出波形。

编写代码

module half_adder

(

input wire in1 ,

input wire in2 ,

output wire sum ,

output wire cout

);

assign {cout, sum} = in1 + in2;

endmodule

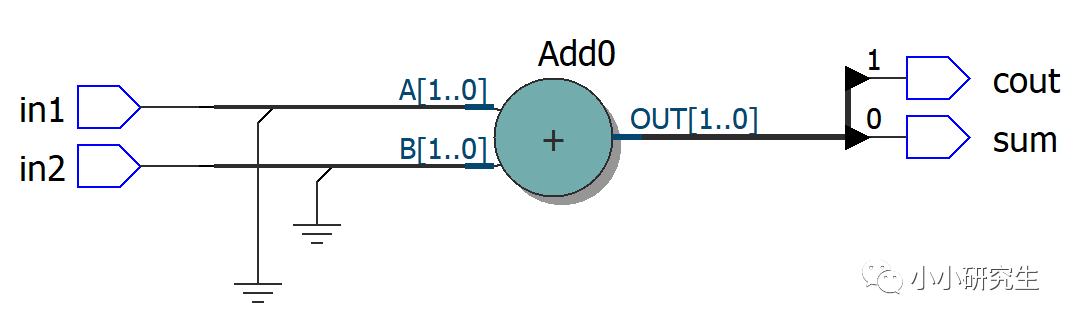

添加.v文件后编译通过。点击RTL viewer可以查看设计的硬件电路结构,和我们设计所表达的意思相同。

编写testbench

`timescale 1ns/1ns

module tb_half_adder();

reg in1;

reg in2;

wire sum;

wire cout;

initial begin

in1 <= 1'b0;

in2 <= 1'b0;

end

always #10 in1 <= {$random} % 2;

always #10 in2 <= {$random} % 2;

//--------------------half_adder_inst-----------------

half_adder half_adder_inst

(

.in1 (in1 ), //input in1

.in2 (in2 ), //input in2

.sum (sum ), //output sum

.cout (cout ) //output cout

);

endmodule

又是超级熟悉的testbench。

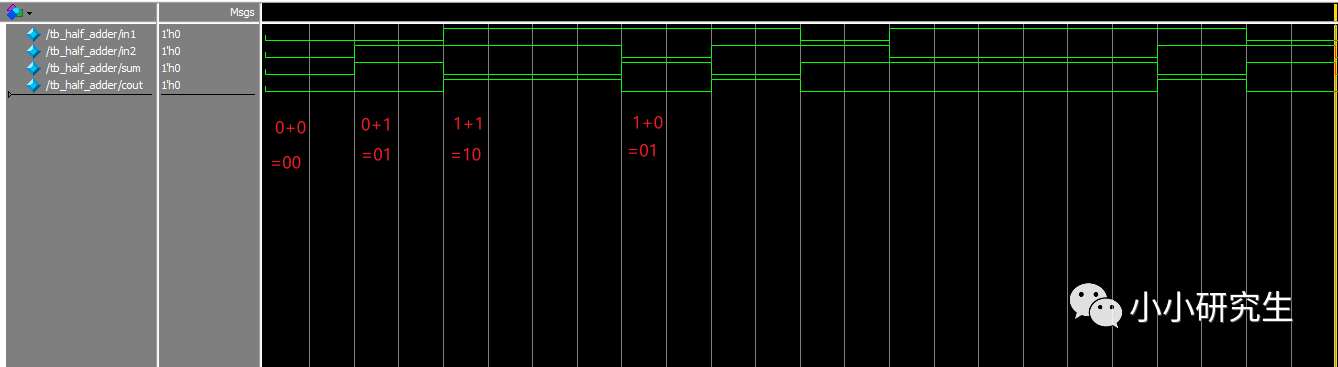

对比波形

波形与预想的一致。

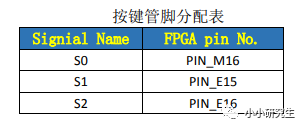

分配管脚

按照设计规划:采用S0和S1作为信号输入A和B,LED0和LED1作为输出C和S。按下AB(0+0)时CS(=00)都亮,按下其中一个(0+1)时只有C(01)亮,都不按下(1+1)时只有S(=10)亮。

全编译后上板验证

都不按时LED1亮

任意按一个时,LED0亮。

两个都按下时,LED0和LED1都亮。

在完成这几个实例的过程中,遇到了很多错误,但是只要会上网,把报错信息进行检索,都能圆满解决。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#硬声创作季 FPGA技术应用:半加器设计Mr_haohao 2022-10-19

-

基于CPLD/FPGA的半整数分频器设计方案2021-06-17 1150

-

FPGA常用运算模块-乘加器2023-05-22 3197

全部0条评论

快来发表一下你的评论吧 !