电容的特征阻抗曲线的了解

电子说

描述

电容的阻抗频率曲线,对于我们电磁兼容的电子电子设计,以及EMC整改都是有着巨大的意义。如果,理解不了电容的阻抗特性,那么,我们在做EMC的时候,就可能陷入巨坑。

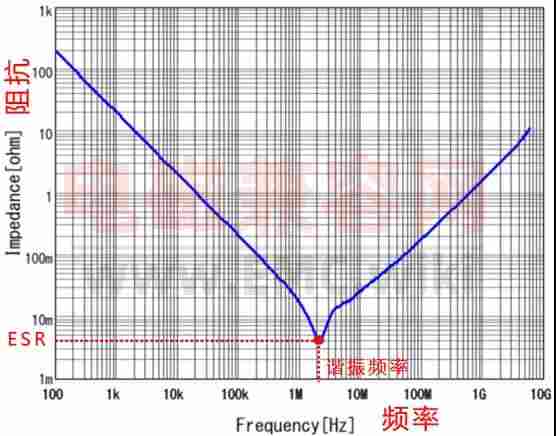

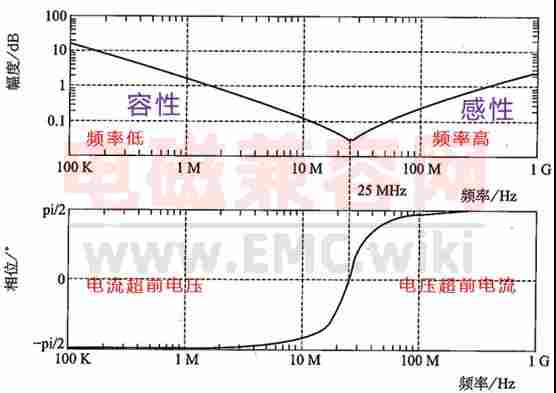

电容阻抗-频率曲线图

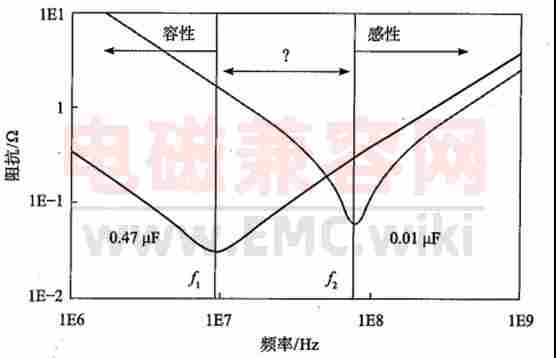

上图是一个典型的电容的阻抗频率曲线图,为什么说它非常重要呢?首先它非常直观,横轴上是频率,纵轴是阻抗,我们能很清楚的看出在各个频率点上,电容的总阻抗是多少。也能知道它在哪个频率点上谐振, ESR是多少。而这些内容,都是我们在选择电容时所必须要了解的。

曲线图的来源

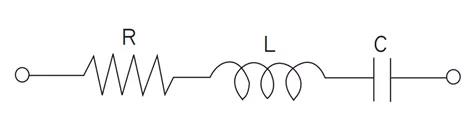

那么,电容曲线图为什么是这样的呢?这是因为电容都不是理想的,它会存在寄生参数,可用简化模型表示。

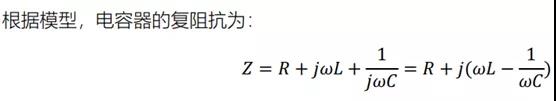

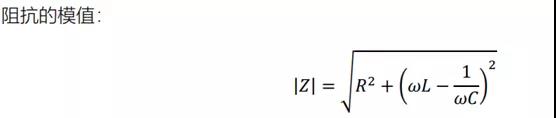

ESR是等效串联电阻,ESL是等效串联电感,C为理想电容。因此实际电容的阻抗可以用数学公式表示

我们画出这个公式的曲线,就得到一个曲线图。

在频率很低的时候,可以看到,感抗远小于容抗,并且复阻抗的相位为负值,说明电流超前电压,这是典型的电容充电特性,所以说,电容在低频主要表现为容性。

而在高频的时候,感抗远大于容抗,复阻抗的相位为正值,说明电压超前电流,是典型的电感施加电压时的行为特征,所以说,电容在高频时表现为电感特性。

而在谐振时,容抗和感抗相抵为0,此时电容的总阻抗最小,复阻抗相位为0,表现为纯电阻特性,这个点就是电容的自谐振频率。在谐振频率左边,电容主要呈容性,在谐振频率右边,电容主要呈感性。

滤波电容如何选择

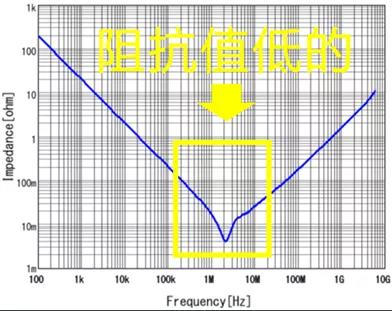

电容最广泛的用途就是滤波,那么如何看曲线选电容呢?其实就是选阻抗最低的。

我们知道,整个阻抗曲线呈大V型,只有在谐振频率点附近的阻抗才比较低。所以,实际的去耦电容都有一定的工作频率范围,只有在谐振频率附近,电容才有很好的去耦作用。

可能有人会觉得,在频率比谐振频率高一点的时候,电容都成感性了,都不是电容了,所以不能让噪声的频率大于电容的谐振频率。其实这是错误的,去耦就是要选阻抗低的,阻抗低,在电容上产生的电压波动就小,也就是噪声会小。

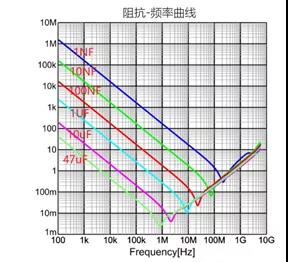

常规的MLCC陶瓷电容的曲线图

来看下常规的MLCC陶瓷电容的曲线图。可以看出,不同的电容,曲线是不同的,容量大的ESR要小写,谐振频率低些,主要滤低频。容量小的ESR要大些,谐振频率要高些,主要滤高频。

两种方式组合滤波

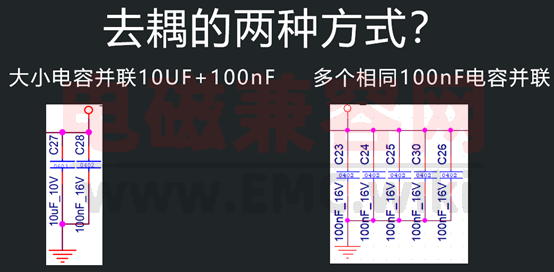

实际电路中我们需要去耦的频率范围会比较宽,因此呢一个电容搞不定,那怎么办呢?我们经常有两种方法来解决,一种是使用一个大电容和一个小电容并联,还有一种是使用多个相同的电容并联。那么这两种方法达到的效果分别是怎样的呢?

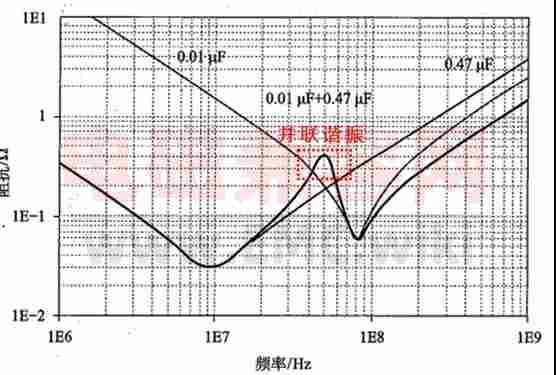

首先来看大小电容并联。大小两个电容分别有各自的谐振频率f1和f2。

当频率比较低的时候,两个电容都成容性,在频率比较高的时候,两个电容都呈感性,并联后总体阻抗曲线都会保持原来的变化趋势,因此,数值上会比任意一个电容都小。

但是,当频率大于f1并小于f2时,大电容呈感性小电容呈容性,两者并联,就像是一个电感和一个电容并联,构成了LC并联谐振电路,并在某一个频率点发生并联谐振,导致该处阻抗很大。如果负载芯片的电流需求正好落在这个频率,那么会导致电压波动超标。所以,我们需要选好电容的搭配情况。

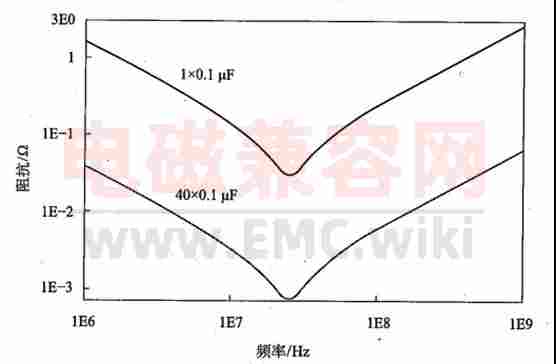

再来看看相同电容并联的情况,n个相同的电容并联,谐振频率和单个电容一样,但是在谐振点处的阻抗是原来的n分之一,因此,多个相同的电容并联后,阻抗曲线整体形状不变,但是各个频点的整体阻抗变小。

有需要做整改的朋友可以私信我!

审核编辑:汤梓红

-

阻抗或者导纳特性曲线若干问2017-09-05 6325

-

6678硬件系统特征阻抗设计2018-06-21 3234

-

PCB特征与PDN性能的关系2018-09-19 4359

-

特征阻抗简介2019-05-30 1831

-

高速信号线的特征阻抗2019-06-14 2994

-

基于UG 平台的截面特征曲线全局约束优化研究2010-02-22 1025

-

扬声器阻抗曲线和低频特性2011-02-21 2355

-

特征阻抗的计算方法2017-06-09 3030

-

特征阻抗的深度解析2020-07-06 4695

-

电容的阻抗频率曲线理解2020-09-21 49527

-

电感阻抗频率曲线_Matlab绘制电感曲线实验2020-10-28 14925

-

电感的阻抗—频率曲线的详细说明2020-12-24 6470

-

LOTO示波器如何测试阻抗的频响曲线2023-05-17 1985

-

电阻、阻抗和特征阻抗的区别是什么?2023-09-20 4658

-

贴片磁珠的阻抗频率曲线如何解读?2025-03-13 1353

全部0条评论

快来发表一下你的评论吧 !