讲讲关于IIC通讯协议的基础知识

电子说

描述

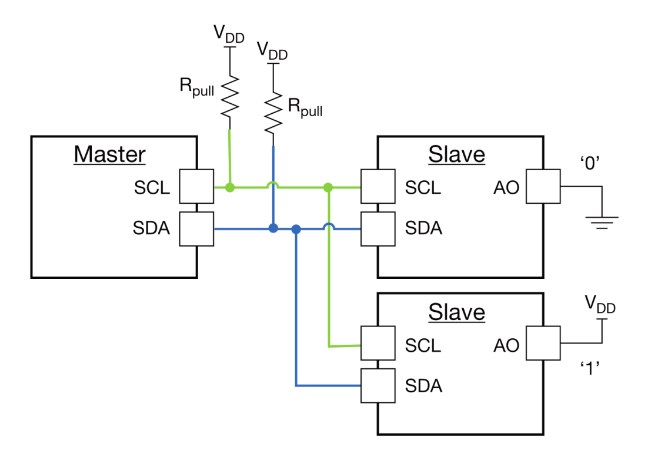

IIC(Inter-Integrated Circuit)的硬件连接

1 对于IIC主机总线上是可以挂1个或者多个从机设备。

2 每个从机是通过其各自的地址来识别。

IIC的数据和控制线(SDA和SCL)

1 SCL(Serial clock),时钟线,用于同步数据传输时序,是一个方波,由主机来驱动,其决定了数据传输的快慢。

2 SDA(Serial data),数据线,用于传输数据,

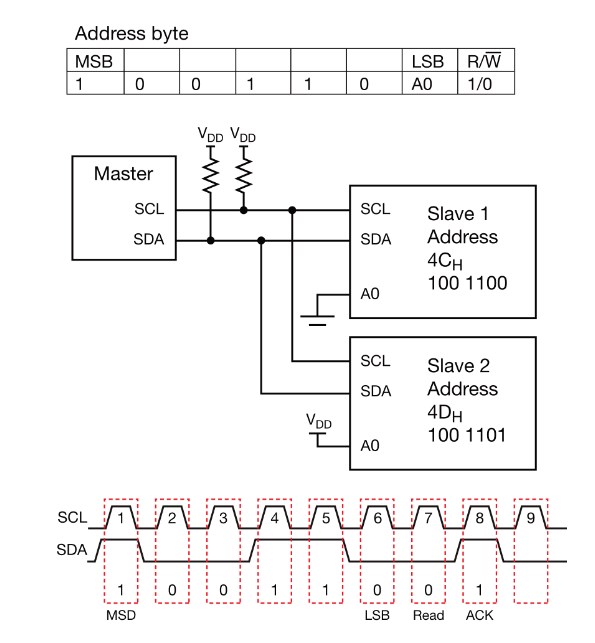

IIC寻址

1 通常对于一个7bit的地址,包含1个额外的读写位。

2 对于IIC总线上的每一个设备都有一个独立的地址。

3 重复的地址会导致通讯错误。

4 对于一些设备会有PIN管脚用来配置不同的IIC地址。

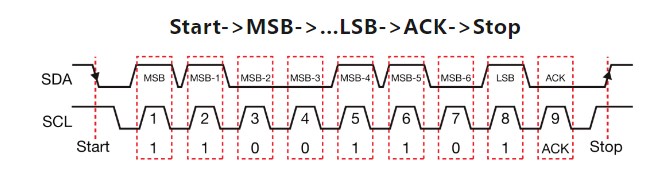

IIC通讯

START,起始位,由主机初始化,SCL高的时候拉低SDA。

STOP,停止位,SCL高的时候,主机释放SDA PIN脚。

ACK(acknowledge),每一次传输一个单字节或者8bits之后,会跟一个SCL的脉冲,这个acknowledge信号是从机应答主机的信号,表示ACK信号之前的那个字节通讯是成功的。

如下是一个标准的IIC写时序:

Start->MSB->…LSB->ACK->Stop

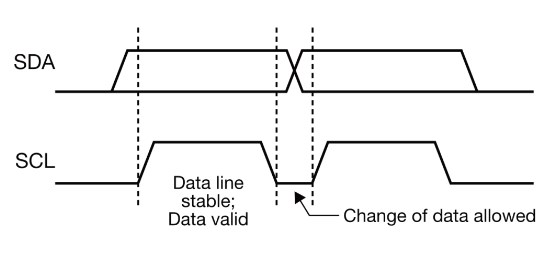

对于有效数据传输:

1 在时钟信号SCL为高的整个脉宽内SDA必须保持稳定。

2 只有在SCL脉冲为低的时候,SDA才被允许高低切换,如果SDA在SCL为高的时候变化,则会被认为是Start/Stop。

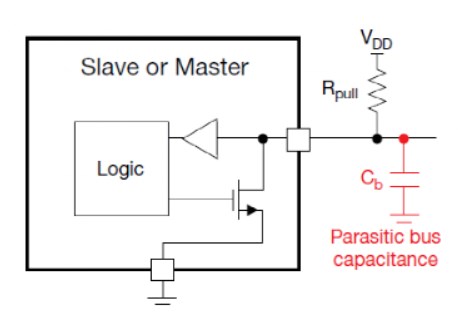

IIC的电路设计

1 对于3.4Mbps速率以下的IIC,是漏极开路(Open Drain)的结构,此时需要外部上拉电阻,上拉电阻的选择需要考虑上拉之后的rise/fall的时间是否满足其时序要求同时也需要考虑功耗。上拉电阻越大,功耗越小,但rise/fall时间越长,会影响通讯;上拉电阻越小,功耗越大,但rise/fall时间短,会降低通讯的误码率。

2 对于3.4Mbps速率以上的IIC,其是推挽(Push Pull)的结构,其rise/fall的时间就完全取决于主机/从机设备内部的push/pull的能力。需要注意的是,不同设备之间的通讯需要选择同样结构的IIC。

-

关于MOS管的基础知识2023-05-23 2465

-

嵌入式网络协议栈基础知识2021-08-03 1831

-

介绍嵌入式网络协议栈基础知识2021-08-04 1616

-

CAN协议基础知识2021-08-19 1631

-

IIC通讯协议2021-08-23 1200

-

STM32 IIC和USART接口的基础知识点汇总,绝对实用2022-02-22 1872

-

网络协议基础知识2010-03-29 940

-

LESSON8_IIC总线协议2016-06-17 1067

-

TCP协议基础知识2017-10-16 4375

-

FPGA基础知识之IIC协议读写解析2018-05-05 9004

-

通讯网络天线基础知识2022-02-15 1359

-

振弦采集模块的通讯协议( IIC)2022-11-17 1503

-

关于mos管的基础知识2023-01-29 6068

-

IIC通讯协议的电路设计2023-04-19 3219

-

SPI协议基础知识2023-11-16 434

全部0条评论

快来发表一下你的评论吧 !