FPGA中Bank和Clock Region之前有什么关系?

描述

前言:从今天开始,我们会定期整理FPGA交流群(包括其他FPGA博主的群)里面有价值的问题,并汇总成文章,如果问题多的话就每周整理一期,如果问题少就每两周整理一期,一方面是希望能帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。

Q:FPGA中的Bank和Clock Region有什么关系?

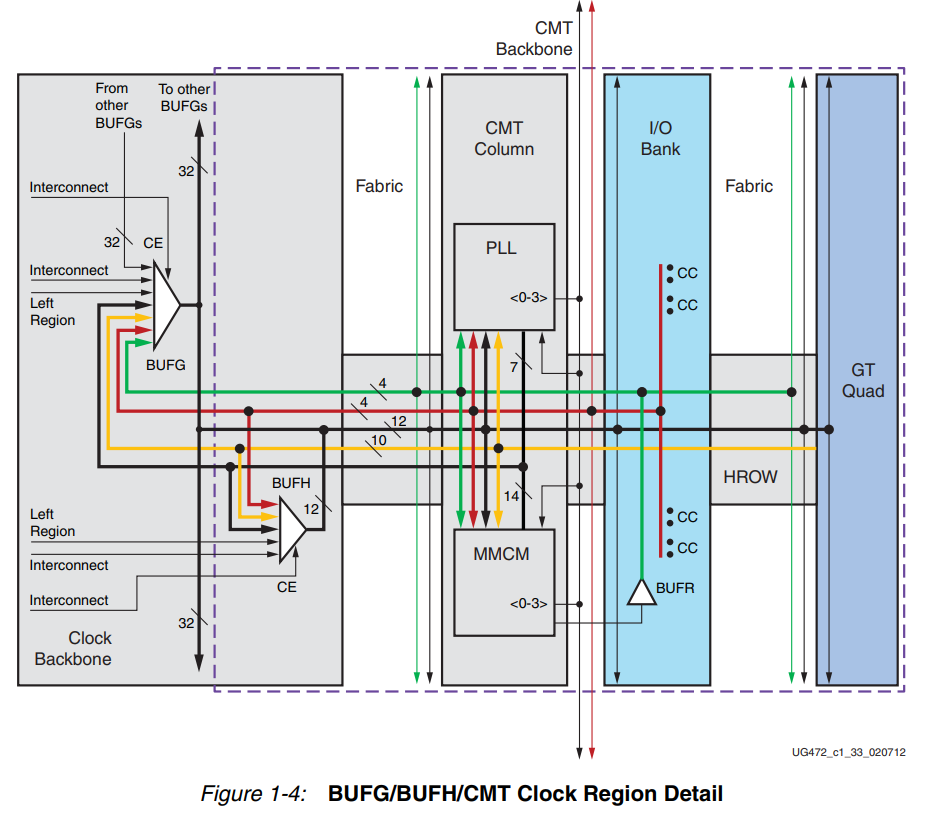

A:这应该是很多FPGA工程师都很困惑或者没有认真相关的一个问题,首先来看Clock Region的定义,我们以7系列为例:

image-20230513230025082

image-20230513230025082

可以看出,Clock Region是包含很多东西的:CLB、CMT、BUFG、BUFH等,当然也包括IO Bank,CLB中又包含了FF、LUT、DSP等资源。

而IO Bank的定义如下:

I/O banks are collections of I/O blocks (IOBs), with configurable SelectIO drivers and receivers, supporting a wide variety of standard interfaces, both single-ended and differential.

可以看出,IO Bank一般就是指一堆有相同特性的 IO的合集,所以我们一般不会说一个bank里面包含FF/DSP这些资源。

Q:FPGA中如何对寄存器类型做初始化?

A:FPGA的初始化其实比ASIC更灵活一些,initial语句原本是用于仿真时的初始化,但在FPGA中,initial是可以被综合的,这是因为FPGA是基于SRAM查找表结构实现的,上电后需要从外部加载配置信息,这个时候initial可以让存储器载入一个初始化文件,实现初始化的操作。

但对于ASIC的话,initial只能用于仿真,无法综合。

我们甚至还可以采用如下的方式进行初始化:

initial begin : INIT $readmemh(pMemInit, mem_bk); end

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ARM9和STM32什么关系?2022-12-19 2810

-

config37中根据DACCLK配置jesd clock,请问下jesd clock大小是跟之前配的serdes pll配置的line rate成40倍关系的吗?2024-12-13 509

-

信号相位和波形什么关系?2011-10-25 7992

-

FPGA实现NCO中相位累加器的输出和查找表地址什么关系?2016-03-10 5708

-

FPGA引脚所属的IO Bank不同有关系吗2016-07-30 8809

-

无法将PLL输出路由到bank 2-bank 0工作2019-06-10 2088

-

请问一下单片机、ARM、MCU、DSP、FPGA、嵌入式之间有什么关系?2021-09-18 2305

-

MCU、DSP和FPGA有什么关系2021-09-22 1543

-

MAC与PHY是什么关系?2021-09-27 3085

-

DSPIC与DSP什么关系?2023-10-17 614

-

FPGA_Alarm_Clock2016-02-22 542

-

USB接口与雷电接口有什么关系?2020-01-13 20850

-

射频芯片和基带芯片是什么关系?2020-11-20 21316

-

Xilinx FPGA中HP/HR/HD Bank的用途2022-02-26 7261

-

FPGA中HP/HR/HD Bank的应用2022-04-07 12876

全部0条评论

快来发表一下你的评论吧 !