HDB3编解码简析

描述

2.设计

2.1.需求分析

此次需求提供的十分明确,给出了编码规则及示例,明确了编解码端口要求;仿真模块根据设计进行适配。

2.2.HDB3编码模块

对HDB3编码规则解读如下:

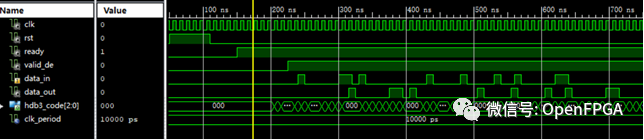

复位(RST)有效(1)时,进行初始化,输出VALID为0、HDB3_CODE为0编码(000)。采用异步复位、同步释放。当复位(RST)无效(0)时进行编码。

在输入时钟CLK的上升沿进行转换。

在CLK上升沿进行判别时,当输入READY为有效(1),DATA_IN有效,为0或1。

对READY和DATA_IN打一节拍,人为产生1个CLK的延时。

在CLK上升沿进行编码判别,DATA_IN有效为1时,立即进行编码,若存在待转换的0,待转换的0也进行编码,并加入待输出编码队列;当DATA_IN有效为0时,若存在待转换的0的个数为(0~3)、也即当前为第4个0,则进行编码,并加入待输出编码队列,否则暂停编码。

在CLK上升沿进行编码输出,若存在待输出编码,则输出VALID为1、HDB3_CODE为对应编码。

一共7种编码形式,对应0、±1、±B、±V;1可能被编码为+1、-1,0可能被编码为0、+B、-B、+V、-V。1、B极性交替(+、-交替出现)、V极性交替;第一个编码极性为+。当出现0时,若是连续的第4个0,则替换为V(极性按交替规则),然后若V极性和前一个1或B的极性不同,则将连续4个0中的第1个0替换为B且极性和V相同,其余0编码为0.由此可见,编码应在RST无效(为0)、READY有效(为1)时按照DATA_IN(0或1)、积累的待编码0数量(0~3)、上一个1或B的极性、上一个V的极性开展,编码后更新待输出编码数量和待输出编码队列。故在编码模块“tt_hdb3_encoder”中设置了如下信号量:

tmp_rst:std_logic_vector(1 downto 0),初始化为00,用于复位同步释放,同时将复位输入RST有效性由1变为0.

tmp_din,tmp_ready:std_logic,分别对DATA_IN和READY打一节拍。

tmp_dataout,深度为4、宽度为3的输出编码缓冲,最多4个。

flag_1BPOL、flag_VPOL:std_logic,1或B极性、V极性标志位,表征上一个1/B/V的极性,0表示-、1表示+。

cnt_tbpo:natural range 0 to 7 := 0,待输出编码个数,实际范围为(0~4)。

cnt_tbc:natural range 0 to 3 := 0,待编码0个数,范围为(0~3)。当cnt_tbpo>0时,每个clk上升沿将输出编码缓冲的(cnt_tbpo-1)编码对外输出。具体代码实现使用VHDL,在ISE14.7中完成,文件为“tt_hdb3_encoder.vhd”。2.3.HDB3解码模块相对于编码,HDB3解码较为简单,输入有效时,将±1解码为1、将0/±B/±V解码为0;解码模块tt_hdb3_decoder的复位、输入打节拍处理同编码模块。

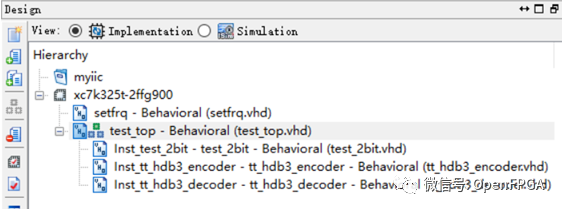

具体代码实现使用VHDL,在ISE14.7中完成,文件为“tt_hdb3_decoder.vhd”。2.4.编解码仿真模块编解码仿真需要提供可控的输入数据流DATA_IN。此次,通过附加test_2bit模块来提供仿真数据流,建立一个多位的std_logic_vector(80位),在CLK时钟上升沿从低位逐位移出。仿真准备:将test_2bit、tt_hdb3_encoder、tt_hdb3_decoder例化在test_top工程下,但是将test_2bit的输入时钟和编解码模块的输入时钟取反,便于在编解码仿真时输入数据稳定。

3.验证

由于预建立了仿真工程test_top,仿真文件tbw_test_top处理较为简单,设置RST和READY即可。在ISE14.7环境下使用ISim完成了仿真验证。

在Vivado2018.3环境下(仿真Vivado Simulator)也进行了仿真验证。

资源使用情况(Target Device: xc7k325t-2ffg900,ISE14.7):

| Module Name | Slices | Slice Reg | LUTs | BUFG | 说明 |

|---|---|---|---|---|---|

| test_top | 1/36 | 0/47 | 1/79 | 1/1 | 测试top文件 |

| Inst_test_2bit | 3/3 | 8/8 | 8/8 | 0/0 | 测试激励文件1 |

| Inst_tt_hdb3_decoder | 4/4 | 8/8 | 3/3 | 0/0 | 解码模块 |

| Inst_tt_hdb3_encoder | 28/28 | 31/31 | 67/67 | 0/0 | 编码模块 |

审核编辑:刘清

-

基于VHDL语言的HDB3码编解码器设计2023-10-13 581

-

怎样去设计一种基带HDB3编解码系统2021-08-09 1843

-

如何设计一个简单的HDB3的电路?2019-11-22 1706

-

labview设计HDB3码型输出2018-12-11 4916

-

基于Verilog HDL语言设计用于数字通信系统中的HDB3编解码器2018-07-16 6002

-

求HDB3码 基于labview2017-11-13 4096

-

基于FPGA的HDB3编解码的实现2016-04-15 4227

-

基于XC9572实现HDB3编解码的完整电路及VHDL程序2013-05-30 3343

-

基于FPGA的HDB3编解码系统2013-04-07 2414

-

基于FPGA的HDB3编解码器设计2010-07-28 881

-

基于CD22103的AMI/HDB3编解码电路设计2010-04-13 2621

-

基于CPLD的HDB3码编解码电路的设计2010-02-24 905

-

用XC9572实现HDB3编解码设计2009-03-28 2031

全部0条评论

快来发表一下你的评论吧 !