FPGA应用设计优秀电源管理解决方案

可编程逻辑

描述

为 FPGA 应用设计优秀电源管理解决方案不是一项简单的任务,相关的技术讨论有很多很多。今天小编要为大家分享的内容『FPGA 的电源管理』主要有两个目的——

☞ 找到正确解决方案并选择最合适的电源管理产品

☞ 如何优化实际解决方案使其用于 FPGA

找到合适的电源解决方案

寻找为 FPGA 供电的最佳解决方案并不简单。许多供应商以适合为 FPGA 供电的名义推销某些产品。为 FPGA 供电的 DC-DC 转换器选择有何特定要求?其实并不多。一般而言,所有电源转换器都可用来为 FPGA 供电。推荐某些产品通常是基于以下事实:许多FPGA应用需要多个电压轨,例如用于 FPGA 内核和 I/O,还可能需要额外的电 压轨来用于 DDR 存储器。将多个DC-DC 转换器全部集成到单个稳压器芯片中的 PMIC(电源管理集成电路)常常是首选。

一种为特定 FPGA 寻找优秀供电解决方案的流行方法是使用许多 FPGA 供应商都提供的已有电源管理参考设计。这对于优化设计来说是一个很好的入门方式。但此类设计往往需要修改,因为

FPGA 系统通常需要额外的电压轨和负载,这些也需要供电;

在参考设计上增加一些东西常常也是必要的;

FPGA 的输入电源不是固定的,输入电压在很大程度上取决于实际的逻辑电平以及 FPGA 所实现的设计。

完成对电源管理参考设计的修改之后,它看起来将与最初的参考设计不同。可能有人会辩称,最好的解决方案是根本不用电源管理参考设计,而是直接将所需的电压轨和电流输入到电源管理选型与优化工具中,例如 ADI 公司的 LTpowerCAD 等。

图1. 通过 LTpowerCAD 工具选择合适的 DC-DC 转换器来为 FPGA 供电。

LTpowerCAD 可用来为各个电压轨提供电源解决方案。它还提供一系列参考设计,以让设计人员快速入门。LTpowerCAD 可以从 ADI 公司网站免费下载。☞下载链接:http://www.analog.com/cn/design-center/ltpowercad.html

如何优化实际解决方 案以用于FPGA

一旦选择了电源架构和各个电压转换器,就需要选择合适的无源元件来设计电源。做这件事时,需要牢记 FPGA 的特殊负载要求——

各项电流需求

电压轨时序控制

电压轨单调上升

快速电源瞬变

电压精度

FPGA 输入电容

各项电流需求

FPGA 的实际电流消耗在很大程度上取决于使用情况。不同的时钟和不同的FPGA 内容需要不同的功率。因此,在 FPGA 系统的设计过程中,典型 FPGA 设计的最终电源规格必然会发生变化。FPGA 制造商提供的功率估算工具有助于计算解决方案所需的功率等级。在构建实际硬件之前,获得这些信息会非常有用。但是,为了利用此类功率估算工具获得有意义的结果,FPGA 的设计必须最终确定,或者至少接近最终完成。

通常情况下,工程师设计电源时考虑的是最大 FPGA 电流。如果最终发现实际 FPGA 设计需要的功率更少,设计人员就会缩减电源。

电压轨时序控制

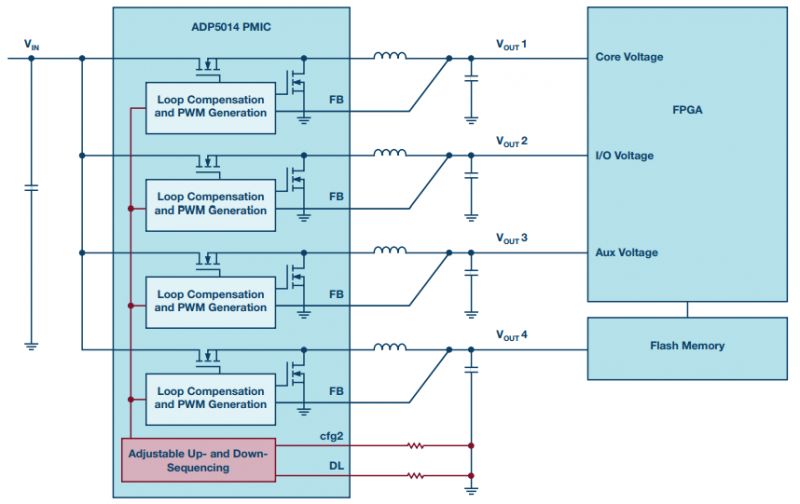

许多 FPGA 要求不同电源电压轨以特定顺序上电。内核电压的供应往往需要早于 I/O 电压的供应,否则一些 FPGA 会被损坏。为了避免这种情况,电源需要按正确的顺序上电。使用标准 DC-DC 转换器上的使能引脚,可以轻松实现简单的上电时序控制。然而,器件关断通常也需要时序控制。仅执行使能引脚时序控制,很难取得良好的结果。更好的解决办法是使用具有高级集成时序控制功能的 PMIC,例如 ADP5014。图2中用红色表示的特殊电路模块支持调整上电和关断时序。

图2. ADP5014 PMIC 集成了对灵活控制上电/关断时序的支持。

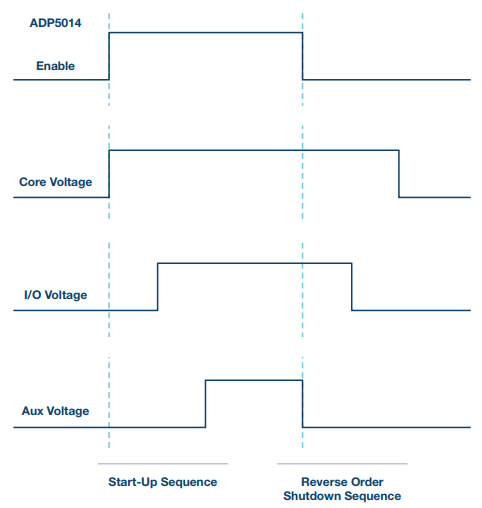

图 3 显示了利用此器件实现的时序控制。通过 ADP5014 上的延迟 (DL) 引脚可以轻松调整上电和关断时序的时间延迟。

图3. 多个FPGA电源电压的启动和关断顺序。

如果使用多个单独的电源,增加时序控制芯片便可实现所需的上电/关断顺序。一个例子是 LTC2924,它既能控制 DC-DC 转换器的使能引脚来打开和关闭电源,也能驱动高端 N 沟道 MOSFET 来将 FPGA 与某个电压轨连接和断开。

电压轨单调上升

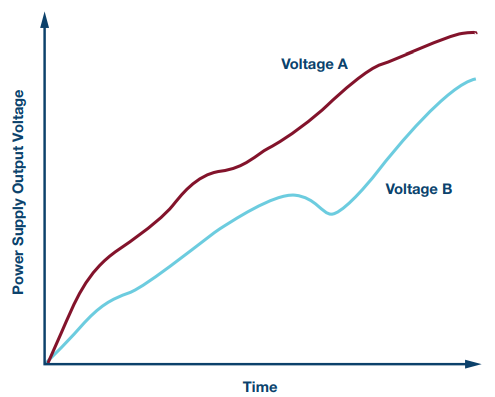

除了电压时序之外,启动过程中还可能要求电压单调上升。这意味着电压仅线性上升,如图 4 中的电压 A 所示。此图中的电压 B 是电压非单调上升的例子。在启动过程中,当电压上升到一定电平时负载开始拉大电流,就会发生这种情况。防止这种情况的一种办法是延长电源的软启动时间,并选择能够快速提供大量电流的电源转换器。

图4. 电压A单调上升,电压B非单调上升。

快速电源瞬变

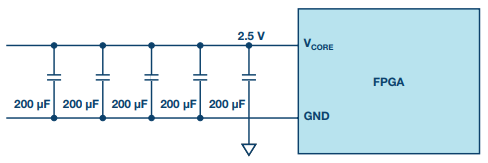

FPGA 的另一个特点是它会非常迅速地开始抽取大量电流。这会在电源上造成很高的负载瞬变。出于这个原因,许多 FPGA 需要大量的输入电压去耦。陶瓷电容非常靠近地用在器件的 VCORE 和 GND 引脚之间。高达 1 mF 的值非常常见。如此高电容有助于降低对电源提供非常高峰值电流的需求。但是,许多开关稳压器和 LDO 规定了最大输出电容。FPGA 的输入电容要求可能超过电源允 许的最大输出电容。

电源不喜欢非常大的输出电容,原因有两点——

在启动期间,开关稳压器的输出电容看来像是短路的。对此问题有一个解决办法。较长的软启动时间可以让大电容组上的电压稳定地升高,电源不会进入短 路限流模式。

图5. 很多FPGA的输入电容要求。

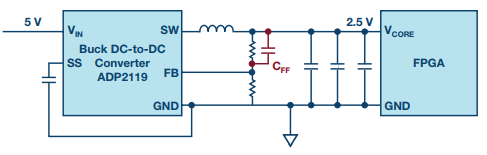

该电容值会成为调节环路的一部分。集成环路补偿的转换器不允许输出电容过大,以防止稳压器的环路不稳定。在高端反馈电阻上使用前馈电容常常可以影响控制环路,如图6所示。

图6. 当没有环路补偿引脚可用时,利用前馈电容可以调节控制环路。

针对电源的负载瞬变和启动行为,开发工具链(包括 LTpowerCAD,尤其是 LTspice)是非常有帮助的。该工具可以很好的建模和仿真,从而有效实现 FPGA 的大输入电容与电源的输出电容的去耦。 图 6 就展示了这一概念。

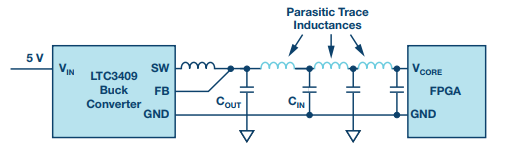

虽然 POL(负载端)电源的位置往往靠近负载,但在电源和 FPGA 输入电容之间常常存在一些 PCB 走线。当电路板上有多个彼此相邻的 FPGA 输入电容时,离电源最远的那些电容对电源传递函数的影响较小,因为它们之间不仅存在一些电阻, 还存在寄生走线电感。这些寄生电感允许 FPGA 的输入电容大于电源输出电容的最大限值,即使所有电容都连接到电路板上的同 一节点也无妨。在 LTspice 中,可以将寄生走线电感添加到原理图中,并且可以模拟这些影响。当电路建模中包含足够的寄生元件时,仿真结果接近实际结果。

图7. 电源输出电容与FPGA输入电容之间的寄生去耦。

电压精度

FPGA电源的电压精度通常要求非常高。3%的变化容差带是相当 常见的。例如,为使0.85 V的Stratix V内核电压轨保持在3%的电压精度窗口内,要求全部容差带仅为25.5 mV。这个小窗口包括 负载瞬变后的电压变化以及直流精度。同样,对于此类严格要 求,包括LTpowerCAD和LTspice在内的可用电源工具链在电源设计 过程中非常重要。

FPGA 输入电容

为了快速提供大电流,FPGA 的输入电容通常选择陶瓷电容。此类电容很适合这种用途,但需要小心选择,使其真实电容值不随直流偏置电压而下降。一些陶瓷电容,尤其是 Y5U 型,当直流偏置电压接近其最大额定直流电压 时,其真实电容值会降低到只有标称值的20%。

编辑:黄飞

-

FPGA的电源管理解决方案2023-11-24 563

-

电源管理解决方案2023-11-16 637

-

经过测试和验证的电源管理解决方案2023-02-13 1705

-

恩智浦处理器的电源管理解决方案2021-05-12 1073

-

为FPGA供电的最佳解决方案2019-12-11 3716

-

FPGA电源管理的关键是什么?2019-08-02 1457

-

怎样为FPGA选择最合适的电源管理方案?2018-08-27 2580

-

如何选择合适的FPGA电源解决方案2018-08-13 3271

-

基于FPGA应用设计优秀电源管理解决方案2018-05-07 6911

-

FPGA的电源管理不简单,五个设计死角一定不可忽视2018-03-16 15774

-

高性能的可编程电源管理解决方案2012-08-20 2685

-

用于Xilinx和Altera_FPGA的电源管理解决方案2012-08-13 3021

-

用于Xilinx和Altera FPGA的电源管理解决方案2012-08-10 948

-

集成电源管理解决方案2011-12-12 1127

全部0条评论

快来发表一下你的评论吧 !