看一下多片FPGA原型验证系统的时钟同步

可编程逻辑

描述

SoC设计是一个整体的芯片设计,最终整个设计将在统一到一块硅片上完成整个芯片,但是,原型验证中,这个SoC的设计要分布在多个FPGA芯片上,因此整体的设计连续性会受到影响。将我们的RTL设计分别映射到多个FPGA芯片上有三个特别的方面,我们需要特别关注。时钟、复位和启动条件。为了尽可能实现FPGA原型平台和最终SoC之间的完全保真度,时钟、重置和启动应表现为FPGA之间的硬边界不存在。

这篇文章,我们来看一下多片FPGA原型验证系统的时钟同步。先从多片FPGA原型平台上综合时钟网络时会存在的两个潜在问题说起:

时钟偏移和时钟不确定性:一种常见的设计方法是使用FPGA硬件板上的PLL来生成所需的时钟,并将其作为主要输入分配给每个FPGA。由于到达FPGA所采用的路径不同,板载PCB轨迹线和缓冲器可能会在相关时钟之间引入一些不确定性和时钟偏移。

如果忽略,这种偏移可能会在这些相关时钟之间的短路径上导致保持时间违例。后端布局布线工具通常可以解决FPGA内的保持时间违例,但目前无法导入从综合之前引入的时钟偏斜和不确定性信息。为了解决这个问题,FPGA拥有PLL(通常是FPGA中MCMM的一部分)可以与板的PLL结合使用或代替板的PLL。后端工具了解MCMM的偏斜和不确定性,并可以在布局过程中解决这些问题。然而,分布式MCMM的使用可能会带来上述第二个潜在问题。

时钟同步:当在每个FPGA上本地重新生成相关时钟时,存在一个潜在的时钟同步问题,该问题确实会影响原始SoC设计,其中时钟是从公共源生成和不受信任的。当一个N分频时钟的多个拷贝来自一个基本时钟,但由于复位或初始启动条件以及刚好不走运遇到硬件故障,它们就不同步。

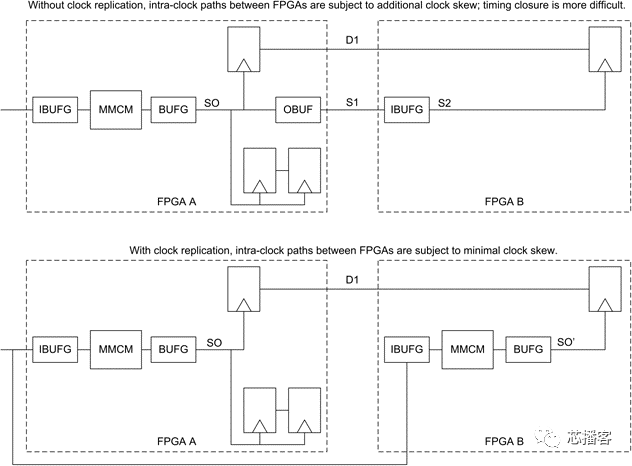

经过分割设计的时钟网络分布在相应的FPGA以及板上的其他时钟组件上。通过成功的时钟门转换,可以使跨越所有FPGA的大量不同时钟变得更容易,从而减少时钟的数量和复杂性。然而,仍有许多时钟驱动器需要在多个FPGA中复制。重要的是,这些复制时钟保持同步,并且在主时钟的正确边缘上生成任何分频时钟。这取决于每个FPGA在同一时钟边缘上的复位应用。因此,有一种通用的FPGA之间的时钟分布,如图所示,

在该图中,我们看到在板上生成的源时钟,而在每个FPGA中使用本地MMCM来重新同步,然后通过BUFG全局缓冲器重新分配时钟。在许多情况下,这种小型FPGA时钟树需要手动插入设计中。一般分割软件将会引入自动将公共时钟电路插入每个FPGA的功能。

一般SoC在顶层会设计具有全时钟管理的CRG模块,只需要在一个顶层模块上进行更改,然后使用复制将相同的结构分区到每个FPGA中。即使SoC 的RTL中的时钟分布在整个设计过程中,复制也将帮助我们将更改限制为比其他情况下可能需要的更少的RTL文件。 如果我们使用按时钟域进行分割设计,则可以避免复制时钟缓冲区。这种方法的成功将取决于不同时钟的相对扇出以及时钟域之间的路径数量。

无论采用何种分割策略,每个FPGA都是一个离散的实体,为了时钟同步,每个FPGA必须有自己的时钟生成,而不是依赖于来自另一个FPGA中的生成器的时钟。因此,时钟发生器必须在每个FPGA中实例化,即使SoC设计的一小部分在那里被划分。

时钟发生器在原型平台中如何帮助我们?MMCM的PLL具有可以锁定的最小频率,因此FPGA的输入时钟必须至少以该速率驱动。比如某型号的MCMM的最小锁定频率为10MHz,而之前的技术为30MHz或更高,这使得它们对我们的用途特别有用。它们能够产生比它们可以接受的输入慢得多的时钟。因此,我们的任务是在原型上组装一个时钟树,在那里我们在FPGA外部保持较高的频率,然后在内部分频,同时保持内部时钟同步。 我们通过以下方式实现:

如果SoC设计中在顶层具有时钟发生CRG模块,则在RTL中例化创建时钟生成器块,以替换SoC中CRG模块时钟的等效部分。我们使用全局基准时钟来驱动MCMM,MCMM通过其除以n的输出生成较慢的导数。

选择板上生成的任何一个全局系统时钟;其频率必须高于最小MMCM锁定频率。

用全局时钟驱动新RTL时钟树的输入。

在新的时钟生成器RTL中,创建MMCM和BUFG实例树,以创建所有必要的子时钟。

在分割软件中,根据需要将MMCM和BUFG复制到每个FPGA中,以驱动分配到那里的逻辑。

在IO的trace分组分配期间,必须将全局时钟分配给FPGA的全局时钟输入。

如果时钟产生或者门控更加分布,那么我们可能需要将BUFG和MMCM组件直接实例化到不同的RTL文件中,但我们应该始终关注复制如何使此过程更容易。

对于多FPGA原型验证系统,我们可能需要时钟树中额外的层次结构。我们应该使用板载PLL驱动每个板的主时钟,并在每个板上使用PLL重新同步,使用板的本地PLL输出驱动每个FPGA,通过使用PLL和匹配的延迟时钟PCB迹线和电缆来避免FPGA板之间的时钟偏移。因为可以使用多个PLL和MCMM,所以本地慢时钟必须与全局时钟同步。这是通过使用基准时钟作为每个MMCM的反馈时钟输入来实现的。

为什么不使用板载全局时钟资源生成所有时钟。毕竟,我们可能在电路板上安装了专门的PLL设备,例如,最低锁定频率甚至更低。这里需要注意的问题是,根据电路板的不同,时钟到达每个FPGA的时间之间可能存在一定的偏差,特别是对于不太复杂的电路板,这些电路板不是专门为此设计和布置的。这种影响将在更大的系统中被放大,并可能导致FPGA之间传递信号的保持时间违规问题。

审核编辑:刘清

-

什么是FPGA原型验证?FPGA原型设计的好处是什么?2024-01-12 2410

-

多片FPGA原型验证的限制因素有哪些?2023-06-19 1290

-

一文掌握多片FPGA的多路复用2023-06-06 2393

-

正确认识原型验证多片FPGA自动分割工具2023-05-23 1115

-

多片FPGA原型平台中的启动同步研究2023-05-22 708

-

如何将这些SoC的逻辑功能原型正确的移植到多片FPGA中?2023-05-10 779

-

FPGA原型系统装配文件:Assign Traces介绍2023-05-08 968

-

FPGA原型验证系统中复制功能模块的作用2023-05-04 1563

-

多台FPGA原型验证平台可自由互连2023-04-11 1895

-

什么是FPGA原型验证?如何用FPGA对ASIC进行原型验证2023-04-10 2886

-

验证中的FPGA原型验证 FPGA原型设计面临的挑战是什么?2022-07-19 2511

-

关于FPGA开发板和原型验证系统对比介绍2022-04-28 3931

-

FPGA原型验证的技术进阶之路2020-08-21 4815

全部0条评论

快来发表一下你的评论吧 !