如何设置TC397的QSPI模块工作在CPH =1协议模式?

电子说

1.4w人已加入

描述

问题描述

客户在调试QSPI模块过程中,将TC397的QSPI模块的CPOL位设置为1,但是示波器显示时钟引脚输出信号的空闲状态并不是高电平,在debug模式下,可观察到CPOL位已设置为1,这是怎么回事呢?

图1

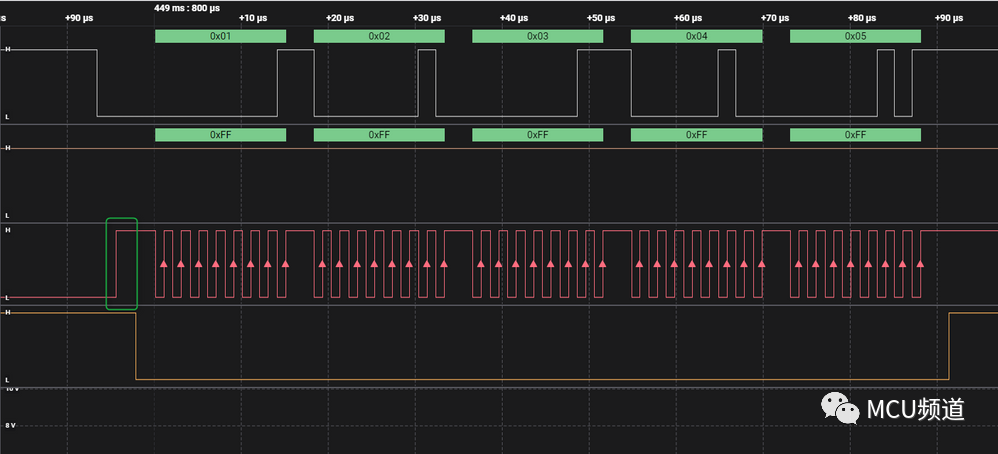

设置TC397的QSPI模块工作在CPOL=1, CPH =1协议模式

解决过程

SpiIf_initChannelConfig()函数在初始化QSPI channel时,提供了很多配置参数项,其中就有clockPolarity,但是单单设置clockPolarity= SpiIf_ClockPolarity_idleHigh,虽然会将CPOL位设置为1,但是捕获的波形显示空闲状态电平并未变成高电平。

这是由于SpiIf_initChannelConfig()函数的默认参数项设置IDLE时序阶段时长为0,使得帧传输间隙缺少IDLE时序阶段,所以需要设置csInactiveDelay > 0(如下所示)来插入IDLE时序阶段,如下图所示。

void SpiIf_initChannelConfig(SpiIf_ChConfig *config, SpiIf *driver)

{

config->driver = driver;

config->baudrate = 0;

config->mode.enabled = 1;

config->mode.autoCS = 1;

config->mode.loopback = 0;

config->mode.clockPolarity = SpiIf_ClockPolarity_idleHigh;

config->mode.shiftClock = SpiIf_ShiftClock_shiftTransmitDataOnLeadingEdge;

config->mode.dataHeading = SpiIf_DataHeading_msbFirst;

config->mode.dataWidth = 8;

config->mode.csActiveLevel = Ifx_ActiveState_low;

config->mode.csLeadDelay = SpiIf_SlsoTiming_0;

config->mode.csTrailDelay = SpiIf_SlsoTiming_0;

config->mode.csInactiveDelay = SpiIf_SlsoTiming_2;

config->mode.parityCheck = 0;

config->mode.parityMode = Ifx_ParityMode_even;

config->errorChecks.baudrate = 0;

config->errorChecks.phase = 0;

config->errorChecks.receive = 0;

config->errorChecks.transmit = 0;

}

图2

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

国产智驾域控上为什么很多是英飞凌TC397?2024-09-13 14252

-

TC397 GPIO与电池短路,箝位电压是多少?2024-06-04 765

-

TC397进入SCR模式的条件是什么?2024-05-31 776

-

TC397关于QPSI通信中的CS的问题求解2024-05-29 511

-

TC397 CAN不能进入normal模式怎么处理?2024-02-04 599

-

SCR模式下如何通过TC397唤醒TLF35584进入NORMAL模式?2024-02-02 1179

-

TC397的TOM和STM会冲突怎么解决?2024-02-01 820

-

如何通过RGMII接口将TC397连接到Marvell 88Q5152?2024-01-26 1267

-

在Tc397中如何用Tim捕捉时间戳?2024-01-22 1388

-

AURIX TriCore学习笔记六:TC397开发环境搭建2021-11-13 2285

全部0条评论

快来发表一下你的评论吧 !