栅极驱动器的原理及应用

电子说

描述

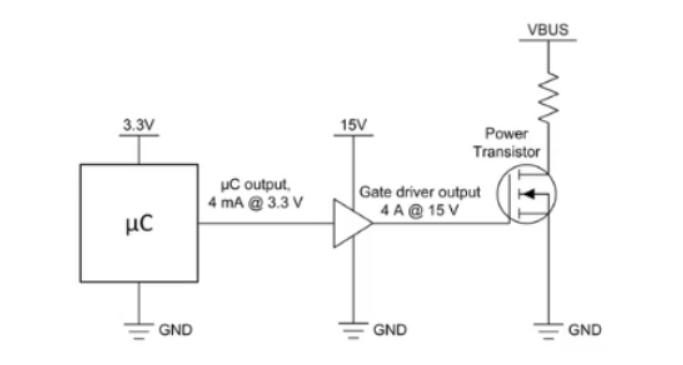

栅极驱动器是一个用于放大来自微控制器或其他来源的低电压或低电流的缓冲电栅极驱动器的原理及应用分析用中,微控制器输出通常不适合用于驱动功率较大的晶体管。

GBT/功率MOSFET的结构使得栅极形成一个非线性电容。给栅极电容充电会使功率器件导通,并允许电流在其漏极和源极引脚之间流动,而放电则会使器件关断,漏极和源极引脚上就可以阻断大电压。

当栅极电容充电且器件刚好可以导通时的最小电压就是阈值电压(VTH)。为将IGBT/功率MOSFET用作开关,应在栅极和源极/发射极引脚之间施加一个充分大于VTH 的电压。

考虑一个具有微控制器的数字逻辑系统,其I/O引脚之一上可以输出一个0 V至5 V的PWM信号。这种PWM将不足以使电源系统中使用的功率器件完全导通,因为其过驱电压一般超过标准CMOS/TTL逻辑电压。

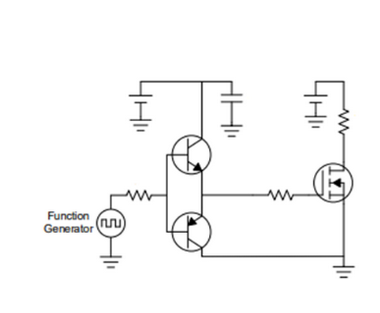

过去,使用双极结型晶体管(BJT)图腾柱驱动低侧配置中的电源开关。但是,由于栅极驱动器IC的诸多优势及其附加特性,它日益取代了这些分立式解决方案。典型BJT图腾柱配置与典型栅极驱动器IC。

分立式电路的一个显著缺点是它不提供保护,而栅极驱动器IC集成了对于确保可预测和稳定的栅极驱动非常重要的功能。相比之下,BJT图腾柱允许MOSFET产生压降,但漏极电流会显著上升。电流上升会导致功耗过大,并可能损坏MOSFET。

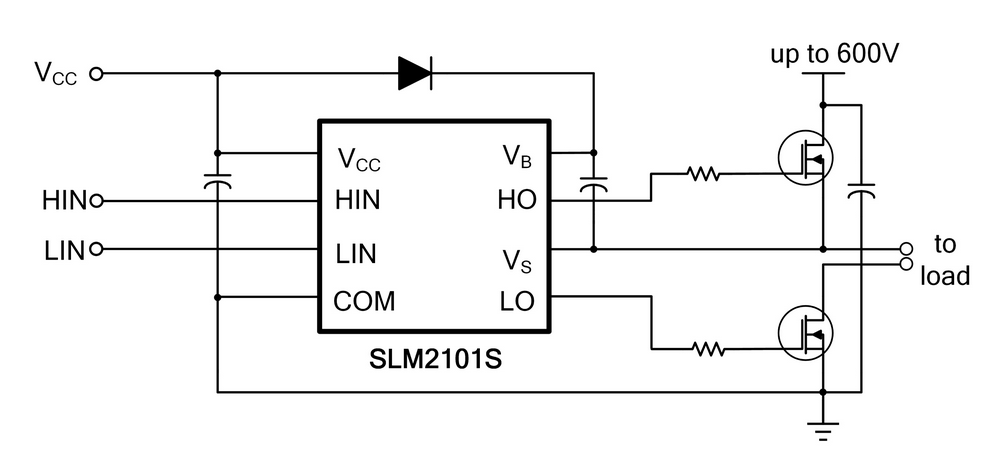

上海数明HVIC栅极驱动器SLM2304S用于驱动最高600V的N沟道MOSFET或IGBT,兼容IR2304(S)系列,广泛应用于BLDC,大功率DC-DC电源,家电,步进驱动器,逆变器等领域。

VS脚⽣产负压的原因和对策

VS脚生产负压的原因

自举式电源是一种应用广泛,给高边栅极驱动电路供电的方法,用来驱动高边N沟道的MOS 或者IGBT。自举式电源技术具有结构简单,成本低的优点,但也存在缺点,其一是占空比无 法做到100%,受到自举电容刷新电荷所需时间,VBS欠压保护阈值的限制,其二是会导致 开关器件的源极看到负压,可能导致HVIC的输出错误。

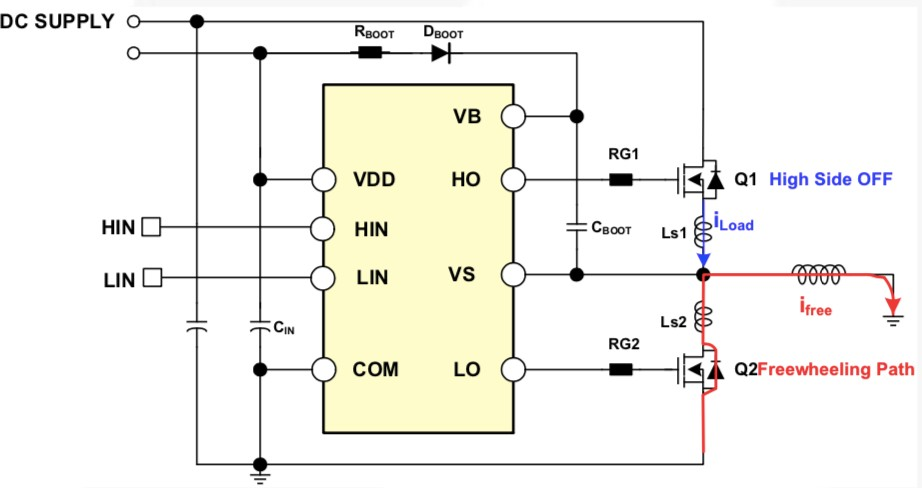

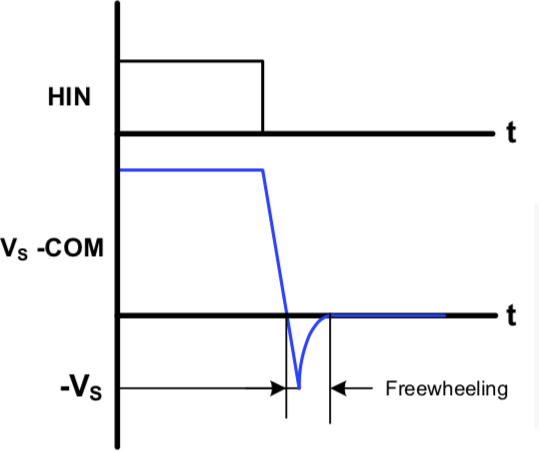

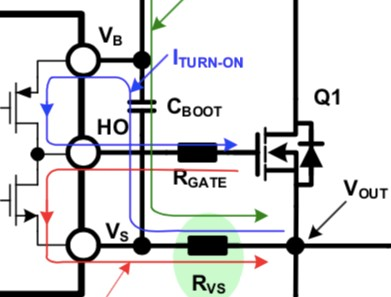

自举式驱动电路最大的难点在于:当开关器件关断时,其源极 的负电压会使负载电流突然流过续流二极管,如图 1所示。该负电压会给栅极驱动电路的输出端造成麻烦,因为它直接影响驱动电路或 PWM 控制集成电路的源极 VS 引脚,可能会明显地将某些内部电压下拉到地以下,如图 2所示。另外一个问题是,自举电容 CBOOT,通过自举二极管 DBOOT, 被电源 VDD 瞬间充电。由于 VDD 电源以地作为基准,自举电容产生的最大电压等于VDD 加上源极上的负电压振幅,可能会使自举 电容处于过压状态,会有打坏电容甚至导致芯片VB/HO被打坏,短路到VS的风险。所以设计中应尽量减小VS的负压。

图1 半桥应用电路

图 2 关断期间的 VS 波形

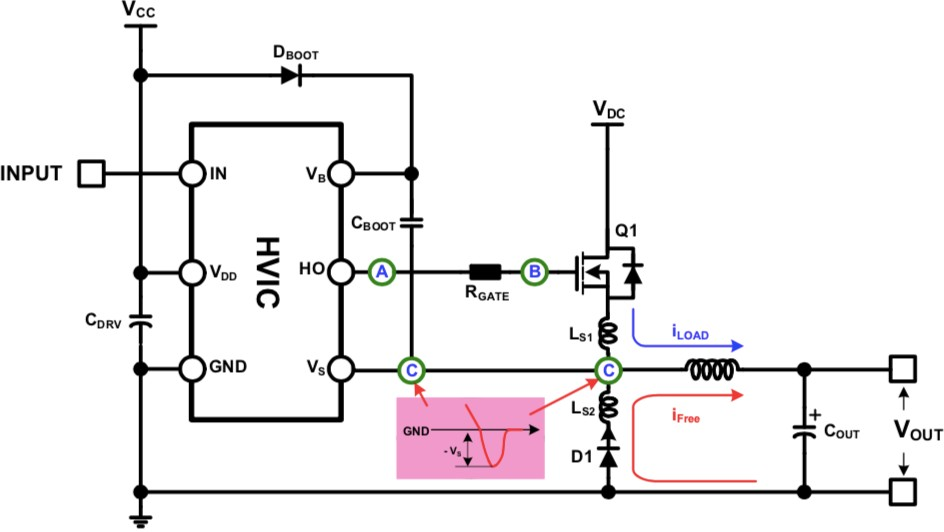

图 3 DC-DC 电源

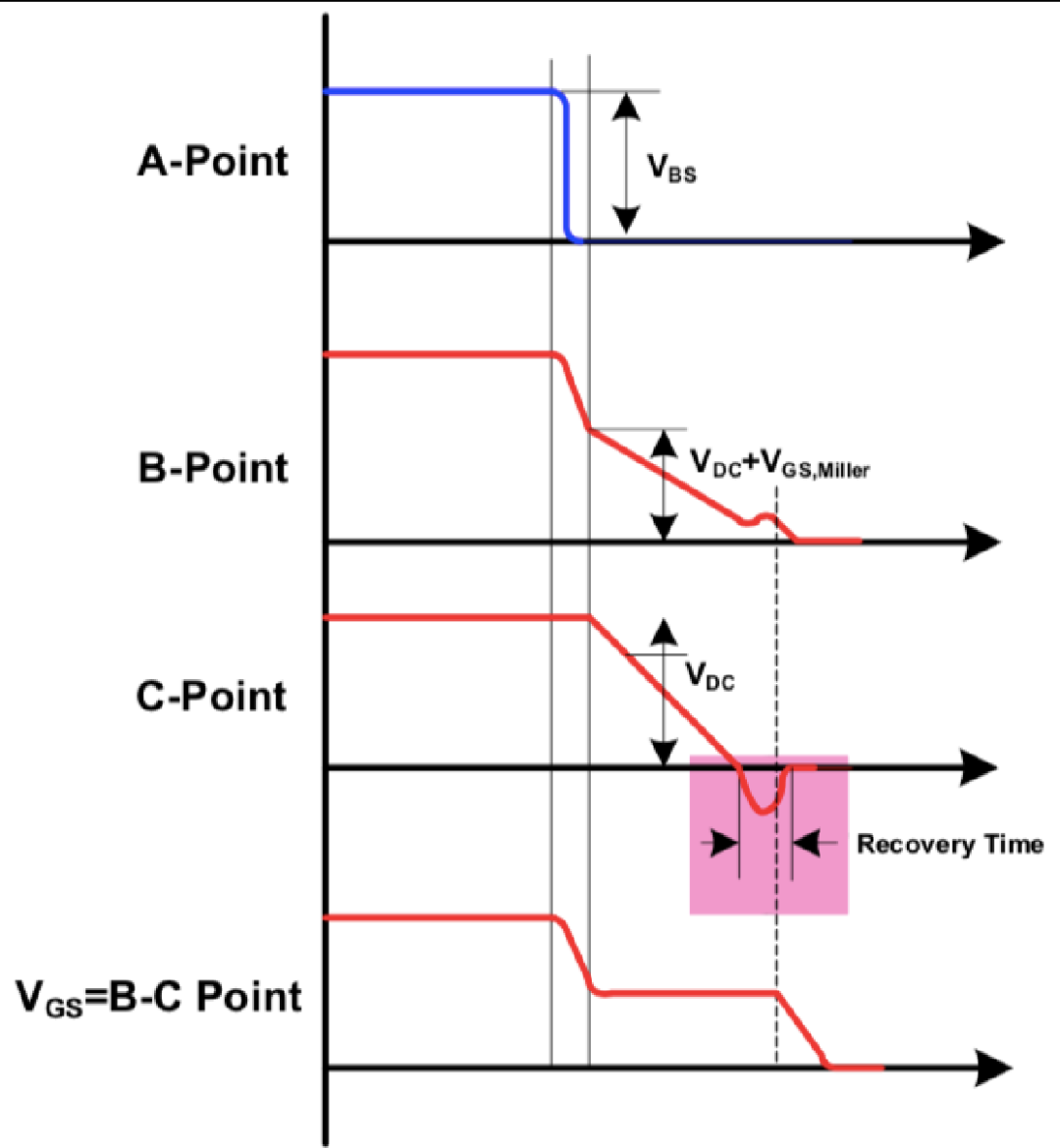

图 4 关断期间的波形

如图 3 所示,低边续流二极管的前向偏置是已知的将 VS 下拉到 COM(地) 以下的原因之一;图 4 描述了高边 N 沟道 MOSFET 关断期间的电压波形。主要问题出现在整流器换向期间,仅仅在续流二极管开始箝压之前。在这种情况下,电感 LS1 和 LS2 会将 VS 电压压低到 COM 以下,该负电压的振幅是:

VS−COM=−(VRBOOT +VFDBOOT)−(LS1+LS2)di/dt

(1)

从等式(1)可以看到,该负电压的放大倍数正比于寄生电感和开关器件的关断 速度, di/dt ;它由栅极驱动电阻, RGATE 和开关器件的输入电容,Ciss 决定。Ciss 是 Cgs 与Cgd 的和,称为米勒电容。

如何降低 VS 负压?

Ø layout 上减小寄生电感 LS1/LS2

Ø 降低开关器件的开关速度

Ø 在开关节点串一个小电阻,如下图中的 RVS 电阻(几欧姆以内),接自举电容后再到,和自举电容形成 RC 滤波,可以限制 VS 脚的下冲电压。不过需要注意这个电阻串在开关器件开启和关闭的路径上,计算门级电阻时需要考虑此阻值

Ø 如在 VS 串电阻后仍不足以限制 VS 负压,则可以在靠近 SLM2304S 芯片的 COM 和 VS脚之间并联一个快恢复二极管,朝向 VS,来钳位 VS 的负压

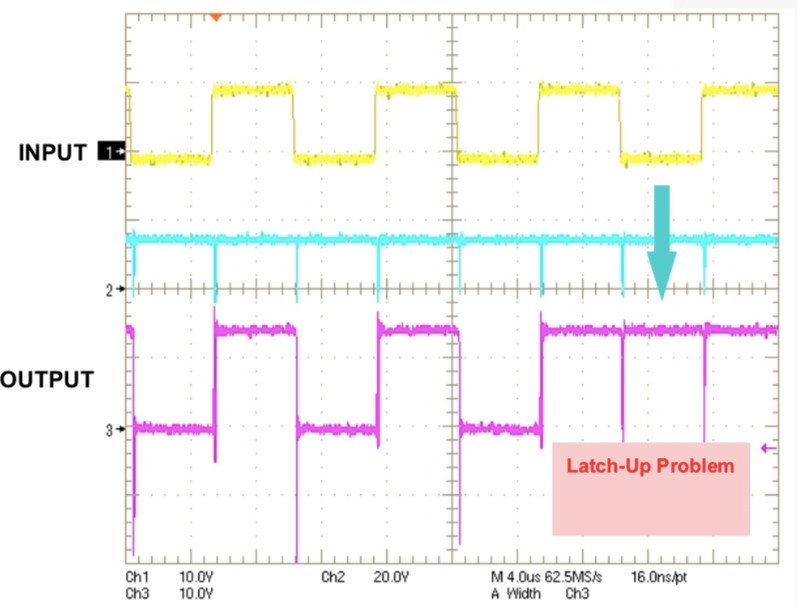

图 5 闭锁情况下的波输入输出形

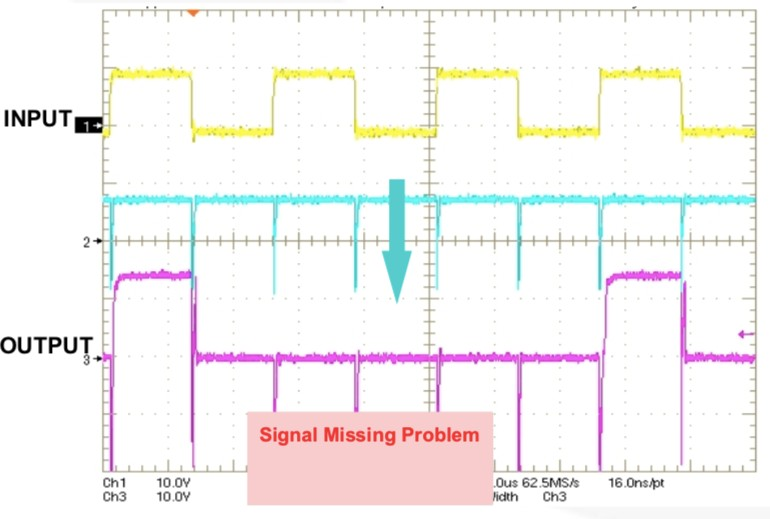

如果 VS 下冲超过规格书中标称的规格,则栅极驱动 IC 将损坏,或者高边输出暂时无法对输入转换做出响应,如图 5 和图 6 所示。建议设计中留一定余量,保证系统的可靠性。图 5 显示闭锁情况,即高边输出无法通过输入信号改变。这种情况下,半桥拓扑的外部、主电源、高边和低边开 关中发生短路。图 6 显示遗漏情况,即高边输出无法对输入转换做出响应。这种情况下,高边栅极驱动器的电平转换器将缺少工作电压余量。需要注 意的是,大多数事实证明高边通常不需要在一个开关动作之后立即改变状态。

图 6 信号丢失情况下的波形

自举电路的设计

选择自举电容值

自举电容 (CBOOT) 每次都被充电,此时,低边驱动器导通,输出电压略低于栅极驱动器的电源电压 (VDD)。自举电容仅当高边开关导通的时候放电。自举电容给高边电路提供电源(VBS),首先要考虑的参数是高边开关处于导通 时,自举电容的最大电压降。允许的最大电压降 (VBOOT) 取决于要保持的最小栅极驱动电压 ( 对于高边开关 )。如 果 VGSMIN 是最小的栅 - 源极电压,电容的电压降必须是:

ΔVBOOT = VDD − VF − VGSMIN

(2)

其中:

VDD= 栅极驱动器的电源电压

VF=自举二极管正向电压降计算自举电容为:

CBOOT=QTOTAL/ΔVBOOT

(3)

其中 QTOTAL 是电容器的电荷总量。自举电容的电荷总量通过等式 4 计算:

QTOTAL=QGATE+(ILKCAP+ILKGS+IQBS+ILK+ILKDIODE)*tON+QLS

(4)

其中:

QGATE = 栅极电荷的总量

ILKGS = 开关栅 - 源级漏电流

ILKCAP = 自举电容的漏电流

IQBS =自举电路的静态电流

ILK = 自举电路的漏电流

QLS= 内部电平转换器所需要的电荷,对于所有的高压 栅极驱动电路

tON = 高边导通时间

ILKDIODED = 自举二极管的漏电流

另外一般的,可以根据经验公式粗略估算自举电容值:

CBOOT>10*Ciss

选择自举电阻值

自举电阻起到限制自举电容充电电流的作用,可防止电容过充,特别在一些 VS 负压较大的情况下,能降低 VS-VB 以及电容过压的风险。该电阻典型值 5~10ohm,会增加 VBS 时间常数。当计算最大允许的电压降 (VBOOT) 时,必须考虑该自举电阻引入的电压降。如果该电压降太大或电路不能提 供足够的充电时间,我们可以使用一个快速恢复或超快恢复二极管。

自举二极管的选择

在高边器件开通时,自举二极管必须能够阻止高压,并且应是快恢复或超快恢复二极管,以 减小从自举电容向电源VCC的回馈电荷。如果电容需要长期贮存电荷时,高温反向漏电流指 标也很重要。一般建议自举二极管的反向耐压值和所选MOS/IGBT的电压规格一致, trr<100ns.

VDD供电

VDD电压一般在12~15V左右,输入电容要靠近芯片VDD和COM脚。一般输入电容配置为一 个电解(10~100uF)+100nF瓷片电容,电解电容提供能量,100nF瓷片滤波,吸收可能的 电压尖峰。

逻辑输入

一般的,逻辑输入脚可以直接连接前级控制器的输出。但如空间允许,或应用环境干扰大且逻辑输入高电平比较低(如3.3V),还是建议在逻辑输入前加RC滤波,电阻串在控制器输出和逻辑输入之间,逻辑输入脚对地并一个电容,如100R,100pF。

另外,需要注意一些MCU或者软件中,如果输入控制器只输出高电平以及高阻态,低电平需 要靠HIN/LIN内部的下拉电阻来实现,则建议在HIN/LIN预留一个下拉电阻的位置。因SLM2304S HIN/LIN内部下拉电阻为500K欧姆左右,在一些噪声干扰比较大的应用中,可能出现HIN/LIN被误触发高电平的情况,此时外部加一个10K以内的下拉电阻即可解决。

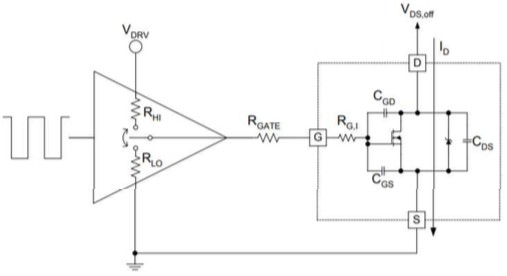

门级电阻值的选取

门级电阻在栅极驱动路径上会影响真实的驱动电流,开关损耗以及上升/下降沿,合适的阻值可以有效限制降低噪声和振铃,避免EMI问题。理论上,驱动输出可以直接和开关器件的gate直接连接,但如果没有选取一个合适的门级电阻值,由于layout和和器件本身的寄生电 感,电容,高速的dv/dt,di/dt,体二极管的反向恢复时间等因素,会导致驱动电路面临EMI, 以及高度dv/dt导致的共通等问题。

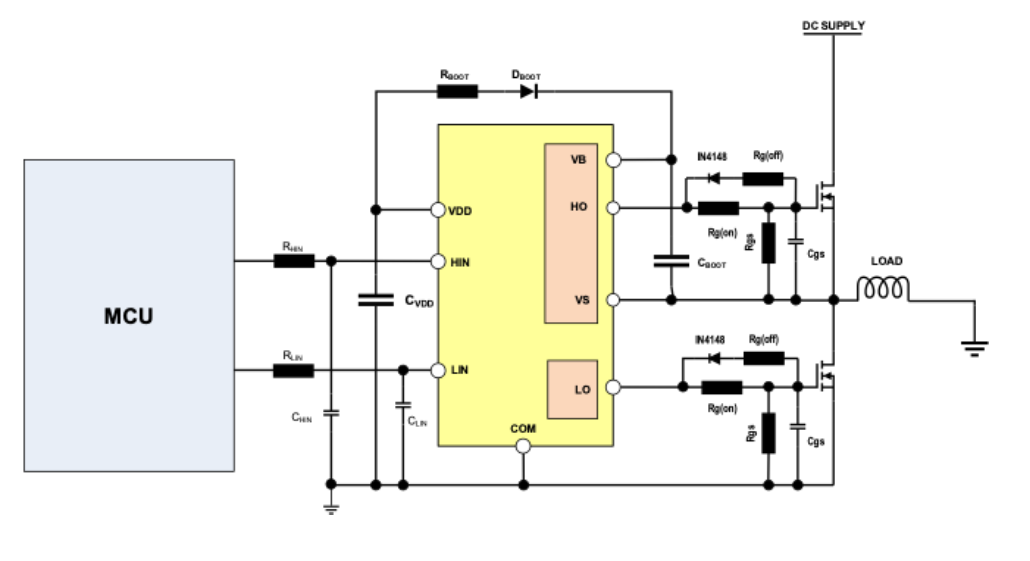

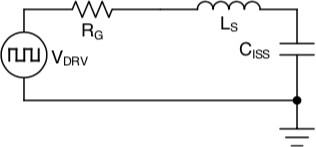

图7

图8

图7,图8两图分别为驱动电路元件示意图以及等效电路图,门级电阻值RGATE可以通过如下 步骤计算:

LS=1/[CISS*(2pifR)2]

(6)

RG=XL/Q=w*LS/Q=1/(CISS*2*pi*fR*Q)

(7)

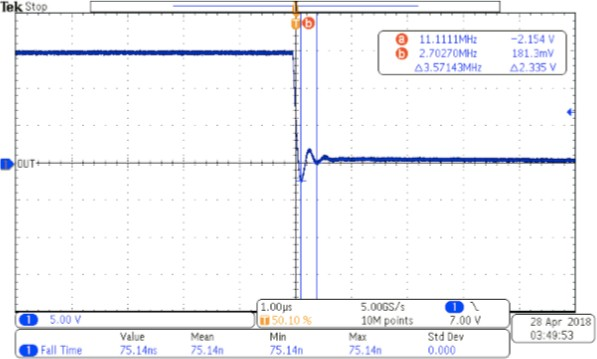

LS是栅极驱动线路上的寄生电感Ciss=CGS+CGD,规格书可查fR 是 RGATE=0 时 实 测 出 来 的 VS 振 铃 频 率 , 如 下 示 意 图 9,fR 测 得 为 3.75MHz RG=RGATE+ROH or LO+RG,I,ROH or LO是HVIC输出级上拉/下拉电阻值,规格书可以查, RG,I是开关器件内寄生的栅极网状电阻,一般在~1欧姆左右,较小可忽略,部分规格书中没有提到此参数Q是谐振电路中的Q值,一般取值0.5~1之间,Q越小,RGATE越大,栅极电压上升/下降越 慢根据等式7,即可算出理论上的RGATE,但一般实际情况中,还需要在开关速度,开关器件 温度,dv/dt,EMI等因素上折中,再确定合适的门级电阻值。

图9 RGATE=0R

快关电路

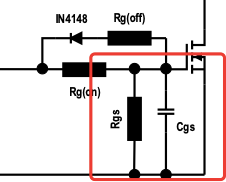

如下图,如希望快速关断来提升效率,或担心关断太慢导致共通,则可以在输出门级电阻并 一个开关二极管+一个电阻的路径,来提高关断速度,此时关断速度由二极管的反向恢复 时间决定,还可通过Rg(off)来调整关断速度。

Rgs和Cgs的作⽤

Rgs一般选10K阻值,用作电荷泄放路径,防止未工作时开关器件GS之间电荷累计导致VGS过压,打坏器件。Cgs一般可作预留,非必要器件,主要用来降低Cgd/Cgs比例,防止开关过程中的米勒效应 导致gate被Cgd耦合起来,半桥开关器件共通,钳住gate电压。该电容若需要的话,典型值 一般在1~2.2nF,注意如果太大会导致开关器件开启慢,开关损耗大,器件温度变高。

PCB 布局⾛线建议

考虑所有功率开关的配合放置,减少驱动输出线路以及开关器件电流路径,走线长度CVDD/CBOOT 去耦电容和栅极电阻的布局和布线,应尽可能靠近驱动芯片管脚避免互连链路。它会显著增加电 降低封装体距离 PCB 板的高度,以减少引脚电感效应自举二极管应尽可能靠近自举。

SLM2304S有两路输入,HIN和LIN,分别控制高边输出HO以及低边输出LO。HIN和HO同相 位,LIN和LO同相位。为防止输入控制出错,例如输入同为高,输出也同为高,从而导致MOS/IGBT共通的情况,SLM2304S采用了互锁设计,即当两路输入均为高时,输出均为低, 确保输出端的安全。当然,如果客户的应用就是需要输出HO和LO同为高的情况,我们推荐 去掉了互锁功能的SLM2106B来满足这类特殊的应用。

-

了解智能栅极驱动器2024-09-21 496

-

什么是栅极驱动器?栅极驱动器的工作原理2024-07-19 25960

-

隔离式栅极驱动器的影响2024-07-13 528

-

栅极驱动器芯片有哪些作用2024-06-10 3585

-

栅极驱动器电流多少正常啊,栅极驱动器电流怎么计算2023-07-14 4132

-

使用隔离式栅极驱动器的实用设计指南2022-11-14 830

-

不要忘了肌肉:栅极驱动器2022-11-02 850

-

栅极驱动器是什么2021-01-27 3802

-

栅极驱动器是什么,为何需要栅极驱动器?2020-12-25 11184

-

隔离式栅极驱动器的揭秘2018-11-01 2720

-

栅极驱动器的负电压介绍2018-08-17 7311

-

了解您的栅极驱动器2017-04-26 4357

全部0条评论

快来发表一下你的评论吧 !