Vivado Design Suite 用户指南介绍

FPGA/ASIC技术

描述

FPGA 技术支持灵活开展现场编程和再编程,无需通过设计修改来重建互连结构。Dynamic Function eXchange (动态功能交换,DFX)推动这一灵活性进一步发展,允许通过加载动态配置文件(通常是部分 BIT 文件)来修改工作中的 FPGA 设计。在使用完整 BIT 文件配置 FPGA 后,可下载部分 BIT 文件以修改 FPGA 中的可重配置区域,在未经重配置的器件各部分中运行的应用的完整性则不会受到任何影响。

DFX 是由多个部分组成的综合性解决方案。这些要素包括:AMD 芯片能进行动态重配置,Vivado 软件流程支持编译设计(从 RTL 到比特流),以及各种补充性功能特性(如 IP)。在此版本中,您将看到 DFX 与部分重配置( PR )术语混用,其中 DFX 表示整体解决方案,PR 则表示该解决方案的技术组成部分。

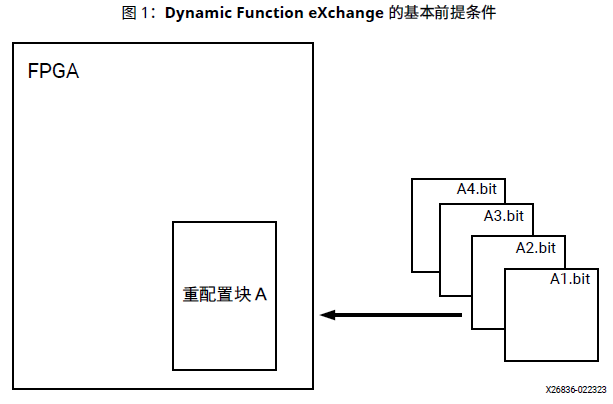

下图显示了 Dynamic Function eXchange 背后的前提条件。

如图所示,通过下载下列任一部分 BIT 文件即可修改重配置块 A 中实现的函数:A1.bit、A2.bit、A3.bit 或A4.bit。FPGA 设计中的逻辑分为 2 种不同类型:可重配置逻辑和静态逻辑。FPGA 块的灰色区域表示静态逻辑,块中标记为重配置块 A 的部分则表示可重配置逻辑。静态逻辑保持正常工作,不受加载部分 BIT 文件的影响。可重配置逻辑则替换为部分 BIT 文件的内容。

在单一 FPGA 上对多路复用硬件进行动态定时的能力是很有用的,原因有很多。其中包括:

减小实现给定函数所需 FPGA 的大小,从而降低成本和功耗

支持灵活选择可用于某一应用的算法或协议

启用设计安全性方面的新技术

改善 FPGA 容错能力

加速可配置计算

向已部署的系统交付更新(修订和新增功能特性)

除了减小大小、降低权重、功耗和成本外,Dynamic Function eXchange 还能支持无法以其它方式实现的多种新型 FPGA 设计。

-

Vivado Design Suite用户指南:逻辑仿真2025-01-15 397

-

UltraFAST设计方法指南(适用于Vivado Design Suite)2023-09-15 775

-

Vivado Design Suite用户指南:版本说明、安装和许可2023-09-13 690

-

Vivado Design Suite设计套件的UltraFast设计方法的介绍2018-11-20 3218

-

Vivado Design Suite 2014.4.1 现已推出!2017-02-09 535

全部0条评论

快来发表一下你的评论吧 !