在高速设计中跨多个FPGA分配复位信号

可编程逻辑

描述

SoC设计中通常会有“全局”同步复位,这将影响到整个设计中的大多数的时序设计模块,并在同一时钟沿同步释放复位。而在FPGA原型验证系统中,由于这些时序元件在多个FPGA之间被划分,因此确保每个FPGA仍然以相同的方式在相同的时钟沿接收复位至关重要。这是重要且值得关注的问题,但通过RTL设计中的一些附加代码模块和允许逻辑简单复制的分割工具,可以实现在高速设计中跨多个FPGA分配复位信号。

只要每个FPGA的时钟边沿相同,就不太可能在特定时钟边缘断言或释放全局复位。因此,我们可以根据需要在复位信号路径中添加尽可能多的流水线级,我们将在一瞬间利用这一点。另一个需要考虑的因素是,连接到每个FPGA的硬件板分组trace的数量通常是有限的,因此我们不需要任何用于布线全局复位的trace迹线。

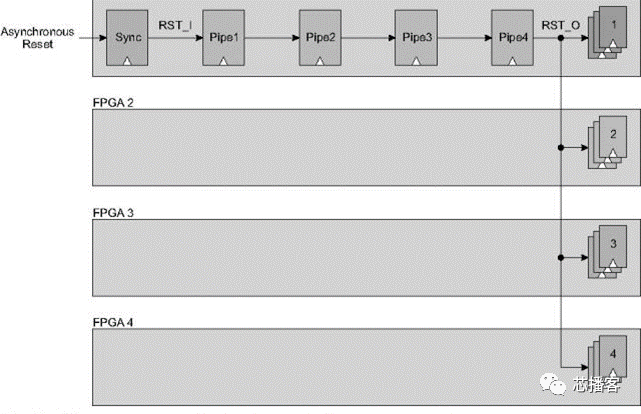

相反,我们创建了一个复位树结构,它通过FPGA本身进行布线,然后在FPGA之间使用普通的点对点trace。 比如下图设计示例,其中流水线复位驱动四个不同FPGA中的时序元件,很明显,FPGA

4中的元件将在FPGA 1中的元件之后很长时间内接收复位。

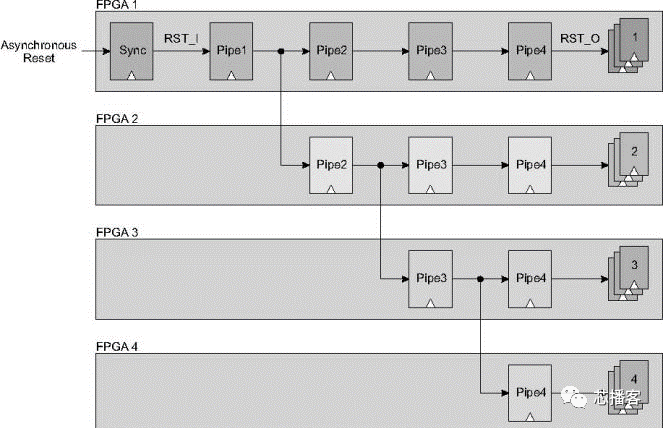

另外,输入可以是异步复位,因此第一阶段充当同步器(如果需要避免亚稳态问题,可以使用双时钟)。除了非常低的时钟速率外,以这种方式通过FPGA的布线是不可接受的,因此为了克服这一问题,我们将在每个FPGA中复制部分流水线,如图所示。

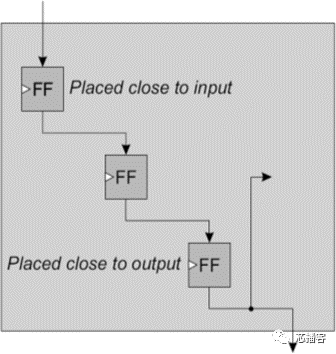

第一阶段不被复制,因为输入复位信号的同步必须仅在一个地方完成。每个FPGA中的流水线级仍有可能引入延迟,因为如果每个级中有一个FF,那么它可能被放置在输入PAD焊盘、输出PAD焊盘附近或两者之间的任何位置;这在每个FPGA中也可能不同。答案是为每个管道阶段使用三个FF,如图所示。

这允许第一和第三FF放置在FPGA边缘的IO FF中。然后,有一个完整的时钟周期用于重置传播到内部FF和输出FF,从而大大放松了位置和路线上的时间限制。再次,与全局复位信号本身的效果相比,这些管道级只引入了微不足道的延迟。

审核编辑:刘清

-

在高速PCB设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上2009-09-06 8976

-

图文解析如何分配FPGA管脚2015-01-06 4506

-

FPGA全局复位及局部复位设计分享2019-05-17 3460

-

高速PCB中的信号回流及跨分割2009-11-17 1230

-

在FPGA开发中尽量避免全局复位的使用?(2)2017-02-11 1279

-

FPGA的理想的复位方法和技巧2017-11-22 6478

-

分享跨分割设计对高速电路信号的影响2018-01-23 8850

-

FPGA设计中的异步复位同步释放问题2018-06-07 2650

-

在FPGA开发中尽量避免全局复位的使用?2022-05-06 3448

-

FPGA设计使用复位信号应遵循原则2023-03-30 2000

-

FPGA设计中的复位2023-05-12 6500

-

在高速PCB设计中,多个信号层的敷铜在接地和接电源上应如何分配?2023-11-24 2103

-

在高速电路设计中,如何应对PCB设计中信号线的跨分割2023-12-04 1799

-

FPGA同步复位和异步复位2024-07-17 3730

-

FPGA复位的8种技巧2024-11-16 2094

全部0条评论

快来发表一下你的评论吧 !