FPGA原型验证中分割引擎的重要性解析

可编程逻辑

描述

随着后摩尔时代的到来,5G、AI、自动驾驶等众多热门应用不断涌现,芯片规模呈指数级增长,十亿门甚至几十亿门的芯片设计比比皆是,大芯片的验证效率问题已成为芯片设计公司的一大痛点。

在这样的背景下,FPGA(现场可编程门阵列)原型验证已发展为芯片公司不可缺少的验证方法。

Part 1

什么是FPGA原型验证?

FPGA原型验证,是基于FPGA的一种芯片功能验证方式。它利用了FPGA可以多次擦写的特性,在芯片RTL代码开发的过程中,将RTL代码综合到FPGA上来做芯片的功能验证。其目的是在芯片流片之前,为芯片开发团队提供一个可以反复迭代的逻辑验证平台。在芯片设计定型之后,流片回片之前,为软件开发团队提供一个可以提前开发软件功能的硬件环境,缩短芯片回片之后产品的上市时间。这个验证环境能够让芯片验证与软件验证并行,确保芯片软硬件功能在真实应用场景中准确无误。

Part 2

为什么要使用FPGA原型验证?

现代SoC芯片是一个软硬件协同运行的系统,上面有复杂的软件运行,帮助芯片实现各种功能。与芯片协同工作的软件系统,其设计、开发和验证工作需要和芯片设计验证工作同步展开。这样才能保证芯片功能正确,降低芯片流片失败的风险,缩短产品的上市周期。

为了保证芯片功能正确,在芯片RTL代码开发之后,需要经过一系列的验证流程。常见的数字芯片验证手段,包括逻辑功能仿真、形式化验证、硬件加速器和FPGA原型验证等。

这几种常见的数字芯片验证手段中,FPGA原型验证技术是最适合芯片软硬件协同功能的验证技术之一。FPGA原型验证平台可以提供调试芯片软件必要的真实物理接口和硬件环境。这是逻辑功能仿真和形式化验证无法提供的。

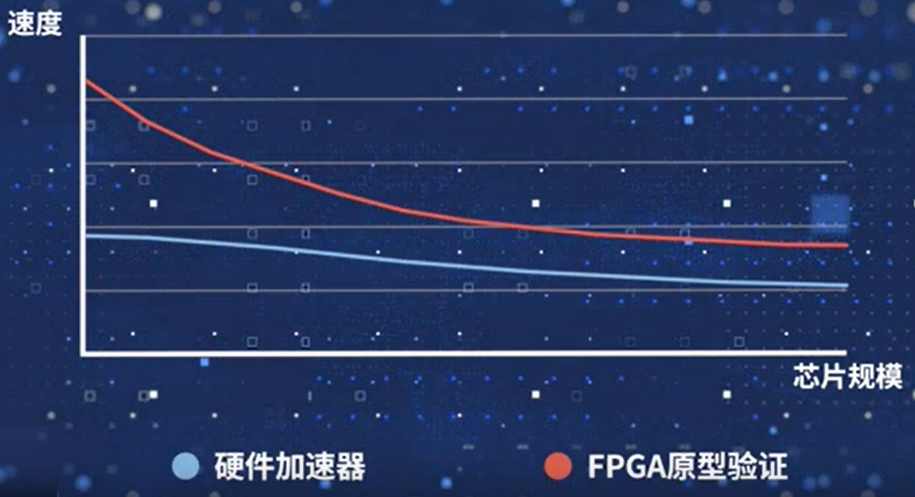

相比硬件加速器,FPGA原型验证平台的软件运行速度快一个数量级,局部或某些接口逻辑代码可以按照更接近真实芯片的频率运行,很大程度缩短了软件运行的调试时间和验证迭代的周期,同时也使得软硬件开发验证并行成为可能。在芯片验证流程中,FPGA原型验证技术是软硬件协同功能验证的必备解决方案,具有显著的不可替代性。

因此,FPGA原型验证技术,作为主流且成熟的芯片验证方法,已成为数字芯片公司不可或缺的验证工具。

Part 3

在FPGA原型验证中

为什么分割引擎非常重要?

FPGA原型验证的原理是将芯片RTL代码综合到FPGA上来验证芯片的功能。对于目前主流行业应用而言,芯片规模通常达到上亿门甚至数十亿门,一颗FPGA的容量难以容纳下芯片的所有逻辑功能。用户需要设法将大的设计分割为若干个小的部分,配置到多颗FPGA中,从而来实现整个设计的逻辑功能。

目前市场上大部分的FPGA原型验证平台,仍然是需要用户手动分割,需要花费很多精力并且容易出错。而领先的原型验证平台可以通过分割引擎来实现自动化分割,自动化分割引擎是否智能、高效,直接影响FPGA的资源分配和使用率、系统运行速度、编译时间以及迭代周期,从而进一步影响芯片产品的上市时间。

因此,合见工软在2022年6月推出了时序驱动全流程编译软件APS Compiler,配合高性能的UV APS原型验证系统,面对十亿门以上设计,可自动化快速实现更卓越的性能,很大程度降低用户的初期部署成本。

APS Compiler集成了业界领先的时序驱动引擎,可通过1:1024大范围的TDM Ratio自动寻求更优解,轻松处理多达100颗FPGA的设计容量,无论是性能还是自动化程度均可媲美业界前沿的同类工具。

那么APS Complier具体是如何实现高智能、全自动的呢?

Part 4

时序驱动全流程编译软件

APS Complier的三大特性

特性一:超大规模容量支持

当前芯片设计规模越来越大,这就要求FPGA原型验证平台的容量也足够大。APS Complier在架构设计之初,就考虑到了这种需求。我们的分割引擎采用业内创新的架构,通过时序驱动的分割算法,可以轻松支持百片FPGA规模的芯片设计分割任务。

特性二:运行速度大幅提升

由于主流芯片的设计频率很高,为了让原型验证平台尽可能和芯片性能接近,我们需要让FPGA原型平台保持在尽可能高的频率上运行,而这是由FPGA之间互联的路径决定的,这些互联一般以时分复用的方式来实现。

APS Complier集成了业内先进的全路径时序驱动分割引擎,与传统的Cut-size Driven的分割方式相比,它优势在于能够根据静态时序分析结果,自动识别并考虑每一条跨越FPGA互联的关键路径信号所在时钟域的频率和时序要求,实现快速迭代,优化FPGA之间的跳数,选择更优的时分复用比例,最终整体提升FPGA验证平台运行速度。

特性三:快速编译和迭代

随着FPGA规模不断加大,它需要的编译时间也不断增加。这导致FPGA布局布线的时间占据了FPGA原型验证平台编译的绝大部分时间。当出现资源使用率过高导致的拥塞和过高要求的时序约束时,编译时间更会大大拉长。

APS Complier可以根据时序约束要求和资源使用率设置,智能分割大规模芯片设计到多片FPGA上,优化和平衡每个FPGA内部的资源使用率和时序约束,达到更大化缩短每片FPGA编译时间的效果。

在迭代方面,我们知道SoC、ASIC验证过程中由于芯片设计迭代而常常带来模块增减,这导致原型验证中分割方案修改频繁。APS Complier支持自动分割模式,很大程度缩短了首次系统分割成功的时间。同时,它还支持用户向导的分割模式进行性能调优,并支持导入上次分割结果,很大程度缩短代码微调后的迭代时间,提高了工作效率和生产力。

编辑:黄飞

-

验证中的FPGA原型验证 FPGA原型设计面临的挑战是什么?2022-07-19 2509

-

简述FPGA原型验证系统中复制功能模块的作用2023-04-25 2719

-

高频RFID芯片的FPGA原型验证平台设计及验证2019-05-29 2847

-

高频RFID芯片的FPGA原型验证平台的设计及结果介绍2019-06-18 3825

-

ASIC设计-FPGA原型验证2020-03-19 2652

-

FPGA原型验证的技术进阶之路2020-08-21 4808

-

FPGA设计的验证技术及应用原则是什么2021-05-08 1266

-

LabVIEW FPGA 的重要性及应用2018-06-25 5326

-

了解PCB组装和原型设计的重要性2019-08-06 3462

-

如何建立适合团队的FPGA原型验证系统平台与技术?2023-04-03 2287

-

什么是FPGA原型验证?如何用FPGA对ASIC进行原型验证2023-04-10 2879

-

FPGA原型验证系统中复制功能模块的作用2023-05-04 1548

-

白皮书 I 基于组网分割的超大规模设计 FPGA原型验证解决方案2022-06-16 1495

-

什么是FPGA原型验证?FPGA原型设计的好处是什么?2024-01-12 2407

-

fpga原型验证流程2024-03-15 3530

全部0条评论

快来发表一下你的评论吧 !