高频同步降压变换器IS6608A使用攻略

电源/新能源

描述

产品指南

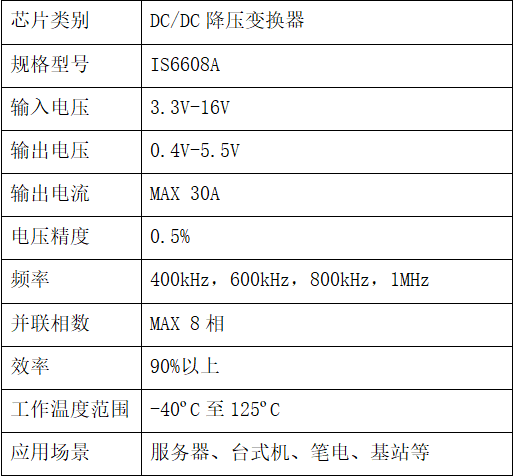

基本信息介绍

图 IS6608A的基本规格信息

IS6608A,国内首颗为CPU供电的多相并联电源芯片,是兼容 PMBusTM 接口的高频同步降压变换器。其采用4mm x 5mm FCQFN-25封装,在宽输入范围内每相可实现高达30A的输出电流,最多可支持8颗芯片并联实现峰值240A的输出电流。在大电流应用领域内,IS6608A可实现极好的电流共享和相位交错功能,可最大限度地减少现有标准外部元器件的使用。

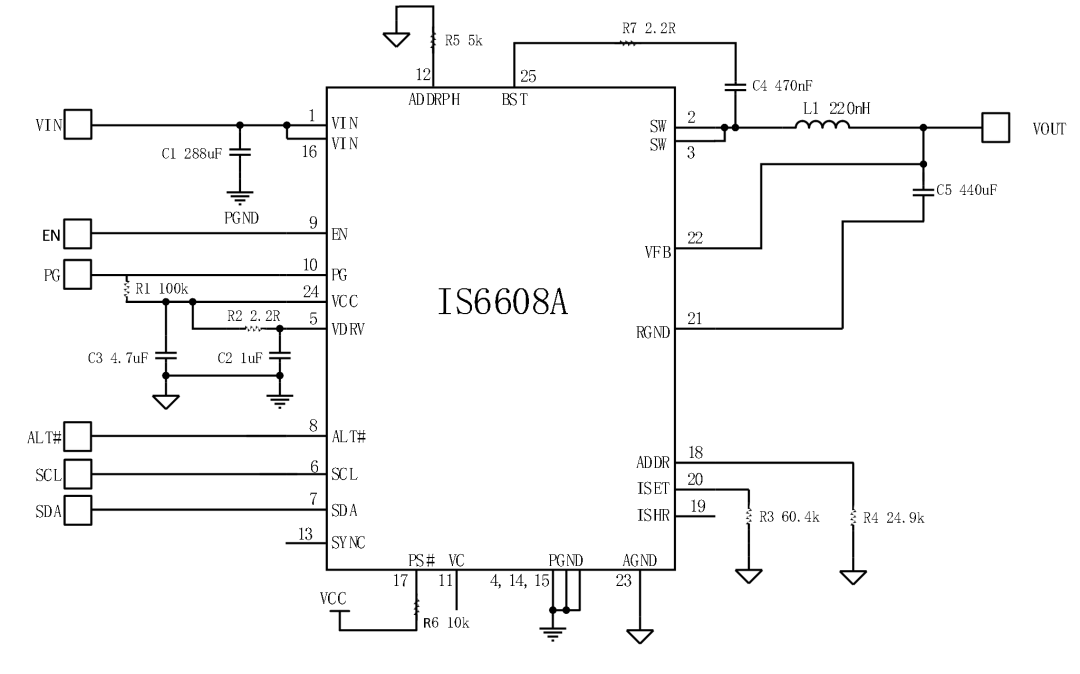

图 IS6608A典型电路图

IS6608A可以根据终端使用场景的多样化进行修改GUI、外围电路配置,为更加快速便捷帮助客户完成产品设计导入,本文章将系统阐述IS6608A的使用说明及布局建议,简单明了的向广大读者介绍该芯片在使用过程中的注意事项。

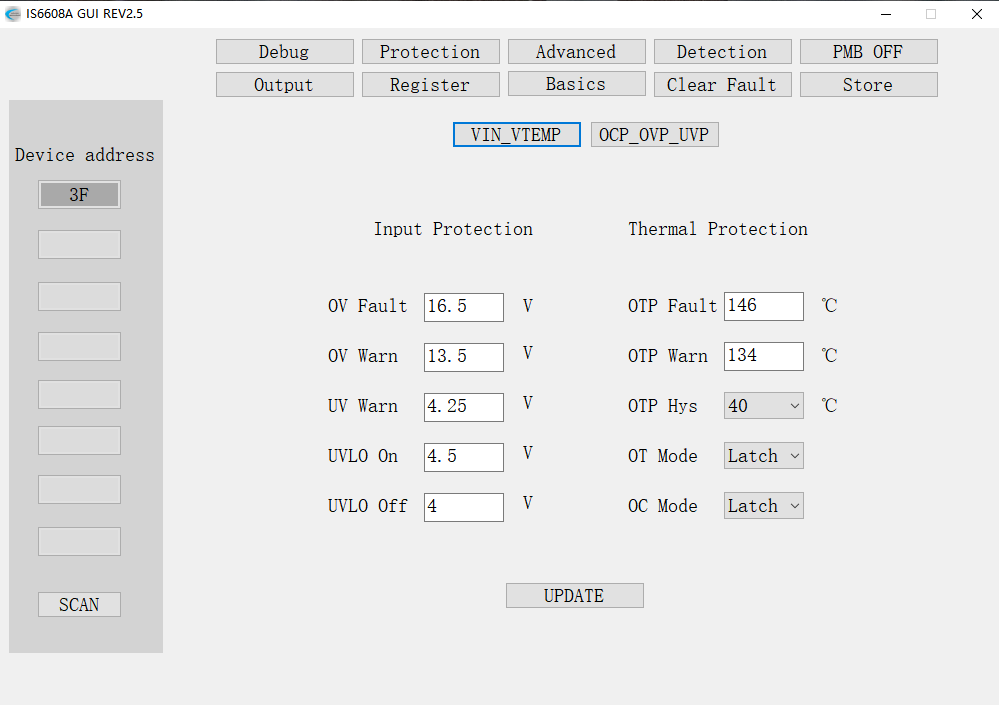

GUI使用说明

IS6608A GUI是长工微自主研发、用于配套IS6608A设计的图形用户界面软件工具,可以帮助用户更加快捷、直观地调试内部配置。IS6608A GUI遵循PMBUS协议,与IS6608A之间通过USB-to-I²C(dongle)进行交互。

图 IS6608A GUI 软件使用界面

1.GUI写入与烧录步骤

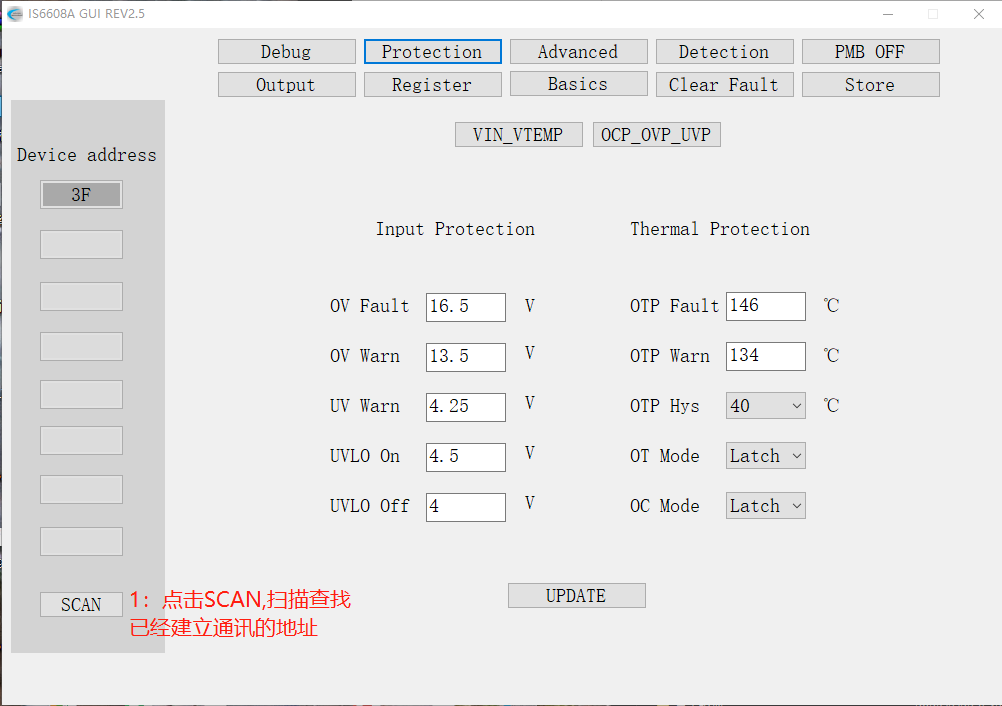

步骤1:点击SCAN,扫描查找已建立通讯的地址

步骤2:选择所需通讯地址

步骤3:选择所需操作分类

步骤4:在操作区中修改数据

步骤5:将修改后的数据写入芯片内

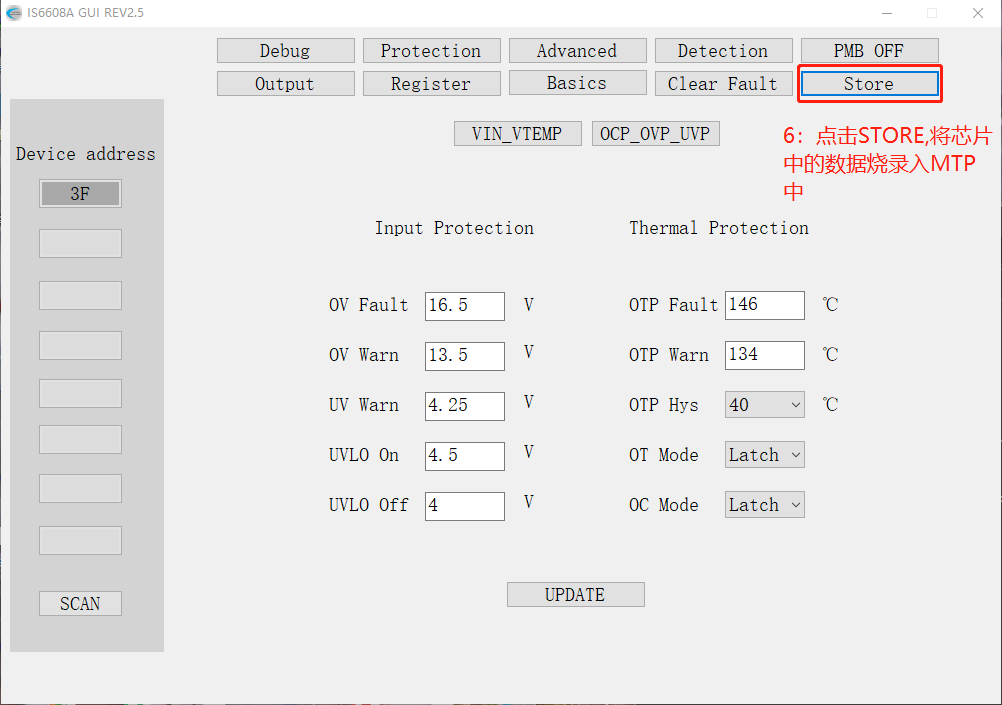

步骤6:点击STORE,将芯片的数据烧录入MTP中

More

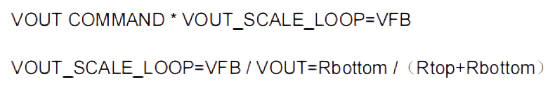

2.输出电压调整

VOUT COMMAND与VOUT_SCALE_LOOP用于设置VFB电压,公式为:

举例Rtop=2kΩ,Rbottom=6kΩ,VOUT=0.8V的应用,其输出电压步骤如下所示:

①根据Rtop=2kΩ,Rbottom=6kΩ,则VOUT_SCALE_LOOP=6kΩ/(2kΩ+6kΩ)=0.75;

②VOUT=0.8V,VOUT COMMAND=0.8V;

③点击UPDATE,将数据写入寄存器;

④点击Store,将寄存器中的数据存入MTP,此时VFB=0.8V*0.75=0.6V。

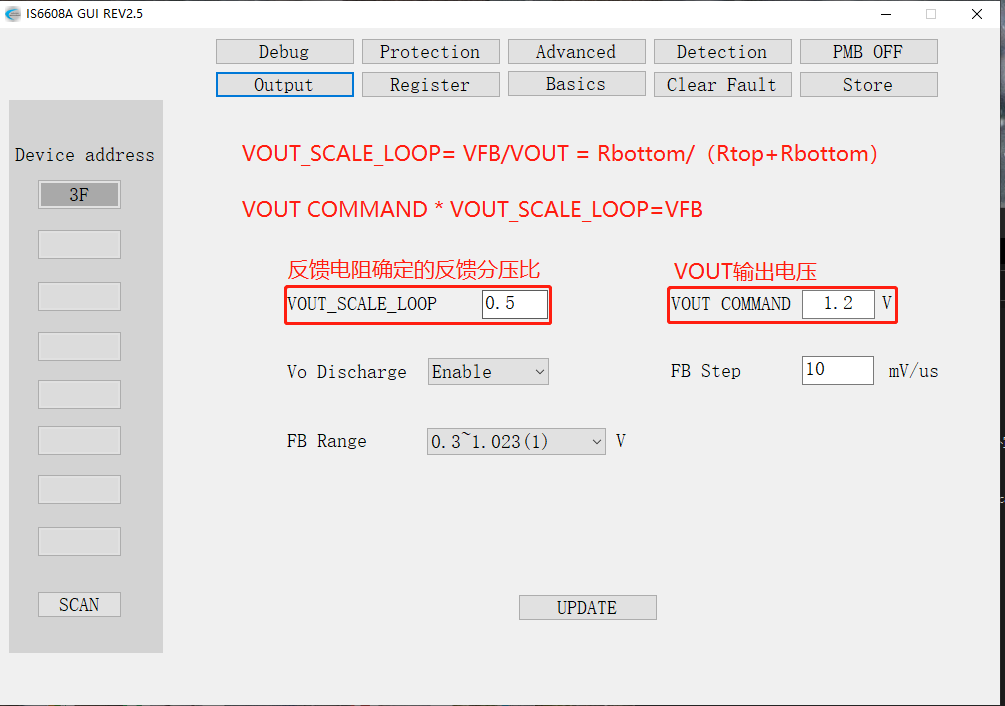

3.VOUT数值的读取

芯片中VOUT电压读取的实际读取数值为VFB电压,如果需要Detection中显示正确的输出电压,则需要将VOUT COMMAND与VOUT_SCALE_LOOP配置正确才可以显示正确数值。

举例Rtop=2kΩ,Rbottom=6kΩ,VOUT=0.8V的应用,其读取输出电压步骤如下所示:

①根据Rtop=2kΩ,Rbottom=6kΩ,则VOUT_SCALE_LOOP=6kΩ/(2kΩ+6kΩ)=0.75;

②VOUT=0.8V,VOUT COMMAND=0.8V;

③点击UPDATE,将数据写入寄存器;

④此时点击Detection,即可在GUI上读取到正确的VOUT电压。

注意:外部VFB分压电阻精度会影响VOUT读取的准确性。

IS6608A具备完善的保护功能,包括过流保护(OCP),负向过流保护(NOCP),过压保护(OVP),欠压锁定(UVLO)和过温保护(OTP)等其他保护机制,用来在发生故障或意外动作并造成异常时,保护芯片不被损坏。

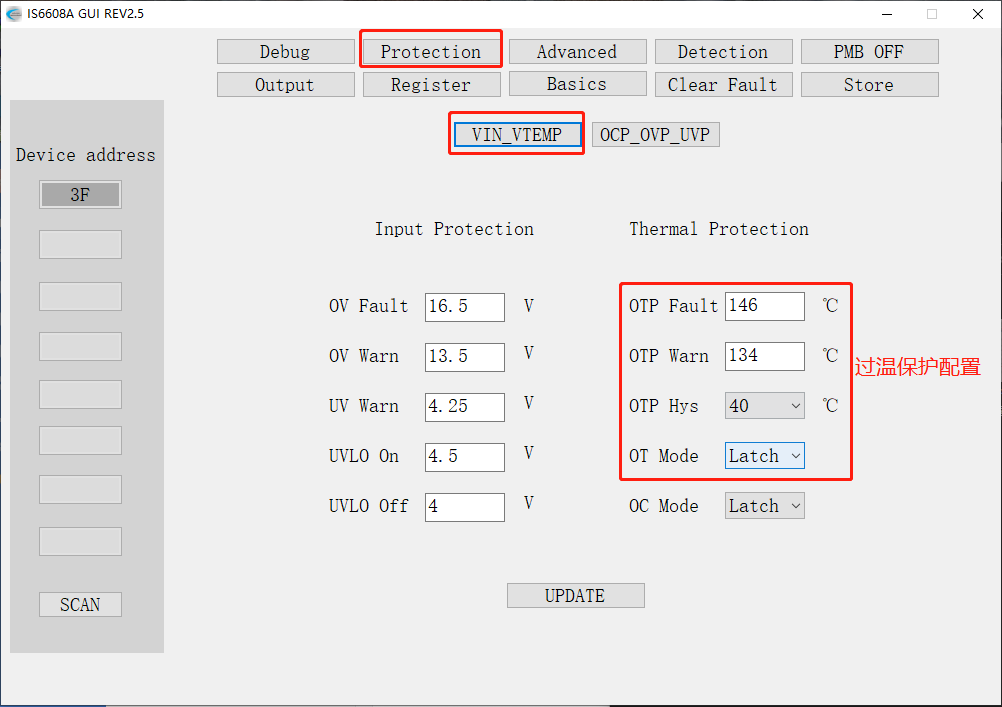

4.OTP保护模式设置

最新版本IC的OTP默认保护温度146℃,保护模式可在Latch和Retry【包括RETRY的迟滞温度】中选择,默认为Latch。下图为修改步骤:

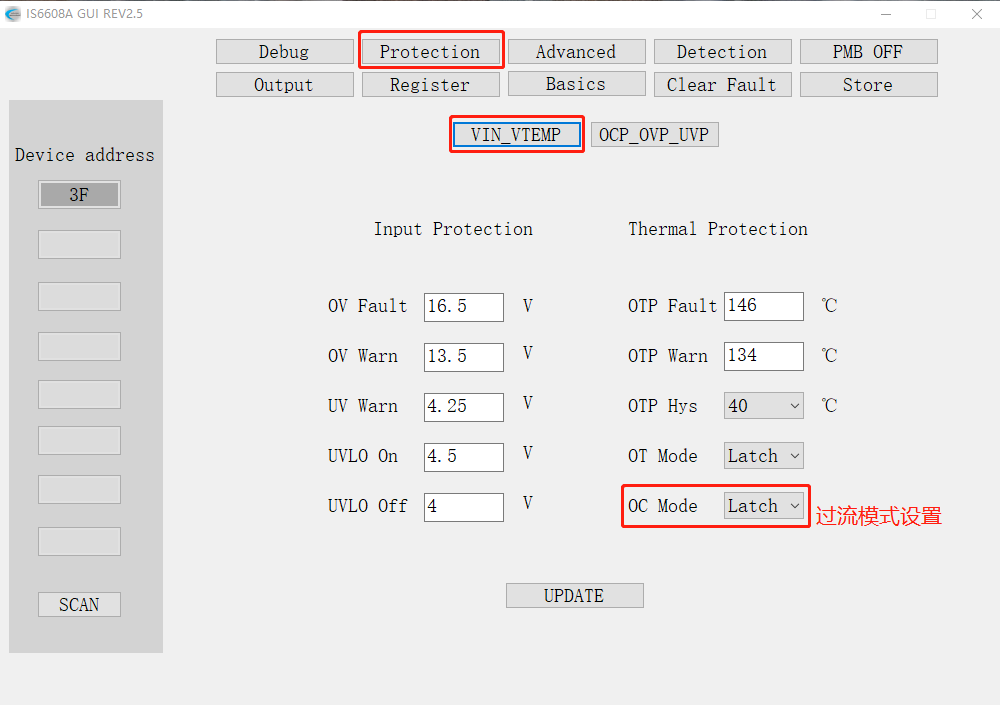

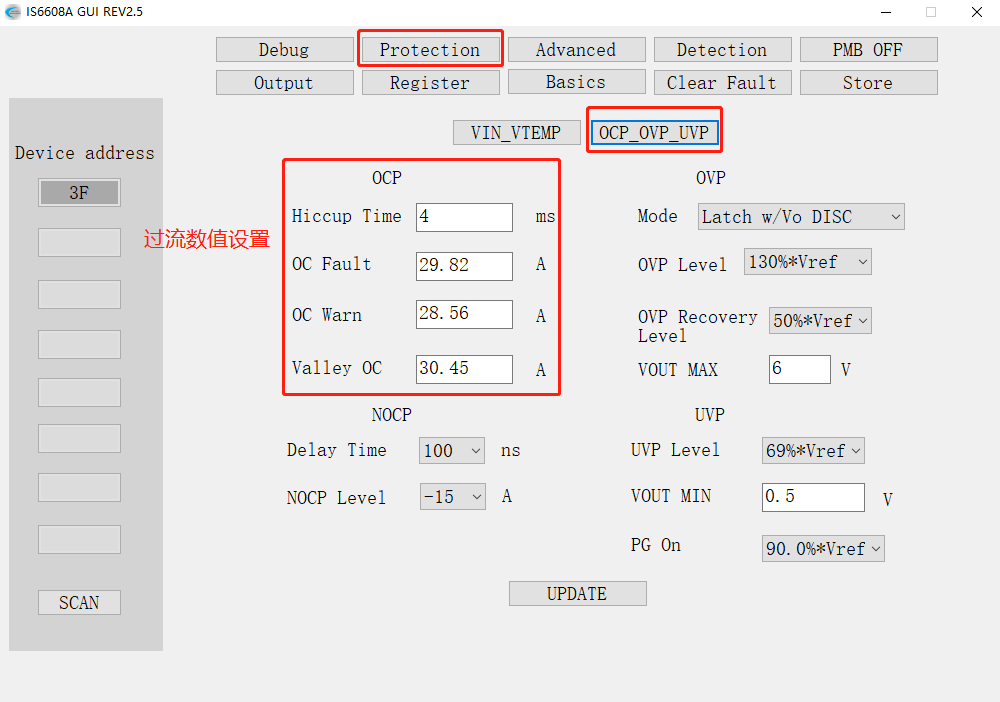

5.OCP保护模式的设置

默认DC保护电流32.66A,保护模式可在Latch和Retry【包括Retry的Hiccup Time】中选择,默认为Latch。下图为修改步骤:

More

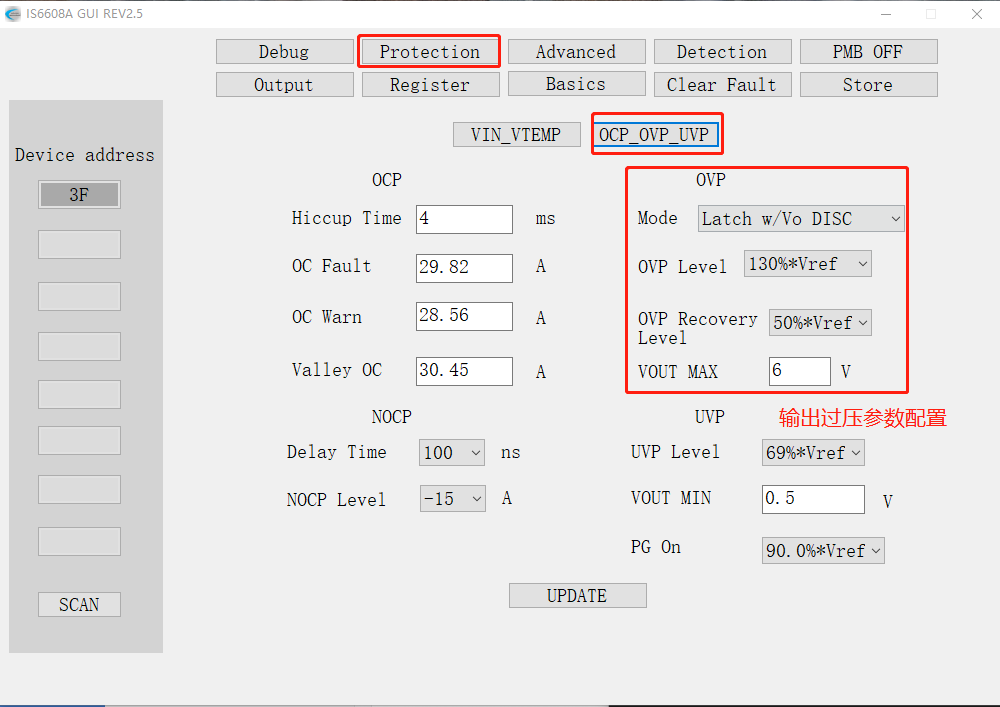

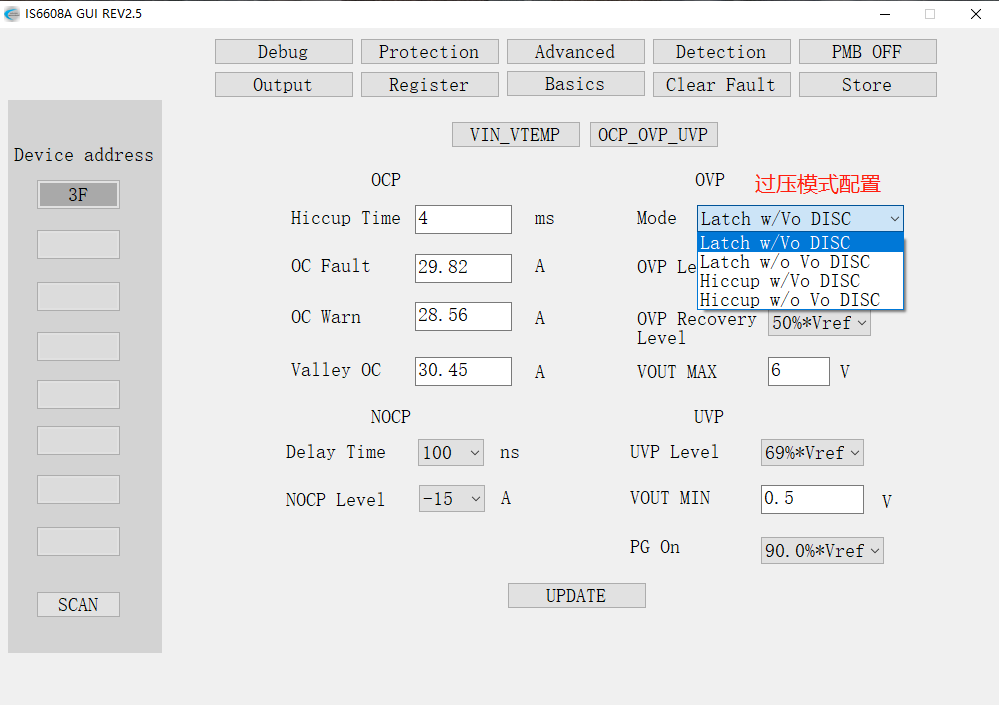

6.OVP保护模式的设置

默认过压保护值为130%*Vref,保护模式可在Latch和Retry【包括Retry的恢复电压和保护方式】中选择,默认为Latch。下图为修改步骤:

OVP共有4种响应方式可供选择,分别为Latch & Hiccup和w/Vo DISC & w/o Vo DISC,具体区分如下:

Latch:过压后掉电锁死,需手动重启;

Hiccup:触发过压保护后会下降至OVP Recovery Level 所设置电压后重新上电;

w/Vo DISC:当触发过压保护后,使用Vo Discharg功能将输出电压拉低;

w/o Vo DISC:当触发过压保护后,不使用Vo Discharg功能将输出电压拉低。

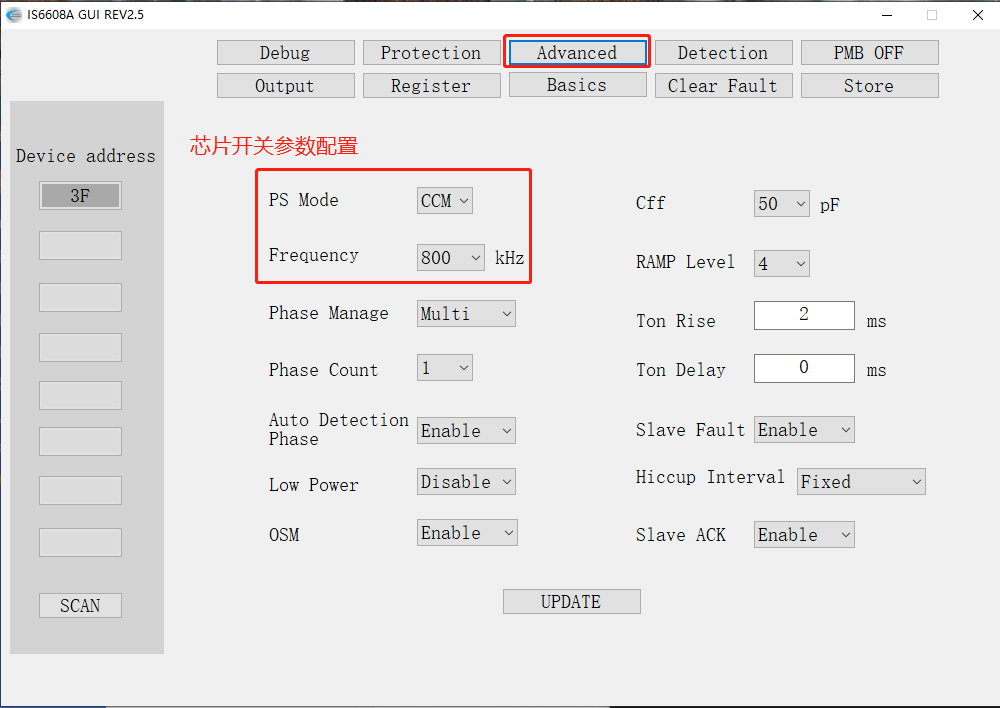

7.芯片工作频率和模式的设置

默认工作频率为800kHz,默认工作模式为FCCM,下图为功能设置所在分类:

走线/布局建议

IS6608A外围包含多种功能引脚配置,对IC走线和元件的放置有较高的要求。良好的外围走线/布局能有效地影响芯片的工作效率和稳定性,此外,外围电路还可以提供良好的电磁兼容性、降低噪声及抗干扰能力。

值得注意的是,在没有特定需求情况下,GUI不是用户使用IS6608A的必需品,但走线/布局是用户需重点注意的使用内容之一。走线/布局建议如下:

1.多相并联时每相ISHR引脚近端需要放3K电阻;

2.芯片正下方及芯片VIN/GND引脚近端/覆铜尽可能放置足够数量的VIA;

3.两个VIN引脚近端放置1uF 0402小电容滤波;

4.敏感走线【如VFB-RGND/SYNC/ISHR/VC】需要避开干扰信号【如SW/BST/VIN】放置;

5.BST回路尽可能短;

6.VCC/VDRV电容尽量靠近引脚同层放置;

7.ISET/ADDR/ADDPH电阻尽可能靠近引脚放置且需要使用1%精度电阻;

审核编辑:刘清

-

NB685 26 V,12 A,低静态电流,大电流 同步降压变换器数据手册2026-04-15 222

-

高频同步降压式DC-DC变换器数据手册2024-04-24 665

-

同步降压变换器 FP6188V071-G1规格书2021-12-02 1078

-

一种高效率的同步降压DC-DC变换器3A输出电流2021-11-17 1455

-

2A同步降压变换器芯片TX9416数据手册2021-06-25 1500

-

车载升降压DCDC变换器资料分享2021-05-12 2467

-

LTC3631:高效高压100 mA同步降压变换器产品手册2021-04-29 891

-

什么是四管同步升降压变换器?2019-09-16 4486

-

Fly-buck变换器及同步升压降压控制器的特点及应用分析 (1)2019-04-28 4631

-

新型高频降压变换器的工作模式介绍2019-04-11 3310

全部0条评论

快来发表一下你的评论吧 !