未来的晶体管会是什么样?

模拟技术

描述

未来的晶体管会是什么样?

在比利时安特卫普举行的ITF World 2023上,英特尔技术开发总经理Ann Kelleher概述了英特尔在几个关键领域的最新进展,最有趣的是英特尔将在未来采用堆叠CFET晶体管。这标志着英特尔首次在其公开演讲中展示这种新型晶体管,但Kelleher没有提供量产日期或确切的时间表。

在这里,我们可以看到幻灯片的放大版本,在新型晶体管周围增加了一个环。幻灯片底部的前两种晶体管类型是较旧的变体,而“2024”条目代表英特尔的新 RibbonFET 晶体管,我们过去已经广泛介绍了这些晶体管。英特尔的第一代设计采用“Intel 20A”制程节点,具有4个堆叠的纳米片,每个纳米片被一个栅极完全包围。Kelleher说,这种设计有望在2024年首次亮相。RibbonFET采用全环栅(GAA)设计,可同时提高晶体管密度和性能,例如更快的晶体管切换,同时使用与多个鳍片相同的驱动电流,但面积更小。

Kelleher的幻灯片还展示了下一代英特尔的GAA设计 - 堆叠式CFET(互补FET),该晶体管设计已经在imec的路线图上出现了一段时间,但我们还没有在英特尔之前的幻灯片上看到它,也没有听到该公司表示计划采用这种设计。imec研究所主要研究未来的技术,并与行业合作,使其开花结果。

当然,英特尔的风格化渲染和我们在上面第一张图片中包含的imec CFET渲染之间存在一些差异,但英特尔的图像很好地表达了一点 ——这种设计允许该公司堆叠8个纳米片,是RibbonFET使用的4个纳米片的两倍,从而增加了晶体管密度。在上面的图片中,还有另外三种类型的英特尔晶体管的图像——平面场效应管、鳍式场效应晶体管和带状场效应晶体管。

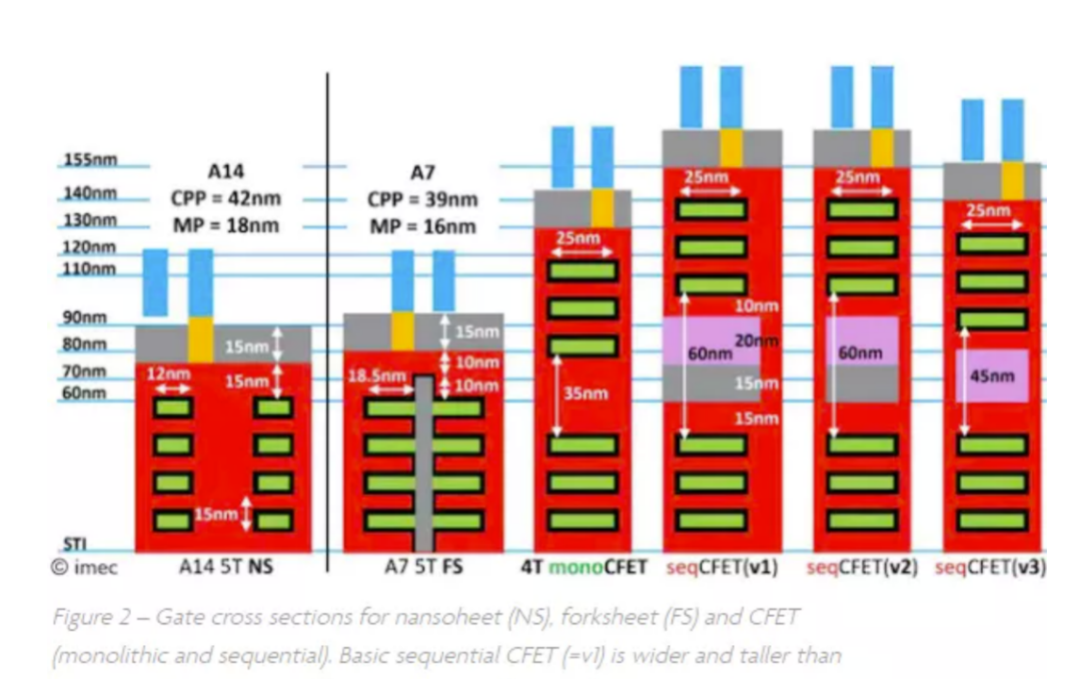

CFET晶体管将n和pMOS器件堆叠在一起,以实现更高的密度。目前正在研究两种类型的CFET——整体式和顺序式。上图右侧的四个器件详细介绍了各种建议的CFET设计。目前,尚不清楚英特尔将采用哪种类型的设计,或者是否会有新的设计类型。鉴于imec在其路线图上没有CFET,直到2032年芯片缩小到5埃时,我们可能需要一段时间才能找到答案。

也就是说,不能保证英特尔会在那个时间范围内瞄准CFET:有趣的是,英特尔的幻灯片显示了其下一代GAA纳米片晶体管(RibbonFET),然后直接跳到CFET,省略了GAA叉片晶体管,大多数人认为这将是纳米片和CFET之间的过渡。您还可以在上面的幻灯片中看到这种类型的晶体管,它是左起第二个。

由于英特尔的幻灯片不是很详细,该公司可能还计划在转向CFET之前使用叉片晶体管,但它尚未选择分享细节。我们正在跟进英特尔,看看我们是否可以了解更多细节。

Kelleher的演讲还涵盖了多个主题,包括随着时间的推移,每个晶体管支付的成本下降,晶体管可靠性随着时间的推移而提高,封装过程日益复杂,以及转向系统技术协同优化方法对英特尔设计工作的重要性。

Kelleher的演讲是在imec的ITF世界会议上进行的,她以回忆自己在imec的历史开始了她的演讲, 她大约在30年前第一次在imec工作,最终在该科研巨头工作了两年。英特尔与imec在过去30年中也有着长期的合作关系,这项工作一直持续到今天。

imec是世界上最重要的科研机构之一,您可以把imec想象成一个“硅瑞士”,某种意义上的。Imec是该行业进步的基石,将AMD、英特尔、英伟达、台积电和三星等激烈竞争对手与ASML和应用材料公司等半导体设备制造商聚集在一起,还有Cadence和Synopsys等关键半导体软件(EDA)设计公司。这种合作使各方能够共同定义下一代设备和软件的路线图,他们将用于设计和制造为世界发展提供动力的芯片。

审核编辑:刘清

-

晶体管诞生100周年时会是什么样?2023-03-21 1680

-

什么是达林顿晶体管?2023-02-16 2095

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 2567

-

未来的晶体管长啥样?2022-12-01 806

-

请问GTR的双晶体管模型是什么样的?2020-06-11 1108

-

晶体管简介2019-05-09 2268

-

晶体管的由来2019-05-05 2649

-

数字晶体管的原理2019-04-09 2540

-

晶体管的检测方法2016-02-23 871

-

晶体管性能的检测2012-04-26 2516

-

晶体管分类及参数2010-08-12 3350

-

未来环保汽车会是什么样?2010-04-07 2034

-

CMOS晶体管,CMOS晶体管是什么意思2010-03-05 4213

全部0条评论

快来发表一下你的评论吧 !