使用寄生建模软件了解和优化碳化硅功率PCB布局

描述

高功率 PCB 布局是艺术、科学和工程的平衡,以实现高性能设计,同时考虑与电压间隔相关的大量限制, 系统布局, 产品尺寸, 热要求, 以及最重要的电气性能.从历史上看,一个经验丰富的设计师如果很好地理解这些权衡,就可以在没有建模工具帮助的情况下提供可接受的设计。然而,在当今采用具有非常高dv/dt和di/dt的碳化硅(SiC)MOSFET的现代功率转换器设计中,了解和量化布局中的寄生效应至关重要。在采用并联 SiC MOSFET 的设计中尤其如此,其中 PCB 寄生电感和电容会对动态均流产生重大影响。是德科技的高级设计系统 (ADS) 和电力电子专业版 (PEPro) 等电路仿真工具能够从 PCB 布局中提取寄生元件并对其进行建模,从而可以在构建任何硬件之前进行设计优化,从而节省时间和金钱。Wolfspeed 与是德科技合作,分析了采用两个并联表面贴装 SiC MOSFET 的新型 Wolfspeed 评估板的行为,并比较了仿真和测量数据。

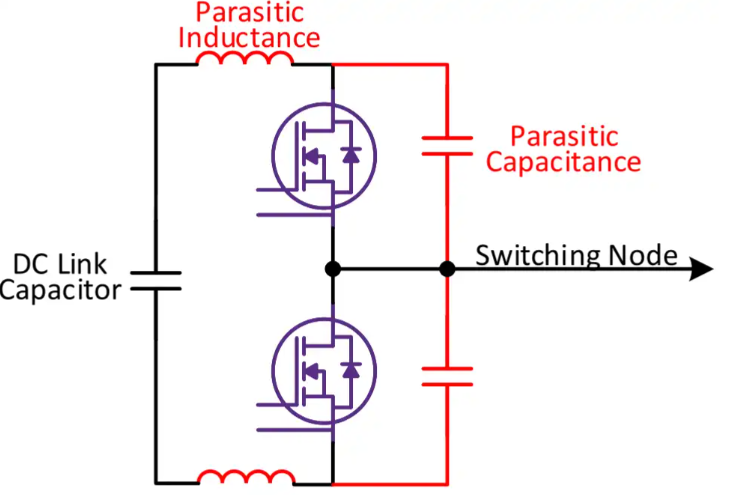

与硅 MOSFET 或 IGBT 相比,SiC MOSFET 的众多优势之一是,由于快速导通和关断开关边沿,大大降低了开关损耗。更快的开关时间可实现更高的系统效率和更高的功率密度,但在PCB布局中确实需要仔细注意,以最大限度地提高优势。在考虑寄生元件对系统性能的影响时,电源路径中有两个基本关注点。第一个是开关环路中的寄生电感,第二个是开关节点上的寄生电容。这些寄生元件在下面的图1中以红色显示。

图 1:带有红色寄生元件的简化半桥电路

寄生电感可能会导致几个问题,具体取决于应用。开关器件和直流母线之间的寄生电感会增加器件在关断时的电压过冲。PCB布局完成后,减少这种过冲的唯一方法是增加栅极电阻,以减慢SiC MOSFET的di/dt。这将导致开关损耗增加。更好的解决方案是了解并优化PCB布局,将寄生电感降至可接受的水平,以便以最佳方式驱动MOSFET。

开关节点与电路中其他点之间的寄生电容有可能增加开关损耗、损坏信号并增加EMI。开关节点和母线轨之间的电容会增加开关损耗,因为存储在寄生电容中的能量在开关事件期间消耗在MOSFET中。

在布线复杂的多层板上,很难直观地可视化所有寄生元件及其对电路操作的影响。如果在构建原型组件之前没有很好地理解寄生元件,则性能可能会受到影响。潜在布局问题的警告信号是:

关断时高压过冲

VDS 或V GS 振铃过多

开关损耗高于预期

并联器件中的动态均流失配

其中一些问题可能严重到足以导致立即设备故障或缩短系统的使用寿命。在原型阶段发现这些问题意味着您已经投入了大量的时间和金钱来订购、构建、测试和排除设计故障,而这些更改可能有效,也可能无效。虽然SPICE仿真器是设计和测试电路行为的有效工具,但它不考虑布局中的寄生效应。这就是,可以使用是德科技的 PEPro 等协同仿真工具对 PCB 进行布局后分析,并在订购任何硬件之前进行设计更改。PEPro 使用电磁 (EM) 场求解器来提取 PCB 布局寄生效应。上述潜在影响可以在这种类型的工具中看到,与花费数月时间构建和测试硬件原型相比,布局在数小时或数天内得到改善。

案例研究 – 并联 MOSFET

作为 Wolfspeed 新评估板 KIT-CRD-HB12N-J1 开发过程的一部分,Wolfspeed 和是德科技合作,使用是德科技 ADS 和 PEPro 对设计进行了分析,并将结果与实验室中的测量数据进行了比较。这项工作展示了如何使用是德科技 ADS 和 PEPro 仿真工具预测设计的实际行为,并利用这些信息来改进布局。

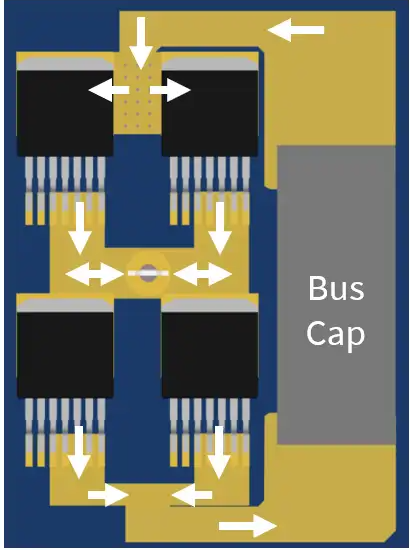

并联分立式 SiC MOSFET 可将设计的功率水平提高到 20-60kW 水平。为了充分利用并联MOSFET,这些器件需要几乎同时开关,并在导通时间内承载几乎相同的电流,以便它们具有相同的功率损耗。在理想系统中,两个MOSFET将使转换器可以处理的功率增加一倍。两个器件之间的任何损耗不匹配都需要将系统功率从理想值降低,以保持相同的峰值结温(TJ)。图2显示了两个并联器件的对称电源路径布局,这些器件配置为半桥拓扑,鼓励并联器件之间的均流。

图 2:并联半桥平衡布局示例可实现良好的均流

影响并联器件之间的损耗和温度平衡的因素有很多。第一个是MOSFET本身的参数(RDS(ON)VGS(TH)等),来自制造过程中的自然分布,设计人员无法控制。数据手册中提供了这些参数的范围,需要对设计进行一些降额,以解决并联器件之间潜在的不匹配问题。但是,设计人员可以控制的两个因素,即布局和冷却系统,可能会对并行器件之间的性能和平衡产生更大的影响。

许多碳化硅 MOSFET 参数与温度有关。即使并联设备的电气布局完美平衡,冷却系统也会引入不平衡。如果冷却系统由于热堆叠、流动不平衡或靠近其他热源而无法为所有设备提供相同的冷却,则设备将在不同的温度下运行。为了满足可靠性要求,设计人员必须限制转换器的操作,以将最热器件保持在应用所需的TJ以内,从而导致其他器件的利用率不足。

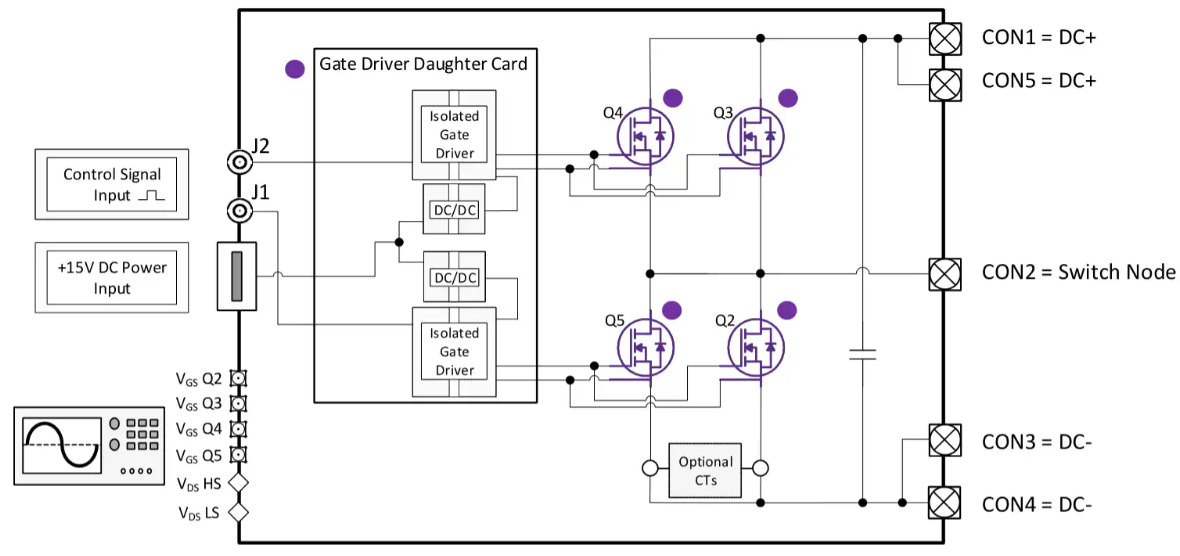

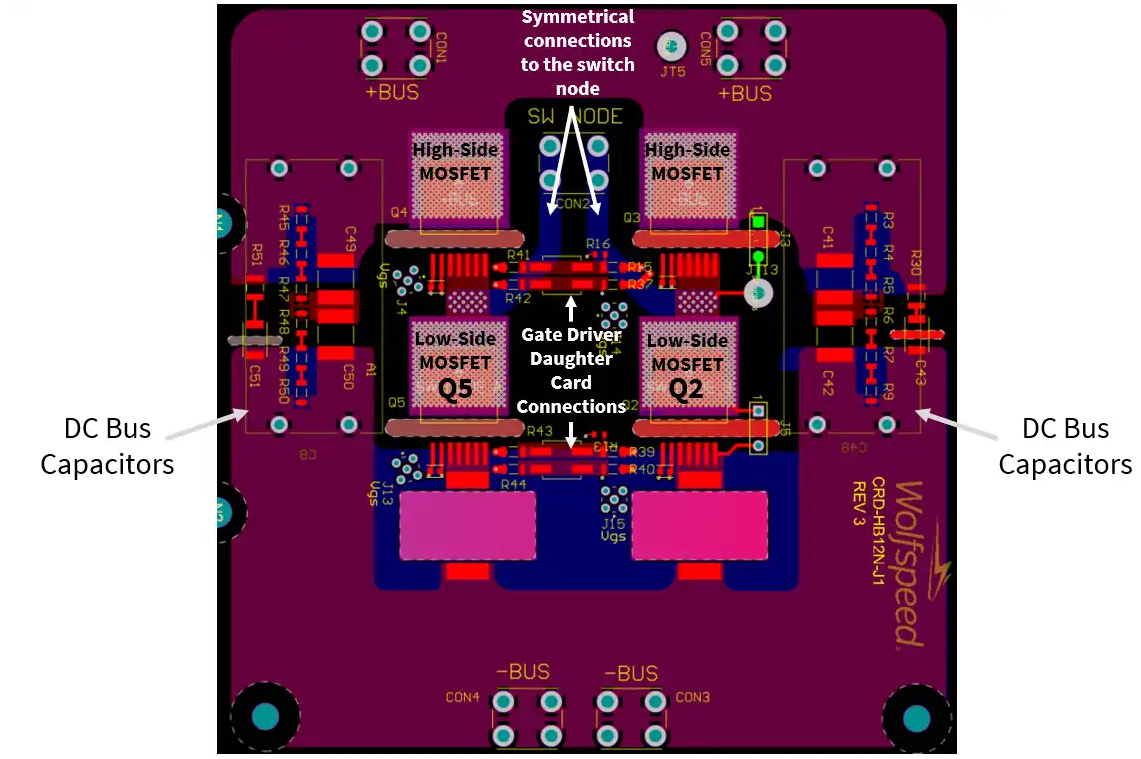

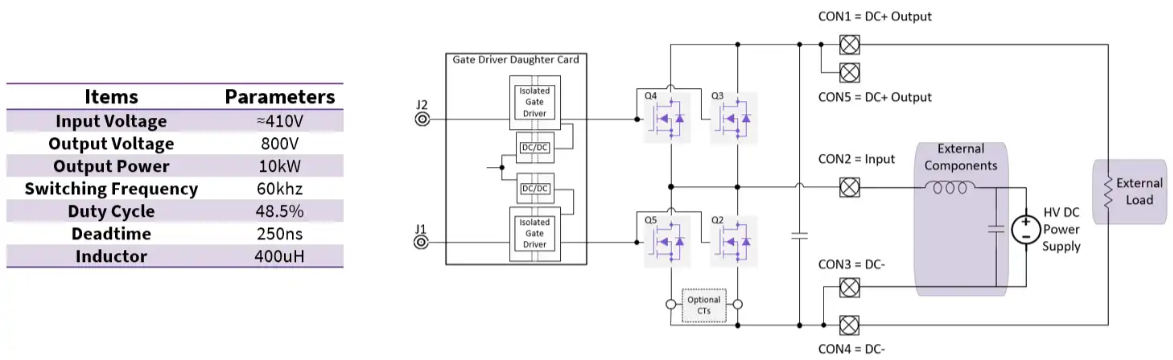

PCB布局是设计人员对设计拥有最多控制权的领域,因此对性能的影响是好是坏的能力也最大。正是在这里,是德科技的 PEPro 仿真工具可以有效地测试潜在布局、识别问题和快速开发解决方案。Wolfspeed 的 KIT-CRD-HB12N-J1 是一款半桥评估板,每个开关位置有两个并联的 MOSFET。该板使用子卡栅极驱动器。下图显示了电路板的框图原理图和电源部分布局的概述。

图 3a:KIT-CRD-HB12N-J1 评估板框图

图 3b:KIT-CRD-HB12N-J1 功率部分布局,显示 Q5 和 Q2 的对称性和位置

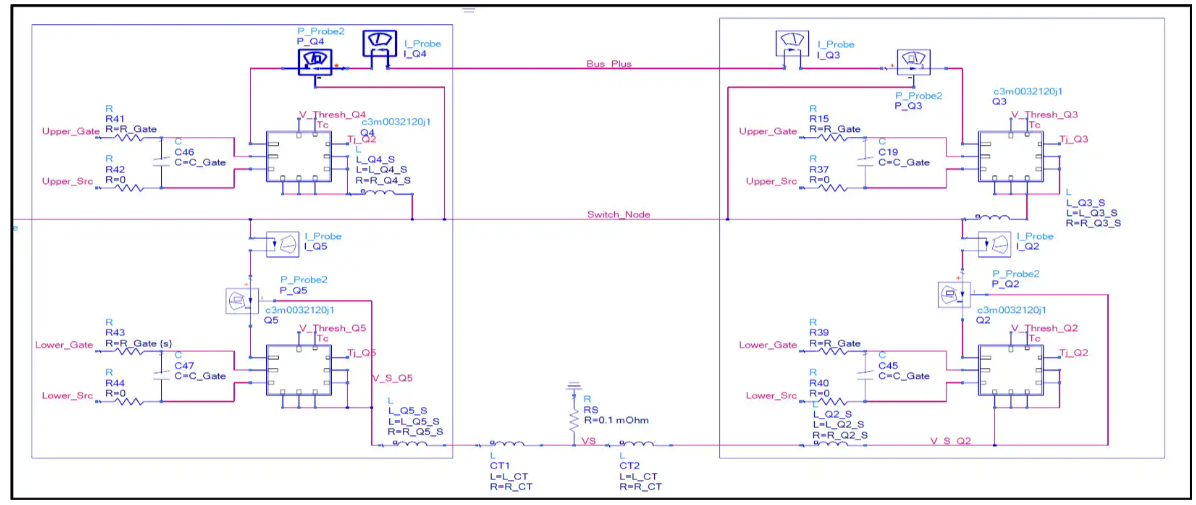

是德科技在该评估板上为电路的电源部分开发了一个 ADS 工作区。本练习未对低压和栅极驱动电路进行建模,因为重点是电源路径的对称性。

图 4:是德科技 ADS 工作区,显示 KIT-CRD-HB12N-J1 电源电路

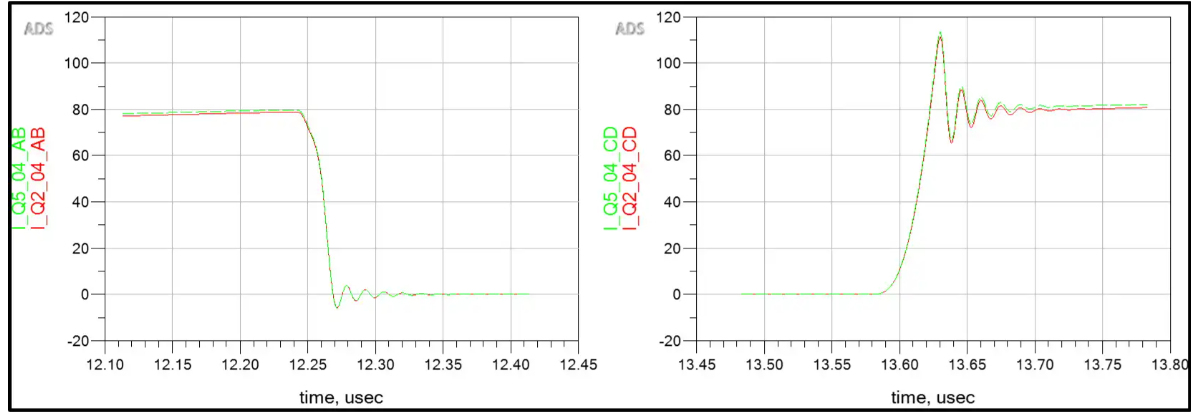

该评估板可用于在 SiC MOSFET 上执行开关损耗测量。每个并联MOSFET都有一个单独的电流传感器,因此可以分析每个器件的动态电流以检查均流。如果布局不对称,导致每个并联器件的寄生电感或电容不同,则两个器件之间导通和关断时的电流将不匹配。下面显示的是德科技仿真显示了两个并联的下部碳化硅MOSFET中的电流。从该仿真中可以清楚地看出,开关边沿两个器件之间的电流不匹配非常小。这表明两个设备的布局非常对称。

图 5:关断(左)和导通(右)时 Q2 和 Q5 中的仿真电流

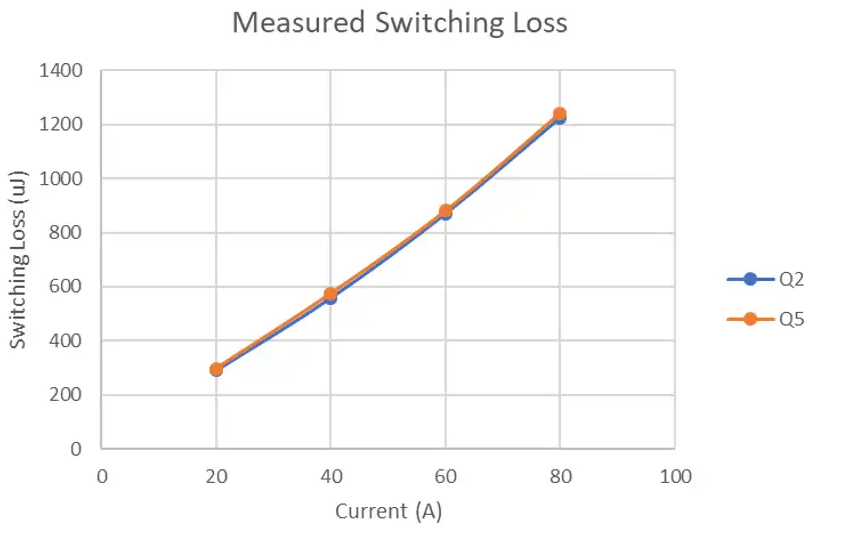

实验室的测量结果证实了模拟是正确的。这两个器件的开关损耗几乎相同,如下图所示。

图 6:在不同电流下测得的 Q2 和 Q5 开关损耗

接下来,在作为同步升压转换器运行的背景下分析该板,如下所示。

图 7:KIT-CRD-HB12N-J1 的同步降压转换器配置

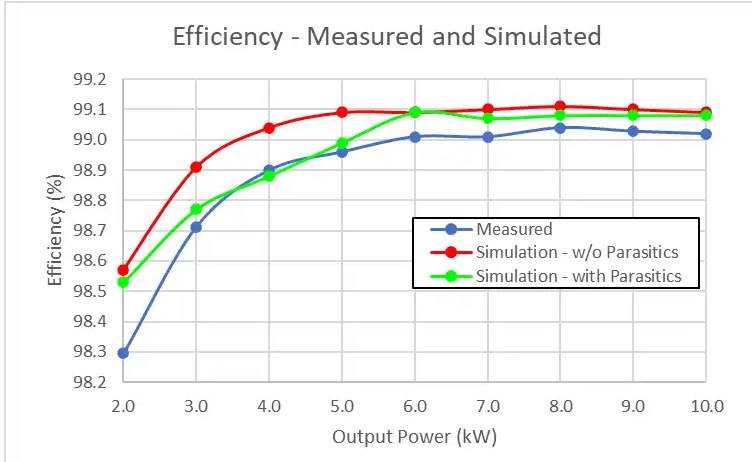

在对PCB的寄生元件进行建模和不对PCB寄生元件进行建模的情况下,对效率进行了仿真。不包含寄生元素的分析是SPICE模型本身所能做到的。如图所示,包括寄生元件会降低效率,并且模型更接近实验室中看到的测量结果。对于试图满足非常严格的效率要求的设计人员来说,这是一个重要的考虑因素。布局会对损失产生重大影响。

图 8:同步升压配置中的实测效率与仿真效率

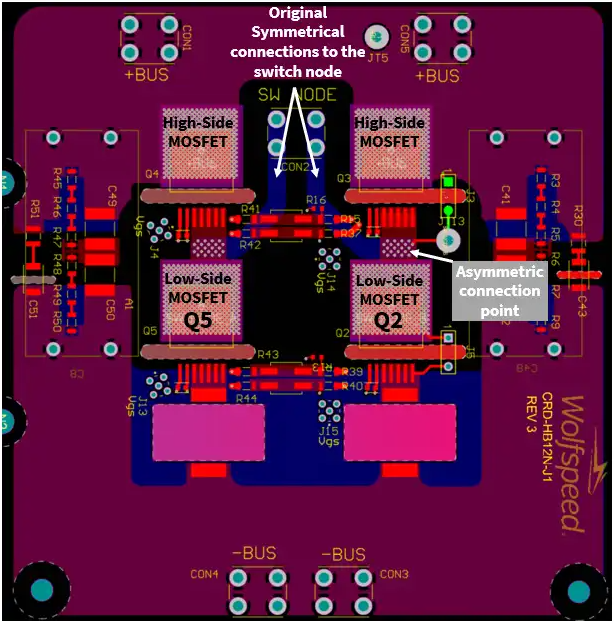

最后,进行了一次实验,有意在设计中引入不对称性,以查看对硬件和仿真的影响。在原始布局中,与升压电感的开关节点连接在两个并联支路之间对称。对于此测试,连接点移至Q2的漏极卡舌处,从而将电阻和电感降低到Q2,并将其增加到Q5。

图 9:有意引入的非对称交换节点连接

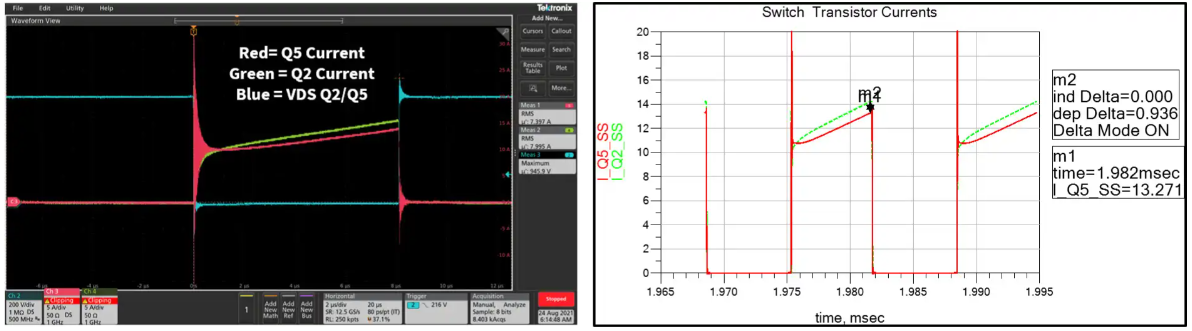

这种不对称导致第二季度的损失增加。对Q2电阻的增加会导致更多的电流在导通时间内流过Q5,从而导致更高的传导损耗。在测试的场景中,Q2故意具有比Q5更低的VGS(TH),因此尽管布局不对称,但Q2仍然更早开启并占用更多的动态电流。是德科技 ADS 能够捕获这两种现象,并且与测量的实验室数据非常吻合。

图 10:采用非对称连接的 Q2 和 Q5 中测量(左)和仿真(右)电流波形

像这样的不对称性通常被放置在设计中,以满足其他设计目标,例如连接点的位置。然而,正如是德科技 ADS 所证明的那样,这可能会对设计性能产生重大影响。使用这样的工具可以帮助设计人员了解设计中的所有权衡,并避免在测试阶段出现意外。

结论

碳化硅MOSFET和二极管为更高效、功率密度更高的设计打开了大门,这在很大程度上是因为它们的快速开关能力。然而,随着开关速度的提高,设计人员越来越需要了解布局中的寄生元件,这些元件会对性能产生重大影响。将电磁建模与 SPICE 建模相结合,可以更全面地了解功率转换器的行为。这些工具可以避免较长的原型设计周期,并优化系统的整体性能,从而缩短设计时间。

审核编辑:郭婷

-

碳化硅MOS驱动设计与PCB布局方法解析2022-03-24 14309

-

碳化硅压敏电阻 - 氧化锌 MOV2024-03-08 8405

-

碳化硅的历史与应用介绍2019-07-02 5055

-

碳化硅深层的特性2019-07-04 6096

-

碳化硅半导体器件有哪些?2020-06-28 4434

-

碳化硅基板——三代半导体的领军者2021-01-12 4439

-

碳化硅器件是如何组成逆变器的?2021-03-16 2828

-

什么是碳化硅(SiC)?它有哪些用途?2021-06-18 9406

-

碳化硅的应用2021-08-19 3981

-

传统的硅组件、碳化硅(Sic)和氮化镓(GaN)2021-09-23 6168

-

功率模块中的完整碳化硅性能怎么样?2023-02-20 9408

-

归纳碳化硅功率器件封装的关键技术2023-02-22 2952

-

浅谈硅IGBT与碳化硅MOSFET驱动的区别2023-02-27 3021

-

在开关电源转换器中充分利用碳化硅器件的性能优势2023-03-14 2886

-

碳化硅功率模组有哪些2023-05-31 1225

全部0条评论

快来发表一下你的评论吧 !