多片FPGA原型平台中的启动同步研究

可编程逻辑

1397人已加入

描述

假如给定FPGA内的时钟没有正确运行,那么我们多片FPGA系统的整体将不能同时启动,这将有可能是致命的。

我们还必须确保所有FPGA主时钟在释放复位之前都在运行,因为由于模拟电路(PLL和MMCM是模拟器件)的相关效应,并非所有时钟生成模块(MMCM、PLL)都可以同时锁定并准备就绪。

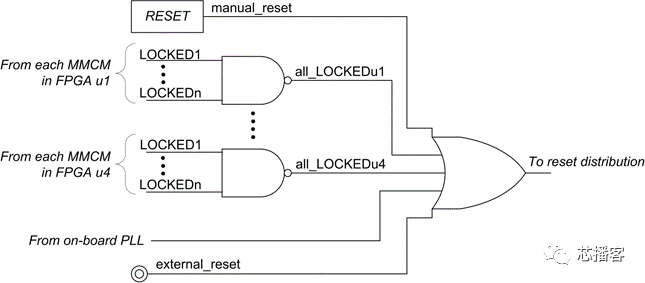

因此,需要构建一个reset复位的条件树。这可以通过添加一个如图所示的小电路来实现,该电路将分布在FPGA上。

每个FPGA中都有一个NAND功能,用于仅从我们设计中激活的MCMM中选通锁定信号。这将是一个组合函数,或者仅由独立于MMCM输出的自由运行的时钟确定。

然后,每个FPGA将其组合的all_LOCKED信号馈送到主FPGA,在主FPGA中对其进行“或”运算,以驱动复位分配树。

该原型中使用的任何板载PLL的锁定信号也必须选通至主复位,并且可能存在与时钟无关的其他条件在释放复位之前,这也必须为真,例如,外部仪器准备就绪的信号,当然,还应包括用户的“按钮”复位。默认这些都是高电平活动的,但当然,复位门可以处理任何组合。

整个树将用RTL编写,RTL被添加到FPGA版本的顶层芯片支持块中,可以使用复制来简化其分区。仅当满足所有系统范围就绪条件时,才释放全局复位。然后,复位也将在同一时钟边缘释放各个FPGA中的所有时钟分频器,以便所有除以n的时钟将在所有FPGA中同步。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

什么是FPGA原型验证?FPGA原型设计的好处是什么?2024-01-12 2405

-

多片FPGA原型验证的限制因素有哪些?2023-06-19 1288

-

多片FPGA原型的两种分割方式介绍2023-06-13 973

-

一文掌握多片FPGA的多路复用2023-06-06 2390

-

正确认识原型验证多片FPGA自动分割工具2023-05-23 1109

-

如何将这些SoC的逻辑功能原型正确的移植到多片FPGA中?2023-05-10 776

-

FPGA原型系统装配文件:Assign Traces介绍2023-05-08 964

-

多台FPGA原型验证平台可自由互连2023-04-11 1874

-

FPGA原型平台到底能跑多快呢?2023-04-04 3434

-

FPGA原型验证的技术进阶之路2020-08-21 4807

-

如何利用FPGA研究设计平台为网络发展加速?2019-08-27 2228

-

高频RFID芯片的FPGA原型验证平台设计及验证2019-05-29 2847

-

多片AD9910同步不了2018-11-20 3867

全部0条评论

快来发表一下你的评论吧 !