HC89S003AF4/HC89S001AJ4 20/8 引脚 8 位 ADC 型 FLASH 单片机 外设功能引脚全映射

电子说

描述

HC89S003AF4/HC89S001AJ4是一颗采用高速低功耗 CMOS 工艺设计开发的增强型 8 位单片机,内部有 16K Bytes FLASH 程序存储器,256Bytes IRAM+768Bytes XRAM,最多 18 个双向 I/O 口,5 个 16 位定时器 /计数器,3 组 12 位带死区控制互补 PWM,1 路 8 位 PWM,2 个 UART,1 个 SPI,1 个 IIC,16 个外部 中断,16+2 路 12 位 ADC,1 个低压检测模块,四种系统工作模式和多个中断源。

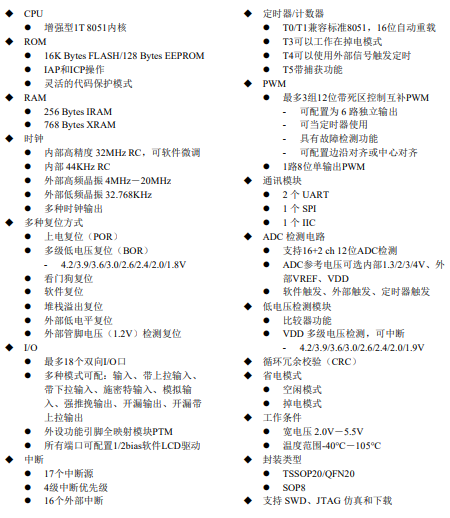

特点→

V:runzexin-18

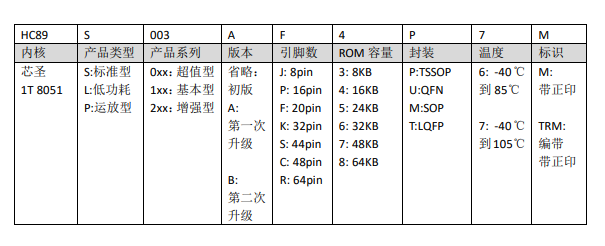

命名规则

1. 为保证系统的稳定性,必须在VDD和GND之间接一电容(容值须大于或等于0.1μF)。

2. 可以直接烧录HC89S003F4的烧录文件,但需要将HC-PM51烧录器的固件版本升级到最新版。

3. P2.7引脚出厂时默认为复位管脚,端口模式为施密特输入带上拉,可以通过配置代码选项将此口配 置为普通IO引脚。

4. 在进行IAP操作时,不响应任何中断。

5. ADCEN 置 1 或切换转换通道后,建议延时 20us 后再启动 ADC 转换,如果外部输入阻抗很大时, 需要延长这个时间。

6. 当 ADC 的参考电压为 VDD 时,ADC 转换时钟可以为 8MHz,一次转换只需要 15 个 ADC_CLK, 这样可以得到最快的 ADC 转换速度。

7. P2.7、P2.5、P2.4、P2.3 这四个端口的模式配置和其他端口的不一样,请仔细看 7.4.6 小节。

8. 使用 PWM3 时,要先配置时钟分频、周期、占空比等寄存器,最后再使能 PWM3 模块。

9. UART2 在使用全双工时,需要配置 CPU 频率为 16MHz 以上,波特率配置 9600 或以下,而且在 UART2 中断服务函数里尽早清零 TI 或 RI,请参考相关例程。

10. 在LVD中断中,若要关闭比较器或LVD中断,应先禁止 LVD/比较器,再失能LVD中断允许位。

11. 在使用LVD比较器功能的时候,如果比较器输出状态(CMPSTA)为高(即比较器正端电压大于负 端电压),则芯片无法进入掉电/空闲模式。

12. QFN20 的封装片中间的焊盘是与 PIN5(VDD)相连接的。

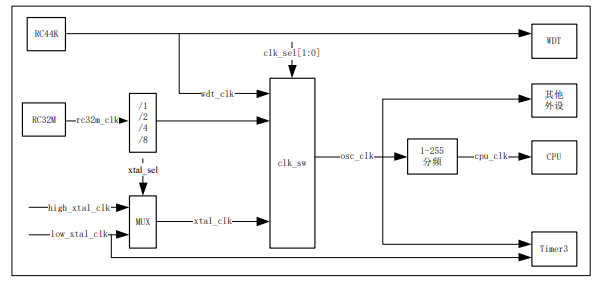

HC89S003A/001A 单片机系统时钟有 4 种时钟源可选:

➢ 外部高频晶振时钟(4MHz~20MHz)

➢ 外部低频晶振时钟(32.768KHz)

➢ 内部高频 RC 时钟(32MHz)

➢ 内部低频 RC 时钟(44KHz)

用户选择后的系统时钟(如果选择的是内部高频 RC,则经 RC32M_DIV[1:0]分频后的时钟)记做 osc_clk,其频率为 Fosc,周期为 Tosc,主要用于外设模块,osc_clk 可以进行 1-255 之间任意值的分频, 分频后的时钟记做 CPU 时钟,其频率为 Fcpu,周期为 Tcpu。

芯片上电复位后,默认选择内部高频 RC 作为系统时钟,其 Fosc 为 4MHz,Fcpu 为 2MHz,可以通过 配置相关寄存器改变 osc_clk 和 cpu_clk 的频率。

CPU 最高可以运行在 16MHz 频率下,如果所选时钟源频率高于 16MHz,需要对其进行分频,使 CPU 时钟频率等于或低于 16MHz。

系统时钟框图

本文章仅展现了产品一部分内容 具体内容可咨询。

审核编辑 黄宇

-

芯圣电子HC89S003A系列MCU简述2023-09-20 2943

-

芯圣电子兼容STM8S系列8051MCU——HC89S103K6T62023-08-03 1900

-

芯圣HC89S001A数据手册8位ADC型FLASH2023-07-26 691

-

HC89F3421B 引脚 8 位 Touch+ADC 型 FLASH 单片机 外设功能引脚全映射2023-05-23 1915

-

芯圣HC89F03xx数据手册8位ADC型FLASH2022-09-16 1041

-

芯圣电子兼容STM8S003的王牌选手-HC89S003A系列2022-09-15 4103

-

HC89S003多路ADC采样代码分享2021-12-07 1525

-

HC89S003F4P6增强型FLASH 8位单片机兼容STM8S0032021-11-16 1998

-

HC89S001P高速低功耗增强型8位单片机2018-11-13 6568

-

at89s52单片机引脚图,at89s52引脚说明2009-04-29 80627

全部0条评论

快来发表一下你的评论吧 !