Zynq UltraScale+ RFSoC器件介绍

描述

介绍一下Xilinx公司的新一代Zynq UltraScale+ RFSoC器件,可用于LTE、5G、SDR、卫星通信等无线平台。

Zynq UltraScale+RFSoC系列将多频带、多模蜂窝无线电和电缆基础设施(DOCSIS)的关键子系统集成到SoC平台中,该平台包含一个功能丰富的64位四核Arm Cortex -A53和基于Arm Cortex- R5F的双核处理系统。

将处理系统与UltraScale架构可编程逻辑、RF- ADC、RF- DAC和软决策FECs相结合,Zynq UltraScale+ RFSoC家族能够实现完整的软件定义无线电(SDR),包括直接射频采样数据转换器,在单个、高可编程SoC上实现CPRI和千兆以太网到射频。

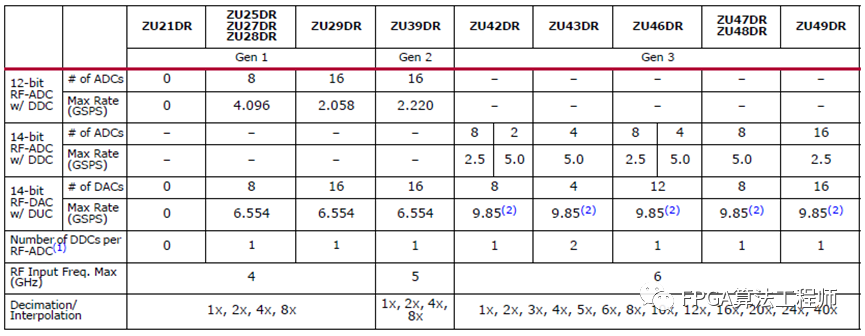

三代ZynqUltraScale+ rfsoc集成了多达16个通道的RF - ADC和RF - DAC,均具有优良的噪声谱密度。RF数据转换器还包括功率高效的数字下转换器(DDC)和数字上转换器(DUC),其中包括可编程插补和抽取、NCO和复杂混频器。DDC和DUC也支持双频操作。关键特性和采样率见表1。

表1 射频数据转换器子系统特性

软判决FEC(SD-FEC)是一种高度灵活的前向纠错引擎,能够在Turbo解码模式下运行,适用于无线应用,如5G无线、回程和DOCSIS 3.1电缆调制解调器中使用的LTE和LDPC编码/解码模式。

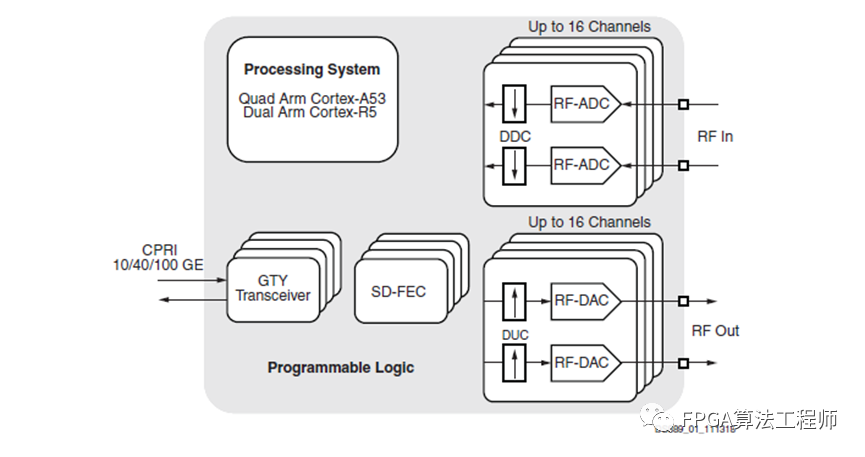

Zynq UltraScale+ RFSoC关键组件

图1 Zynq UltraScale+ RFSoC

特性总结

RF 数据转换器字系统概述

大多数ZynqUltraScale+ RFSOC都包含一个射频数据转换器子系统,其中包含多个射频模拟数字转换器(RF-ADC)和多个射频数字模拟转换器(RF-DAC)。高精度、高速、高效的RF - ADC和RF - DAC可单独配置用于实部数据,也可成对配置用于实部和虚部I/Q数据。

Soft Decision Forward Error Correction (SD-FEC)概述

一些ZynqUltraScale+ RFSOC包括高度灵活的软判决FEC块,用于解码和编码数据,作为在不可靠或有噪声的通信信道上控制数据传输错误的手段。SD-FEC块支持低密度奇偶校验(LDPC)解码/编码和Turbo解码,用于5G无线、回程、DOCSIS和LTE应用。

处理器系统(PS)概述

Zynq UltraScale+RFSOC具有四核Arm Cortex-A53 (APU)和双核Arm Cortex-R5F (RPU)处理系统(PS)。支持处理器的功能,大量的外围设备和专用功能都包含在PS。连接到外部数据或配置存储记忆,PS包括一个多协议动态内存控制器,DMA控制器,NAND闪存控制器,SD / eMMC控制器和一个四SPI控制器。除了与外部存储器接口外,APU还包括1级(L1)和2级(L2)缓存层次结构;RPU包括L1缓存和紧耦合内存子系统。每个芯片都可以访问一个256KB的片内存储器。

对于高速接口,PS包括4个通道的发送(TX)和接收(RX)对收发器,称为PS- GTR收发器,支持高达6.0Gb/s的数据速率。这些收发器可以接口到高速外设块,支持PCIe在5.0GT/s (Gen2)作为根复合或端点在x1, x2,或x4配置;串行ATA (SATA) 1.5Gb/s, 3.0Gb/s,或6.0Gb/s的数据速率;和多达两个通道的DisplayPort在1.62Gb/s, 2.7Gb/s,或5.4Gb/s的数据速率。PS-GTR收发器还可以通过USB 3.0和串行千兆媒体独立接口(SGMII)与组件接口。

对于一般连接,PS包括:一对USB 2.0控制器,可以配置为主机、设备或on - go (OTG);一个I2C控制器;一个UART;和符合ISO11898-1的CAN2.0B控制器。还有4个三速以太网MAC和128位GPIO,其中78位通过MIO和96位通过EMIO可用。基于ARM AMBA AXI4协议的高带宽连接将处理单元与外设连接起来,并提供PS和可编程逻辑(PL)之间的接口。

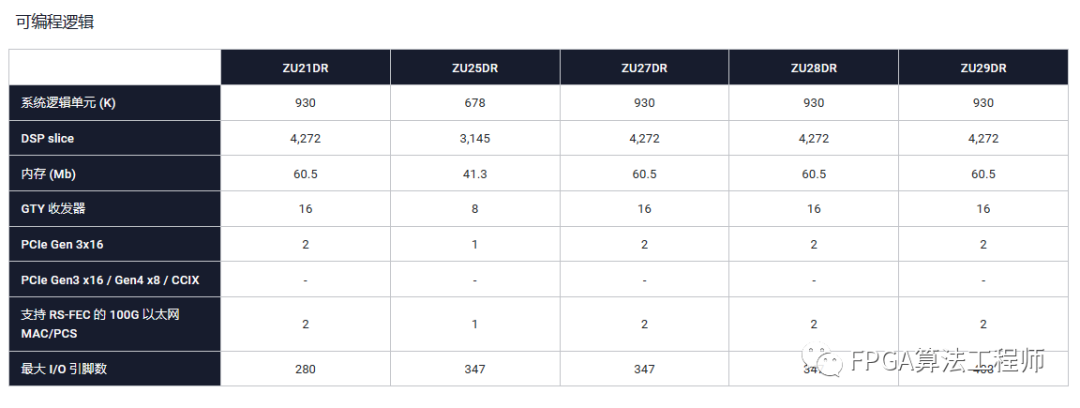

I/O, Transceiver, PCIe, 100G Ethernet, and 150G Interlaken

数据通过高性能并行SelectIO接口和高速串行收发器连接的组合在芯片上和芯片外传输。I/O块通过灵活的I/O标准和电压支持提供对尖端内存接口和网络协议的支持。基于UltraScale架构的设备中的串行收发器传输数据最高可达28.21Gb/s,实现25G+背板设计,比上一代收发器的每位功耗显著降低。除PS-GTR外,所有模块均支持PCIe接口卡所需的数据速率为8.0GT/s (Gen3)和16.0GT/s (Gen4)。PCIe集成块可以配置为端点或根端口,根据目标设备速度等级和包支持各种链路宽度和速度。用于150Gb/s Interlaken和100Gb/s以太网(100G MAC/PCS)的集成块扩展了UltraScale设备的能力,实现了对Nx100G交换机和桥接应用的简单、可靠的支持。

时钟和内存接口

Zynq UltraScale+RFSOC包含强大的时钟管理电路,包括时钟合成、缓冲和路由组件,共同提供了一个高能力的框架,以满足设计需求。时钟网络允许非常灵活的时钟分配,以最小化与时钟信号相关的歪斜、功耗和延迟。时钟管理技术与专用内存接口电路紧密集成,以支持高性能外部存储器,包括DDR4。除了并行内存接口,Zynq UltraScale+ RFSOC还支持串行内存,比如(HMC)。

路由、逻辑、存储和信号处理

可配置逻辑块(CLB)包含6输入查找表(LUT和触发器,DSP片与27x18乘法器,36Kb Block RAM与内置FIFO和ECC支持,和4Kx72 UltraRAM块都与丰富的高性能,低延迟互连连接。除了逻辑函数外,CLB还提供移位寄存器、多路复用器和携带逻辑功能,以及将LUT配置为分布式内存的能力,以补充高能力和可配置的BRAM。DSP芯片具有96位的异或功能、27位的预加法器和30位的A输入,可执行多项独立的功能,包括乘累加、乘加和模式检测。

配置、加密和系统监控

Zynq UltraScale+RFSoC通过配置安全单元(CSU)引导,CSU支持通过256位AES-GCM和SHA/384块进行安全引导。CSU中的加密引擎可以在引导后的RFSoC中用于用户加密。系统监视器可以通过片上温度和电源传感器监控物理环境,还可以监控多达17个外部模拟输入。

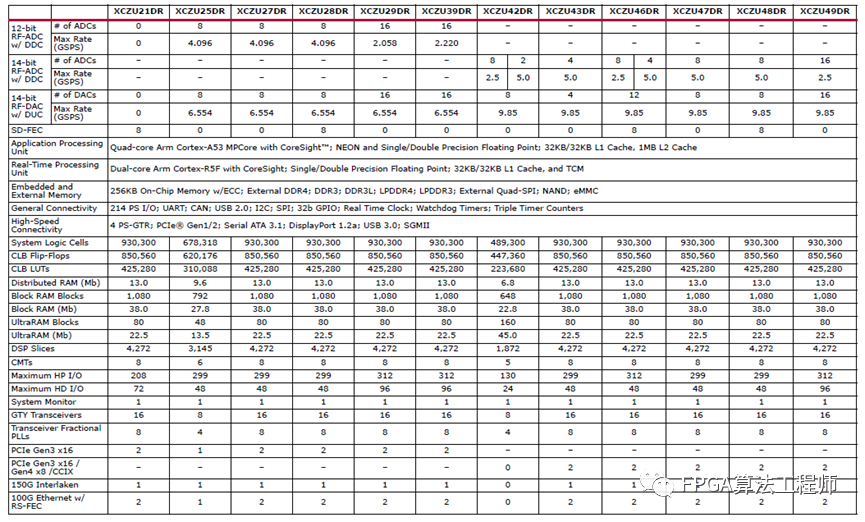

特性总结如表2所示。

表2 Zynq UltraScale+ RFSOC特性总结

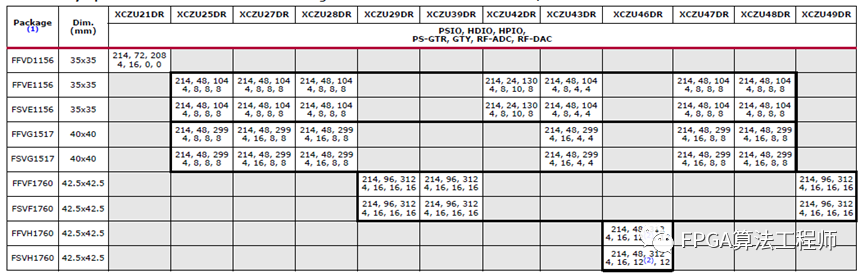

表3 Zynq UltraScale+ RFSoC Device-Package combination and Maximum I/O

相关产品

审核编辑:刘清

-

AMD Zynq UltraScale+ RFSoC评估套件调试检查表2026-04-15 180

-

Zynq UltraScale+ RFSoC DFE数据表:概述2023-09-14 623

-

Zynq UltraScale+器件封装和管脚用户指南2023-09-13 1105

-

基于Xilinx Zynq UltraScale+ RFSoC ZCU216评估套件详细内容介绍2022-07-04 14628

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 4875

-

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器2021-01-07 2796

-

赛灵思公司宣布其Zynq UltraScale+ RFSoC系列开始发货2019-07-29 3273

-

赛灵思关于Zynq UltraScale+ RFSoC系列产品介绍2019-07-26 6687

-

上新:Zynq UltraScale+ RFSoC ZCU111 评估套件2019-07-02 5369

-

支持6GHz以下频段的Zynq UltraScale+RFSoC2019-06-01 2115

-

Zynq UltraScale+ MPSoC器件的收发器技术演示2018-11-27 3529

-

Zynq UltraScale+ RFSoC的功能特点与应用2018-11-21 7600

-

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞2018-06-28 3150

全部0条评论

快来发表一下你的评论吧 !