基于FPGA开发板点亮LED灯

可编程逻辑

描述

设计流程:

设计规划--波形绘制--编写代码--代码编译--编写testbench--对比波形--绑定管脚--全编译--上板验证

设计规划

使用用户手册,了解硬件资源,这个示例中需要用到按键和LED灯:

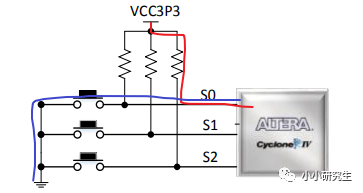

1、按键

在没有按键按下时,输出高电平(红色);当按键按下的时候,被按下的按键端会输出低电平(蓝色)。

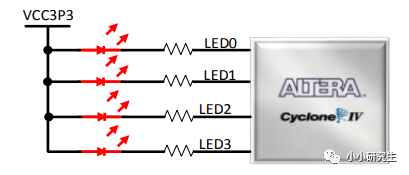

2、LED灯

当 FPGA 输出低电平时,LED 点亮,当 LED 输出高电平时,没有电位差,LED 灯熄灭。

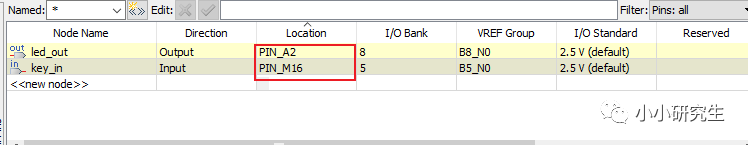

由上可知:需要实现的功能是,当按下按键时(key_in=0,PIN_M16管脚),LED灯要被点亮(led_out=0,PIN_A2管脚)。此处波形非常简单,省略画波形的步骤,对于复杂电路还是需要画波形来理清思路。这里波形应该是key与led波形一致。

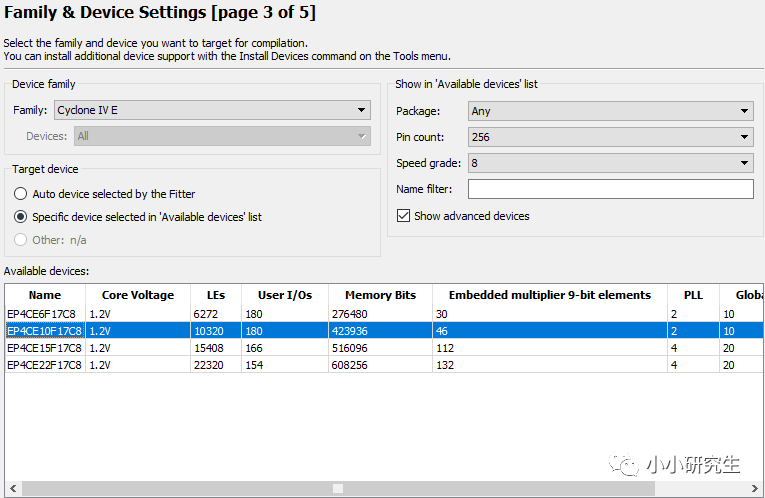

打开quartus,新建工程。

编写代码

编写.v文件,代码如下:

module led

(

input wire key_in , //输入按键

output wire led_out //输出控制led灯

);

//led_out:led灯输出的结果为key_in按键的输入值

assign led_out = key_in;

endmodule

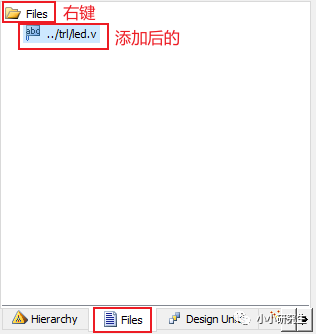

将.v文件添加到文件目录下,右键Files文件夹选择添加.v文件,添加完成后可以在Files下看到添加的.v文件:

代码编译

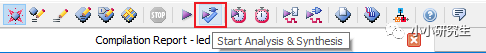

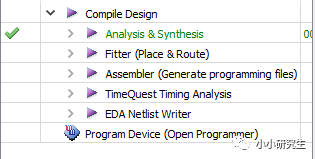

点击如图所示的图标,可以检查语法是否有错,综合器将代码解释为电路的形式。绿色表示通过。

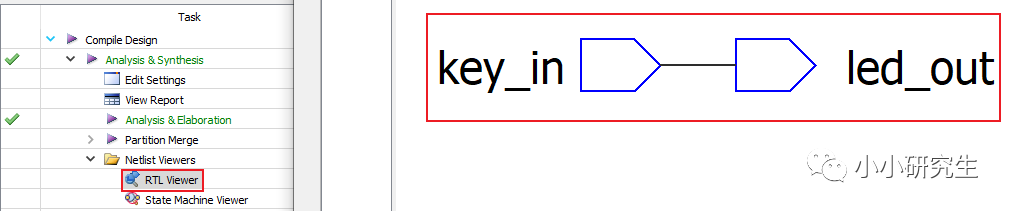

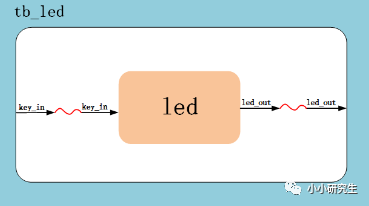

点击RTL viewer可以查看设计的硬件电路结构,和我们设计所表达的意思相同

编写testbench

Testbench是测试电路功能和性能的脚本。在线逻辑分析虽然好用但是每次修改代码都需要综合一次,而使用testbench做仿真的速度就很快,所以一开始就应该编写testbench以便后面大型电路的验证。

testbench就是产生输入波形,加入到被测模块上并观测其输出,和我们之前画好的波形进行比对。

编写.v文件

`timescale 1ns/1ns //时间尺度/时间精度,时间精度<=时间尺度

module tb_led();

wire led_out ;

reg key_in ;

//初始化输入信号

initial key_in <= 1'b0;

//key_in:产生输入随机数,模拟按键的输入情况

always #10 key_in <= {$random} % 2; /*取模求余数,产生非负随机数0、1

每隔10ns产生一次随机数*/

//\\* Instantiate \\//

led led_inst

(

.key_in (key_in ), //input key_in

.led_out(led_out) //output led_out

);

endmodule

tb_led模块中,首先定义初始的输入信号为低电平(一般时序电路使用非阻塞赋值<=),延迟10个时间单位(ns)产生随机数0或1赋值给输入,就完成了输入信号的波形设计。根据上一节中实例化的讲解,第2-5行和第14-19行完成的功能是将上一个led.v文件中led模块与tb_led模块相连。这样随机生成的输入信号就被加到led模块上,并得到输出led_out,通过验证led_out与我们期望的输出是否一致,就知道我们的设计是否正确。

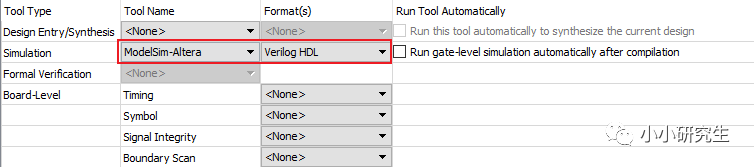

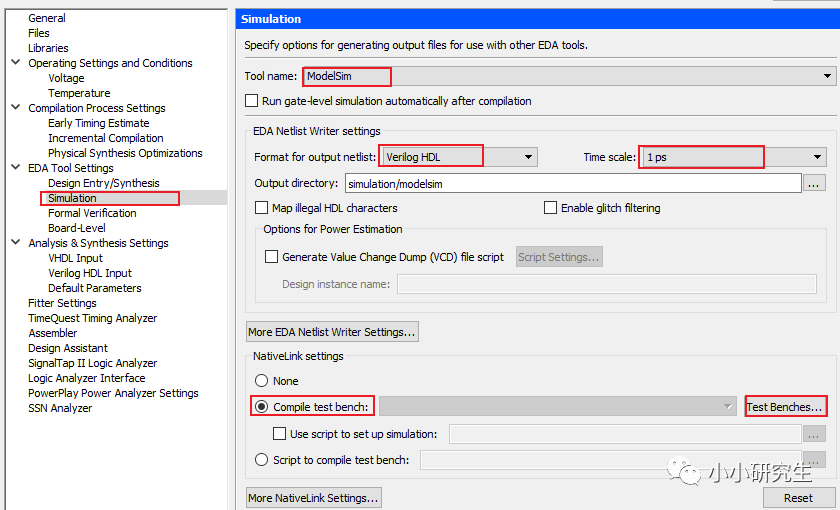

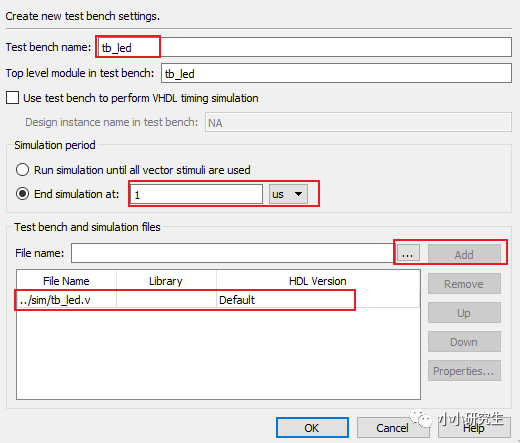

和之前的操作一样,将这个tb_led.v文件添加到Files文件下。然后在quartus的菜单栏中找到assignments-setting,如图所示。

对比波形

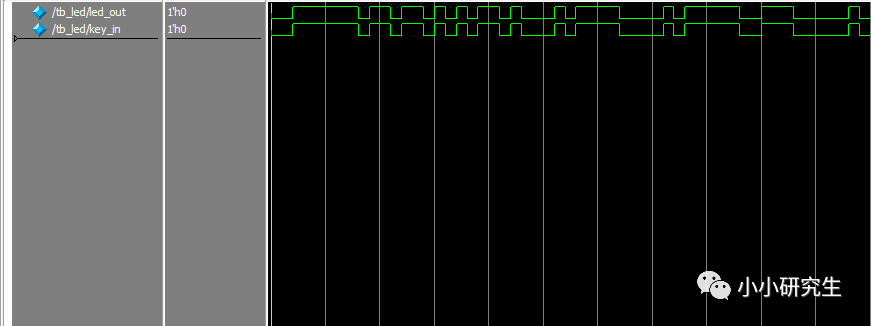

设置完成后,点击菜单栏的tools-run simulation tool-RTL simulation,能自动打开modelsim说明之前的关联操作是成功的,如果不成功,在上一节中看怎么关联。得到波形如图,观察得知led_out波形与key_in波形一致。

分配管脚

在开发板用户手册中就有对应管脚,按键有三个,我们选择M16的S0作为key_in,LED有四个,我们选择A2的LED0作为led_out。

全编译

全编译需要进行布局布线,管脚绑定后就可以对全局进行布局布线了。没有错误就可以上板了,有错误的话根据提示改。

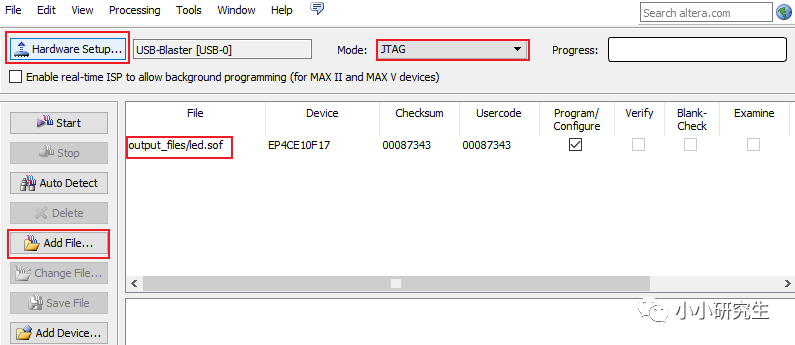

上板验证

上板是需要安装USB_blaster驱动的,在设备管理器中如果USB-blaster有黄色感叹号需要右键更新,文件在安装文件quartus-drivers-USBblaster或USBblaster ii中。安装完成后感叹号消失。

再点start,右上角的progress到100%,开发板就下载完成了。

按着按键A0不放,LED0一直被点亮,松手就关闭。

-

鸿蒙上点亮LED灯2023-01-16 2880

-

在FPGA开发板中点亮LED灯实现时序逻辑电路的设计2022-07-22 3778

-

点亮STM32、FPGA和Liunx板子的LED灯2022-04-18 10409

-

如何利用基于WiFi模块的nodemcu开发板去点亮一个led灯呢2022-02-15 1409

-

使用开发板点亮LED灯2022-01-17 1246

-

基于Study210开发板点亮LED灯的相关资料推荐2021-12-16 982

-

【STM32】开发板学习1 NUCLEO-L476RG:GPIO例程 点亮LED2灯2021-12-08 1388

-

如何去实现基于STM32开发板去点亮LED的设计2021-11-03 1346

-

如何使用UNO开发板控制外围电路中的6个LED灯点亮?2021-10-26 2780

-

如何去实现一种基于51开发板点亮一个LED灯的设计2021-08-27 1790

-

怎样通过FPGA去点亮开发板上的LED灯?2021-07-26 1199

-

采用FPGA DIY开发板实现11个LED走马灯功能2018-06-22 5603

-

让开发板上的LED灯闪烁起来吧2016-11-11 1048

全部0条评论

快来发表一下你的评论吧 !