时序逻辑电路设计之异步计数器

描述

上文介绍了同步计数器的设计原则以及各注意事项,本文承接上文继续介绍异步计数器以及三种常用的集成计数器的相关内容。

异步计数器设计

异步计数器与同步计数器最大的不同点就在于时钟信号的不一致性,即同步计数器的CP时钟都是同一个,异步计数器的时钟并不完全都是同一个,它可以是任何一个上级或下级触发器的输出及其组合逻辑,这就要求我们在设计异步计数器时,不能在列出真值表之后立即书写三大方程,而是必须先列出各触发器的时钟信号,这是与同步电路相比,异步电路设计的最大特点。 下面我们以题5.25为例说明。

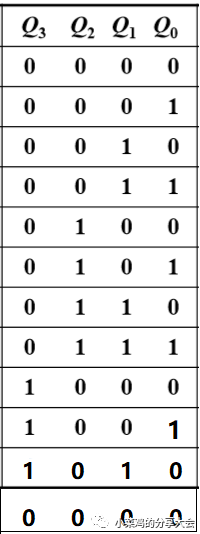

题干要求利用D触发器设计十一进制异步加法计数器。 首先还是要先列出真值表

首先另CP0=CP,即最低位变化最为简单明显,采用直接加入时钟信号的方式。

其次注意Q1,Q1只有在Q0下降沿才发生变化(这里注意使用的触发器时D触发器,所以应该观察的时沿,而不是具体的高低电平),但是D触发器是上升沿触发,所以CP1=Q0(非).依次可得CP2=Q1(非)、CP3=Q2(非)。

细心观察真值表的同学这个时候要质疑了,你这不对呀,最后一行明明不符合上述的触发机制,但是很恰巧的是只有最后一行0000不符合这一规则,因此我们可以在1010时直接置零得到,此时上述规则成立。 并且得到极为简单的驱动方程,即

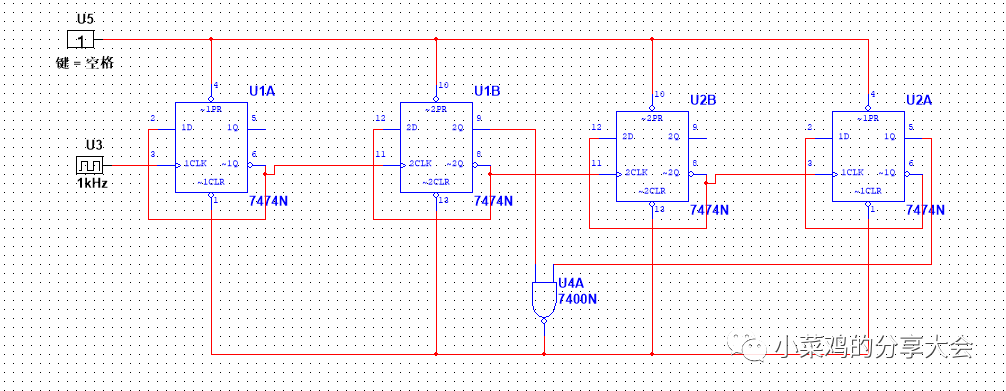

D0=Q0(非); D1=Q1(非); D2=Q2(非); D3=Q3(非); R(非)=(Q3Q1)(非)。 电路如图

上述方法的合理性在于,最根本的异步计数器的设计应当对进制有要求,即M应为2的指数,这时直接令

①加法计数器下降沿情况:CP0=CP,CPi=Q(i-1)

②加法计数器上升沿情况:CP0=CP,CPi=Q(i-1)(非)

减法计数器与加法计数器取法相反

对于上述不是2的指数的情况,我们应当观察真值表,寻找最多的符合的情况,对于不符合的情况加以修改(如上述R的设置),从而达到设计要求,最后同样要检查自启动问题。

集成计数器芯片

集成计数器芯片是之后进行电路设计的基本单元,而不用触发器自行搭建计数器,只需要对已有计数器进行外围电路修改即可,这里介绍课程中涉及到的三种计数器——74161、74160与74LS90。

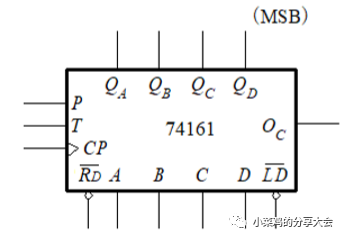

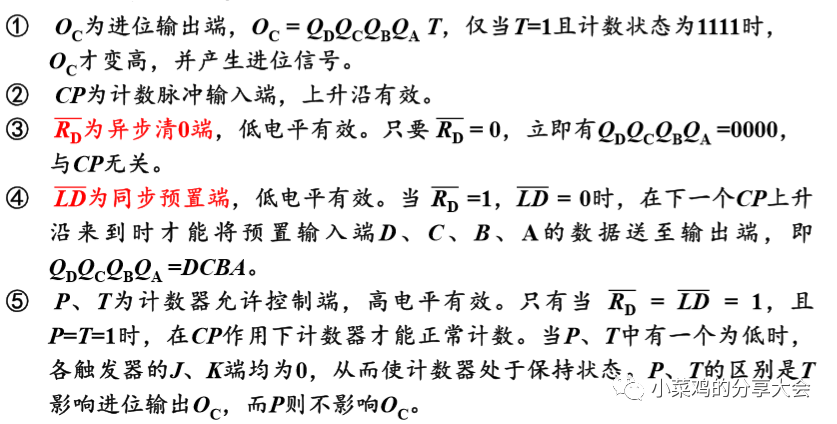

一、74161

74161是4位同步二进制计数器,具有计数、保持、预置、清零四项基本功能,时钟信号上升沿有效,因为其内置触发器为JK触发器。芯片各端口及功能如下:

74161值得注意的一点在于具有清零端和预置端,尤其是预置端,这就给予了74161进行进制更改的极大空间,我们之后的任意进制计数器就是基于这两个功能设计的。

二、74160

74160是同步十进制计数器,除此外与74161完全一致,包括各个端口及特性,因此不再赘述。

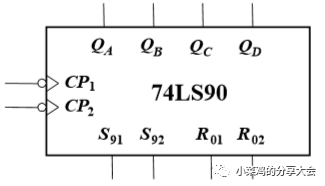

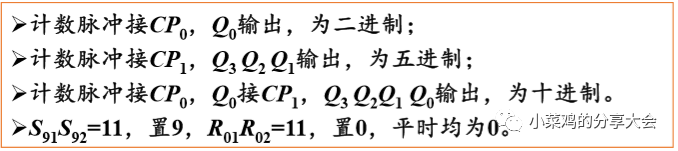

三、74LS90

74LS90是二-五-十进制异步计数器,上升沿触发,这三个进制的转变不需要外部的额外组合电路,只需进行不同地连接即可,具体如下:

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 14423

-

时序逻辑电路设计之计数器2023-05-22 7366

-

同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?2023-03-25 30223

-

时序逻辑电路的精华——计数器2022-12-29 2117

-

计数器及时序电路2022-07-10 840

-

时序逻辑电路分为几类2019-02-26 52729

-

时序电路设计的计数器详解2019-01-24 3899

-

时序逻辑电路的主要故障分析2018-04-09 7000

-

【FPGA开源教程连载】第三章 时序逻辑电路设计之计数器2016-12-21 5430

-

Multisim的时序逻辑电路设计仿真2012-02-10 2142

-

移位型计数器中反馈逻辑电路的设计2010-04-26 745

-

异步时序逻辑电路2009-09-01 1361

-

时序逻辑电路设计2009-03-20 6108

-

时序逻辑电路2008-09-24 3623

全部0条评论

快来发表一下你的评论吧 !