FPGA设计:4位全加器代码以及仿真

描述

大家好!今天给大家分享的是4位全加器的代码以及仿真程序。俗话说:“千里之行,始于足下。”对于初学者来说, 加法器是fpga初学者入门必须掌握的内容。我们很多朋友在入门时囫囵吞枣,一些基础的东西没有掌握好,导致后面在做大型项目的时候漏洞百出。因此,大家在开始学习或者正在学习fpga的过程中,一定要把一些基础的模块理解透彻。我会给大家分享一些常见的模块代码以及仿真程序,希望能帮助到大家更好的去学习fpga!下面一起来看下4位加法器的代码以及仿真程序:

4位全加器代码:

module adder4(cout,sum,ina,inb,cin);

output cout;

output [3:0] sum;

input [3:0] ina,inb;

input cin;

assign {cout,sum}=ina+inb+cin;

endmodule

4位全加器的仿真程序:

`timescale 1ns/1ns

module tb; // 测试模块的名字

reg [3:0] ina,inb; // 测试输入信号定义为 reg 型

reg cin;

wire [3:0] sum; // 测试输出信号定义为 wire 型

wire cout;

integer i,j;

adder4 adder(cout,sum[3:0],ina[3:0],inb[3:0],cin); // 调用测试对象

always #5 cin=~cin; // 设定 cin 的取值

initial

begin

ina=0;inb=0;cin=0;

for (i=1;i<16;i=i+1)

#10 ina=i; // 设定 a 的取值

end

initial

begin

for (j=1;j<16;j=j+1)

#10 inb=j; // 设定 b 的取值

end

initial // 定义结果显示格式

begin

$monitor($time,,,"%d+%d+%b={%b,%d}",ina,inb,cin,cout,sum);

#160 $finish;

end

endmodule

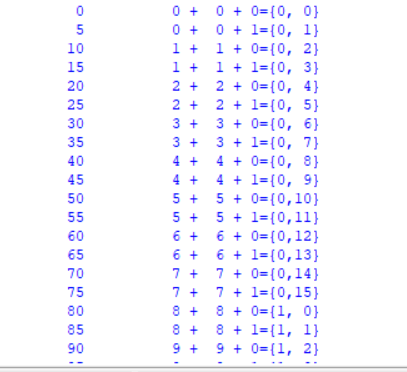

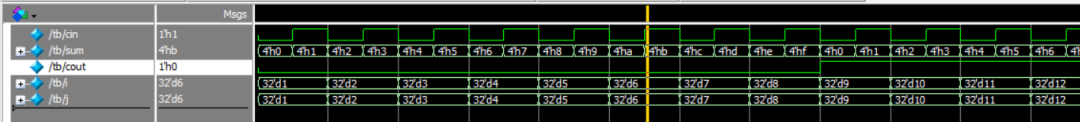

modelsim仿真结果:

具体的代码细节我就不详细阐述了,大家一定要学会思考,在这个代码中,主要要理解清楚这样几个问题:

什么叫全加器?

半加器和全加器的区别是什么?

什么叫低位进位?什么叫高位进位?

为什么仿真出来的波形图感觉和modelsim打印出来的结果不一样?比如感觉数据没对齐?

$monitor是什么意思?怎么使用?格式是什么?

这个4位全加器的电路图是什么样的?

就这样一个“简单”的4位全加器,你真的掌握了吗?如果你能快速回答出我上面提出的几个问题,那你就掌握了;如果不能,那还要好好看下!其实,我们很多的公司笔试就是考这些简单的题目,但是却可以难倒一大片同学!再次提醒大家!重视基础!

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

一位全加器代码VHDL2014-12-09 0

-

请问Quartus2中的用一位全加器来实现四位全加器2019-03-06 0

-

FPGA入门——1位全加器设计 精选资料分享2021-07-26 0

-

怎样去设计一种基于FPGA的1位全加器2021-09-17 0

-

基于Quartus II软件完成一个1位全加器的设计2021-12-17 0

-

什么是8位全加器和8为带超前进位的全加器?2022-02-09 0

-

什么是一位全加器,其原理是什么?2010-03-08 75904

-

什么是全加器 全加器工作原理2018-07-25 77492

-

FPGA各种数字电路模拟的详细资料合集免费下载2019-01-02 981

-

上百个Verilog HDL的程序设计实例代码合集免费下载2019-08-02 1557

-

使用FPGA实现一位全加器的文本输入实验报告资料免费下载2020-12-02 837

-

全加器的真值表2021-06-29 60677

-

Verilog数字系统设计——复杂组合逻辑实验2(8位全加器和8为带超前进位的全加器)2021-12-05 504

-

FPGA设计:4位计数器代码及仿真程序2023-05-24 1756

全部0条评论

快来发表一下你的评论吧 !