SiP和SoC的协同发展

描述

随着电子技术的飞速发展,集成电路正沿着三个方向发展:一是集成电路芯片的特征尺寸向不断缩小的方向发展;二是大量的不同需求催生多种类型的集成电路芯片;三是为满足小型化而朝着系统集成方向发展。因此国际上提出,一方面,半导体技术將延续摩尔定律(More Moore)发展,不断增强系统级芯片(SoC)的功能和集成度;另一方面,更多类型、更多功能的芯片或器件将通过系统级封裝(SiP)实现集成,向着超越摩尔定律的方向发展。

SoC 和SiP 技术是两种有效的系统集成解决方案,各有优缺点,也有各自特定的应用场景,为持续改善电子系统的性能、功耗、成本和尺寸提供了新的发展途径。随着半导体器件尺寸的特续缩小,SoC 将会面临诸如工艺波动严重、光刻成本增加、器件性能变差、器件功耗增加等严峻挑战。由于工艺不同,SoC将模拟、射频、数字甚至光电 功能整合在一起的难度很大,天线、MEMS 等徽机械结构的集成更加困难。而且在大多数情况下,SoC 的成本要高于不同功能分立器件的总和,因此 SiP 技术越来越受到业界重视。SP 技术是基于 SoC 技术发展起来的,具有灵活、易于扩展的特点,是SoC 技术的有效补充,但不会替代 SoC技术。以光电集成技术为例,限于当前光电子技术和集成制造工艺发展水平的限制,完全实现高性能的单片光电集成还有很多技术难题需要攻克,光子和电子混合集成在设计、加工、性能等方面仍旧具有巨大的优势。光子集成电路和电子集成电路技术的成熟和进步,推动了光电混合集成 SiP 成为光电组件及光模块的关键技术。而通信容量的增加,以及光电网络的升级改造,对光电混合集成的带宽、功耗等方面提出了严格的要求,进而推动光子集成电路和电子集成电路在带宽、功耗、制造工艺及集成方式等关键技术的进步,以满足光电组件.光电模块和光电系统的指标要求。

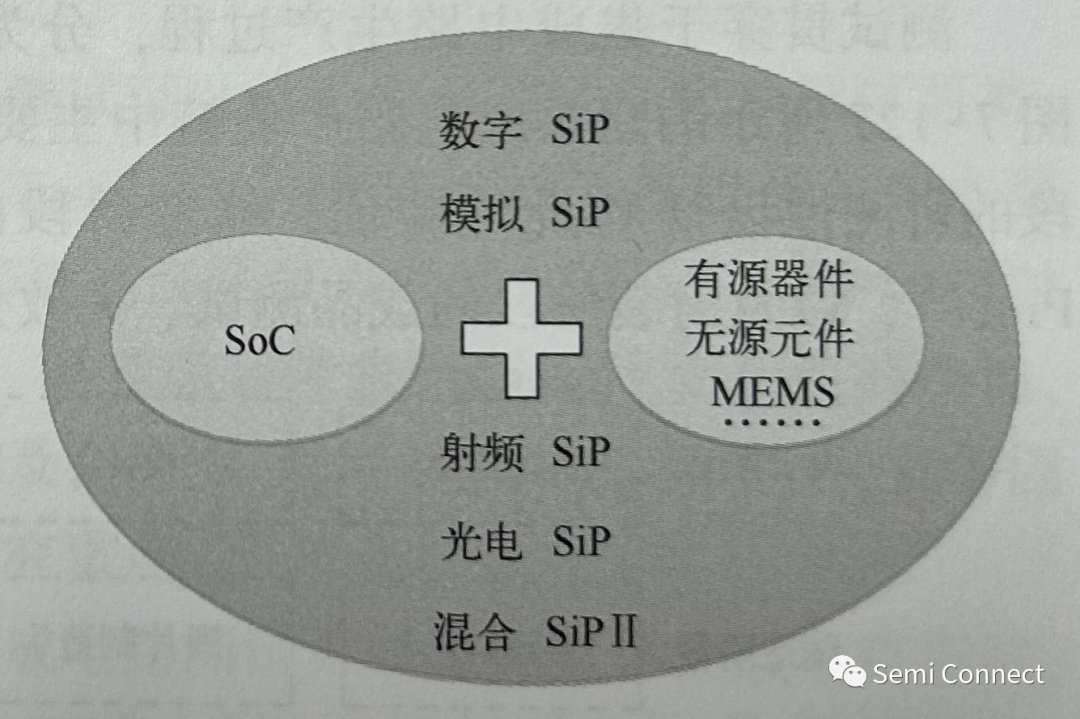

随着新原理、新方法的采用,硬件与软件联合设计,以及制造工艺水平工艺兼容性的提高,SoC 的功能将会得到快速发展,对 SiP 技术工艺能力的需求也越来越高。高性能 SiP 的实现也会对 SoC 的引脚布局、物理尺寸、材料体系KGD (Known Good Die) 等提出要求。制造设备的提升,新型材料的引入,以及封装工艺能力的不断提升,也会支撑 SiP 技术扩展到基于更高端 SoC 的系统异质集成的应用。在基于 SoC 进行系统级封装的过程中,许多新的封装形式和封装技术被相继提出,这对 SoC 和SiP 从设计、材料、工艺、测试等多方面提出了新的挑战,因而需要 SoC和 SiP 在诸如信号完整性、热管理可靠性、测试及互连制造技术等方面协同设计、互为补充、共同发展SoC 和 SiP 技术融合示意图如图所示。

审核编辑:汤梓红

-

京津冀城市照明协同发展联盟一行到访英飞特电子2025-07-03 1314

-

华工科技出席绿色智能船舶区域协同发展座谈会2025-03-26 799

-

多网协同发展探讨2023-11-10 523

-

数字产业协同发展的意义和作用2023-04-24 6699

-

关于HIC、MCM、SIP封装与SOC的区别2022-05-05 2138

-

数据中心与智能电网如何协同发展2021-01-05 1322

-

“5G+车联网”的车路协同发展模式促进智能汽车与智慧城市协同发展2020-10-28 3525

-

如何促进5G+车联网协同发展2020-04-08 2301

-

系统级封装(SiP)的发展前景(上)2018-08-23 4396

-

SiP的特点与SOC的区别和SiP的应用和发展方向的参考资料2018-04-29 33360

-

简单介绍SoC与SiP中芯片解密的应用2017-06-28 3095

-

一文读懂SIP与SOC封装技术2016-10-29 22911

-

SOC设计领域的核心技术-软/硬件协同设计2009-11-19 4738

-

SoC与SiP混合设计出多样化手机2009-02-12 3484

全部0条评论

快来发表一下你的评论吧 !