FFT_ad采样速率简析

描述

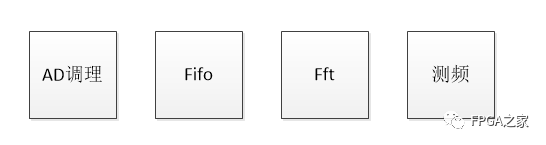

调用quartus的ip核测量频率和幅值,可以把程序分成四大部分。第一部分是AD采样模块,本次实验用的是ad828,最高采样率为70M,

根据奈贵斯特采样定律 Fs > 2Fc,即采样率要大于信号最高频率的两倍,如果要求信号的频率,需要知道频率所对应的地址和频率分

变率F。而F = Fs/N,所以只要知道了采样速率FS和地址坐标,就可以求出频率来。ad采样率为50M,程序设定的有四个频率分辨率,

分别为1Hz,10Hz,100HZ还有1KHz,拿1Hz来举例,FS = F * N,所以只要对采样时钟进行适当的分频就可以算出FS来。

另外还需要注意的一点就是fft输入的数据是有符号的,需要对原始数据处理一下,变成有符号的二进制,只要在前面补零就可以。

/*-----------------------------------------------------------------------

Date : 2017-XX-XX

Description : Design for 频率分辨率.

-----------------------------------------------------------------------*/

module sample_clk

(

//global clock

input clk, //system clock 200M

input rst_n, //sync reset

//key interface

// input key0_value,

input [1:0] key_data,

//sample_clk interface

output reg sample_clk

);

//--------------------------------

//Funtion :

/* always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

key_data <= 2'd0;

else if(key0_value)

key_data <= key_data + 1'b1;

end */

//--------------------------------

//Funtion : 分频

reg [15:0] n;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

n <= 16'd0;

else

case(key_data)

2'b00 : n <= 16'd48828; //频率分辨率 1Hz

2'b01 : n <= 16'd4882; //10Hz

2'b10 : n <= 16'd488; //100Hz

2'b11 : n <= 16'd48; //1KHz

default : ;

endcase

end

//--------------------------------

//Funtion : sample_clk

reg [15:0] cnt_clk;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_clk <= 16'd0;

else if(cnt_clk >= n - 1'b1)

cnt_clk <= 16'd0;

else

cnt_clk <= cnt_clk + 1'b1;

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

sample_clk <= 1'b0;

else if(cnt_clk >= n - 1'b1)

sample_clk <= ~sample_clk;

else

sample_clk <= sample_clk;

end

endmodule

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FFT至简设计法实现法_FFT算法_蝶形运算_fpga2017-08-02 5713

-

ad7705最大采样速率是多少?2017-11-16 21325

-

Raspberry Pi Pico上的ADC采样和FFT2023-06-16 2754

全部0条评论

快来发表一下你的评论吧 !