ASIC物理设计流程概述

电子说

描述

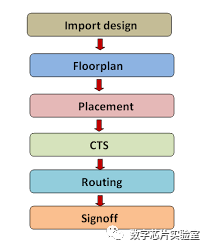

Physical design是将 电路描述(circuit description) 转化成 物理版图(physical layout) 的过程。在物理版图中规定cell的摆放位置和相互之间的 连线 。

Import design: 物理设计流程的第一步就是**导入设计。**在综合阶段RTL被转换成netlist,然后在物理设计阶段被读入物理设计工具中。

Floorplan: Floorplan阶段定义了 芯片(die)的大小 , macro和io的位置 , power grid的定义和连接 。在摆放完macro的同时,也定义了摆放std cell和routing的区域。

Placement: Placement是使用物理设计工具自动摆放std cell的过程,其中在global placement阶段,非常roughly地将std cell摆放在core里面,在detailed placement阶段,将std cell legalize到siterow上 ,保证没有overlap。

同时还需要通过GRC map来检查congestion.

CTS(clock tree synthesis): 在CTS阶段通过插入inverter和buffer来生成时钟树。因为clock信号对于基于DFF的ASIC设计非常重要,我们需要在CTS阶段balance clock skew以及最小化insertion delay来满足设计的时序(timing)和功耗(power)要求。

Routing: 在Routing阶段之前,只有power进行了实际的金属连线,macro、std cell、clock和io都只是逻辑上定义了连接关系(logically)。在routing阶段就需要用金属线进行物理上的连接(physical)。

**Signoff:**在routing阶段完成以后,芯片的物理版图已经确定了。在sign-off阶段需要保证芯片的质量和性能满足了要求,然后才能进行 投片(tape-out) 。

-

ASIC集成电路设计流程2024-11-20 4180

-

典型的基于RTL的ASIC设计流程分析2022-06-20 6760

-

ASIC与FPGA的开发流程是怎样的2021-11-01 2387

-

ASIC有哪些设计流程2021-07-23 1396

-

配网流程概述2021-07-22 1776

-

物理综合与优化的优点有哪些?流程是怎样的?2021-04-08 1285

-

ASIC芯片设计开发流程2021-04-07 2875

-

27张详解ASIC芯片设计生产流程的PPT2019-07-16 12269

-

ASIC和FPGA设计优势和流程比较2017-11-25 4955

-

寄存器的物理地址的概述2017-01-04 755

-

ASIC设计全流程入门资料2014-05-06 40907

-

ASIC设计流程及其应用2012-06-16 3677

-

ASIC到FPGA的原型验证代码转换技术2011-03-25 1403

全部0条评论

快来发表一下你的评论吧 !