射频开关(RF Switch)学习笔记

电子说

描述

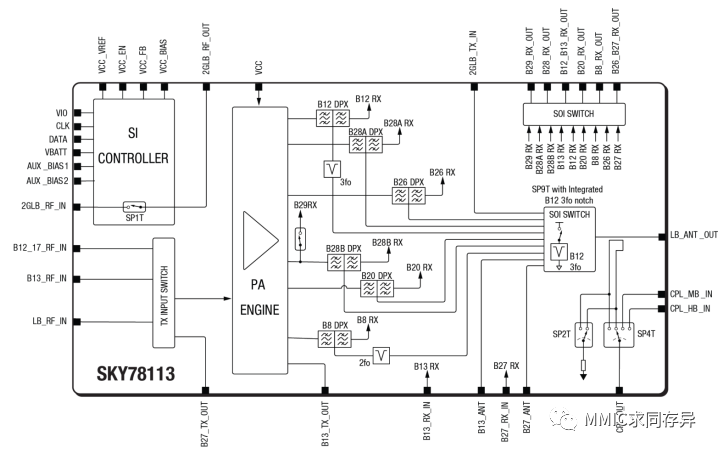

移动终端设备的射频前端模块(FEM)中射频开关处于关键位置且必不可少。射频开关的性能诸如插损、回损、隔离度、谐波抑制和功率容量等性能对射频前端链路的影响至关重要。

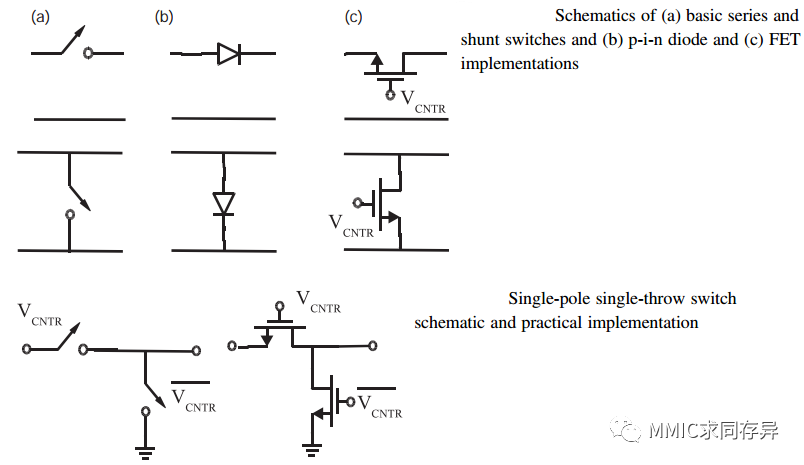

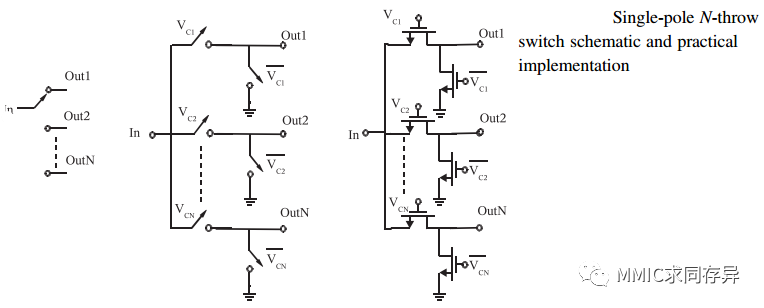

基本的串联、并联和FET开关可以简单图示,PIN二极管和肖特基(Schottky)二极管都可以用作开关。通过改变二极管的正反偏置条件可以实现二极管开关电路的切换。一方面,PIN二极管的Ron和Coff可以做的很小,便于实现很好的开关特性,但是,PIN二极管的偏置电源电压需要通过低通滤波器直接施加到RF信号端,PIN的集成也非常昂贵。相较于二极管,FET是三端口器件,不需要通过低通滤波器就可以将控制电压与信号路径隔离,可以将FET器件的源极和漏极之间用作开关,将控制电压加到栅极。开关的主要指标有插入损耗和隔离度等。

在时分多址系统中,射频开关用作切换天线到功放(上行)或者低噪放到天线(下行)通路。开关的插入损耗会增大接收通路的噪声系数,降低发射通路的功率附加效率。因此降低开关的插入损耗至关重要,此外,由于开关的上行链路需要通过较大的射频信号,一般还需要关注开关的P1dB和IIP3等线性指标。

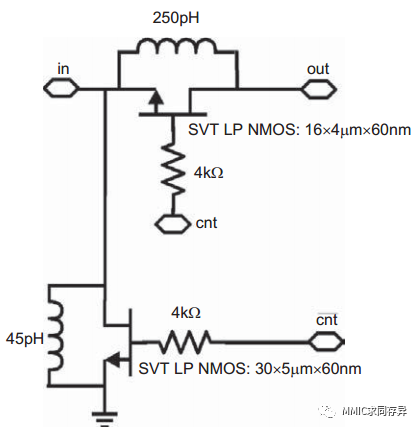

当FET开关关断时,开关的输出阻抗可以由Csw=Cdb + Cds + Cgd 并联一个大电阻表示。为了最大程度地提高高频下的截止阻抗,通常将一个电感与FET并联放置,以使其与输出电容Csw产生谐振,如下图并联系列天线开关所示。

我们注意到,与二极管开关不同,后者在导通时消耗偏置电流,而FET开关在“导通”或“截止”状态下均不消耗电流。但是,必须为开关中使用的FET的漏极和源极提供直流路径,以使其正常工作。如果不需要快速开关,通常会在栅极上串联几个kΩ的电阻,以减小漏极与地之间的电容。这种方案使栅极-漏极和栅极-源极电容串联出现,从而减少了输出电容的栅极-漏极分量,并改善了隔离和插入损耗。

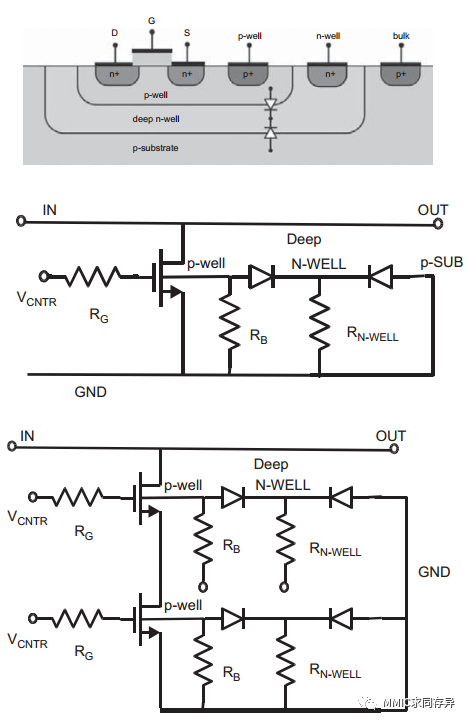

与SOI,蓝宝石硅(SOS)和III-V FET材料不同,硅MOSFET具有较大的漏极和源极电容,因此需要将开关放置在隔离的深n阱中并增加一个大电阻(一般为kΩ级)与衬底串联可以进一步减少损耗并改善隔离度,如下图所示。在所有FET开关中,可以通过垂直堆叠晶体管来提高线性度,但是会增大损耗。

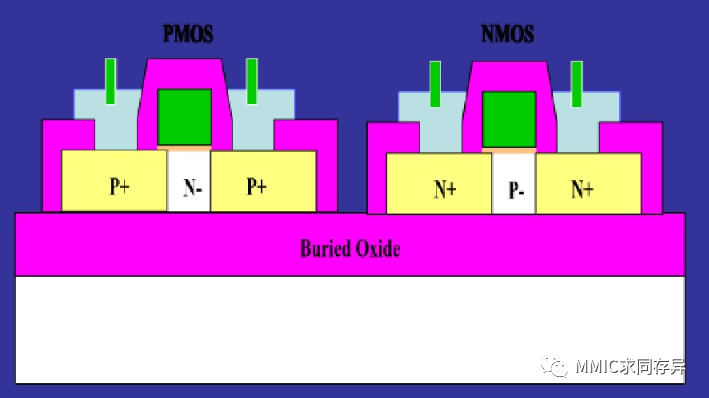

需要特别说明的是,目前射频开关设计采用的主要工艺是SOI和pHEMT。SOI是一种具有独特的Si/ 绝缘层/Si三层结构的新型硅基半导体材料。它通过绝缘埋层( 通常为SiO2) 实现了器件和衬底的全介质隔离,在器件性能上具有以下优点:

- 减小了寄生电容, 提高了运行速度。与体硅材料相比,SOI 器件的运行速度提高了20- 35%。

- 具有更低的功耗。由于减小了寄生电容, 降低了漏电, SOI 器件功耗可减小35- 70%。

- 消除了闩锁效应。

- 抑制了衬底的脉冲电流干扰, 减少了错误的发生。

- 与现有硅工艺兼容, 可减少13- 20%的工序。

-

“简约而不简单”的射频开关设计2023-07-04 2433

-

射频开关(RF Switch)基础知识2023-05-23 3460

-

简约而不简单的射频开关设计2023-04-19 1298

-

手机射频开关领域的工艺纷争:RF-SOIVs.MEMS2022-12-08 2867

-

射频开关(RF Switch)基础2022-10-31 4408

-

射频微机电系统开关相关介绍2022-05-12 3597

-

供应电连ECT品牌Mini RF Switch Series(RF射频测试座)2022-03-02 3410

-

开关电源学习笔记 --- 目录2021-10-22 1363

-

HCC-96RF-SH射频式液位开关2021-01-21 433

-

射频前端产业链大盘点:RF芯片领域必将打破由欧美厂商垄断的局面2018-08-01 18181

-

基于射频功放的GSM与DCS双频段RF射频前端设计2016-05-04 1272

-

基于AT88RF256的RF射频研究2010-09-30 2092

全部0条评论

快来发表一下你的评论吧 !