深度剖析NAND门

描述

介绍

NAND门是一个逻辑门,如果其所有输入均为真,则产生低输出(0),否则产生高输出(1)。因此,NAND门是AND门的反面,其电路是通过将AND门连接到NOT门来创建的。NAND门与 AND 门一样,可以有任意数量的输入探头,但只能有一个输出探头。

逻辑 NAND 操作由 NAND门执行。NAND门(以及NOR门)被称为通用门,这意味着它们是一种逻辑门,可以在不使用任何其他门类型的情况下实现任何布尔函数。

当两个输入均为逻辑低电平时,输出为高电平。如果任一输入为逻辑低电平,则输出为高电平。也可以说,当两个输入均为高电平时,输出为低电平。

说明和引脚排列

CMOS 版本

标准的 4000 系列 CMOS IC 是 4011,它包括四个独立的双输入 NAND 门。

图:CMOS 4011型集成电路中的NAND栅极示意图。

可用性

这些器件可从大多数半导体制造商处获得,例如仙童半导体,飞利浦或德州仪器。它们通常以通孔DIL和SOIC两种格式提供。数据表在大多数数据表数据库中都很容易获得。提供标准的2、3、4 和 8 输入 NAND 门:

CMOS:

4011: 四通道 2 输入 NAND 栅极

4023: 三路 3 输入 NAND 栅极

4012:双通道 4 输入 NAND 栅极

4068:单声道 8 输入 NAND 门

TTL:

7400: 四通道 2 输入 NAND 栅极

7410: 三路 3 输入 NAND 栅极

7420:双通道 4 输入 NAND 栅极

7430:单声道 8 输入 NAND 门

NAND栅极的应用

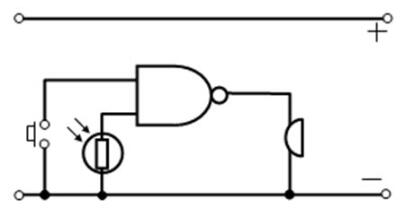

1. 防盗报警器

防盗报警电路如下图所示。它包括一个 NAND 栅极和一个 LDR 输入。LDR

是光相关电阻器的缩写。当按下报警开关时,其中一个NAND栅极输入变为低电平。如果LDR保持点亮,则第二个输入也很低。因此,NAND门的两个输入为低电平。因此,如果发生这两种情况中的任何一种,NAND门的输出将变为高电平,并且盗窃警报会发出警告。

2. 冷冻室警告蜂鸣器

当热敏电阻为冷时,其电阻为高电平,NAND栅极的输入为高电平。输出为低电平,因为当热敏电阻预热时,NAND栅极作为 INVERTER.As连接,其电阻降低,降低其两端的电压并降低NAND栅极的输入。当它低于某个阈值时,输出变为高电平,蜂鸣器发出声音。

3. 自动浇水系统

技术进步对于夜间浇灌植物很有用。该电路仅在LDR关闭(通常在夜间)且热敏电阻周围大气潮湿时工作。该电路包括一个继电器,用作开关,仅当满足NAND栅极的两个输入条件时,才允许泵水。

4.光激活盗窃警报

当开关处于位置 A 时,无论光相关电阻器的照明如何,蜂鸣器都保持关闭状态。当开关在位置 B关闭时,当短暂的闪光(可能来自防盗的手电筒)落在光相关电阻器上时,蜂鸣器将激活并保持活动状态。只有将开关返回到位置 A,才能关闭蜂鸣器。

NAND门的通用性

NAND门有一个非常有用的特性,将其与所有其他门区分开来。NANDGate本身可以实现所有可能的布尔表达式,而无需任何其他Gate,从而可以实现布尔表达式的任何复杂性。NAND门的这一特性称为功能完整性;由于这一特性,整个微处理器可以仅使用NAND门进行设计!此属性由

NAND 和 NOR 门共享,两者都称为通用门。

如何

如何从NAND门制作非门

当双输入NAND门的两个输入均为零时,输出为1;当两个输入均为 1时,输出为零。因此,只需将公共输入施加到NAND门或短路NAND门的所有输入端子,即可从NAND门轻松实现NOT门。

如何从NAND门制作AND门

NAND 门是一个 NOT 门,后跟一个 AND 门,所以如果我们能取消 NAND 门中 NOT 门的效果,它就会变成一个 AND 门。因此,一个NOT 门后跟一个 NAND 门来实现一个 AND 门。

优点和缺点

NAND门的优点如下:

1. NAND门是低成本设备,具有大存储容量。

2.高耐久性和耐用性。

3.该门具有良好的可更换性,这意味着如果闪存损坏,可以用适当的组件进行更换。

4. NAND的内存容量可以取代USB驱动器,数码相机和平板电脑等大文件。

NAND栅极缺点如下:

与NOR门相比,NAND存储器架构和速度的可靠性较差。

示例:单 2 输入 NAND 门

描述

74LVC1G00 是单路 2 输入 NAND 栅极。输入可由3.3 V或5 V器件驱动。此功能允许在3.3 V和5V混合环境中将这些器件用作转换器。所有输入端的施密特触发器动作使电路能够容忍较慢的输入上升和下降时间。该器件完全适用于使用 IOFF的部分关断应用。IOFF电路禁用输出,防止器件断电时通过器件的潜在破坏性回流电流。

特点和优点

1.65 V 至 5.5 V 的宽电源电压范围

过压容限输入至 5.5 V

高抗噪性

低功耗CMOS功耗

IOFF电路提供部分省电模式操作

±24 mA 输出驱动 (VCC = 3.0 V)

闩锁性能超过 250 mA

与 TTL 电平直接接口

符合JEDEC标准:

JESD8-7(1.65 V 至 1.95 V)

JESD8-5(2.3 V 至 2.7 V)

JESD8C(2.7 V至3.6 V)

JESD36(4.5 V至5.5 V)

静电保护:

HBM JESD22-A114F 超过 2000 V

MM JESD22-A115-A 超过 200 V

多种封装选项

额定温度范围为 -40°C 至 +85°C 和 -40°C 至 +125°C

功能图

-

双4输入正NAND门数据表2024-05-14 528

-

8输入正NAND门数据表2024-05-11 386

-

TTL逆变器和NAND门实验研究2023-08-28 1921

-

TTL逆变器和NAND门2023-05-29 2117

-

资料共享:嵌入式网络那些事LwIP协议深度剖析与实战演练2016-06-12 9168

-

【资料分享】C语言深度剖析2015-10-16 4712

-

linux内核深度剖析,另附有光盘资料2014-01-15 5138

-

陈正冲《C语言深度剖析》2013-08-17 12551

-

c语言深度剖析2013-04-02 3085

-

C语言深度剖析2012-08-14 4043

-

《C语言深度剖析》【超经典书籍】2012-08-02 7828

全部0条评论

快来发表一下你的评论吧 !