FPGA原型平台门控时钟自动转换

电子说

描述

现代FPGA综合工具会自动执行门控时钟转换,而无需更改RTL代码中的设计,然而,我们可能需要适当地手动指导综合工具执行门控时钟变换。需要注意的是,在这项任务中,各种综合工具的能力是不一样的,这是综合工具效果的一个展示功能。

以下是使综合工具成功转换门控时钟的一些简单的指导。

识别基准时钟,并通过添加频率或周期约束将其定义到综合工具中,例如vivado或者synplify。

不要将下游门控时钟定义为时钟。去掉在SoC设计流程中可能指定的门控时钟的任何周期或频率限制。

在综合工具中设置任何必要的控件,以启用门控时钟转换。

识别设计中由门控时钟驱动的任何黑盒。要修复驱动黑盒的门控时钟,必须识别黑盒的时钟和时钟启用信号输入。应使用特定于综合工具的指令来识别它们。

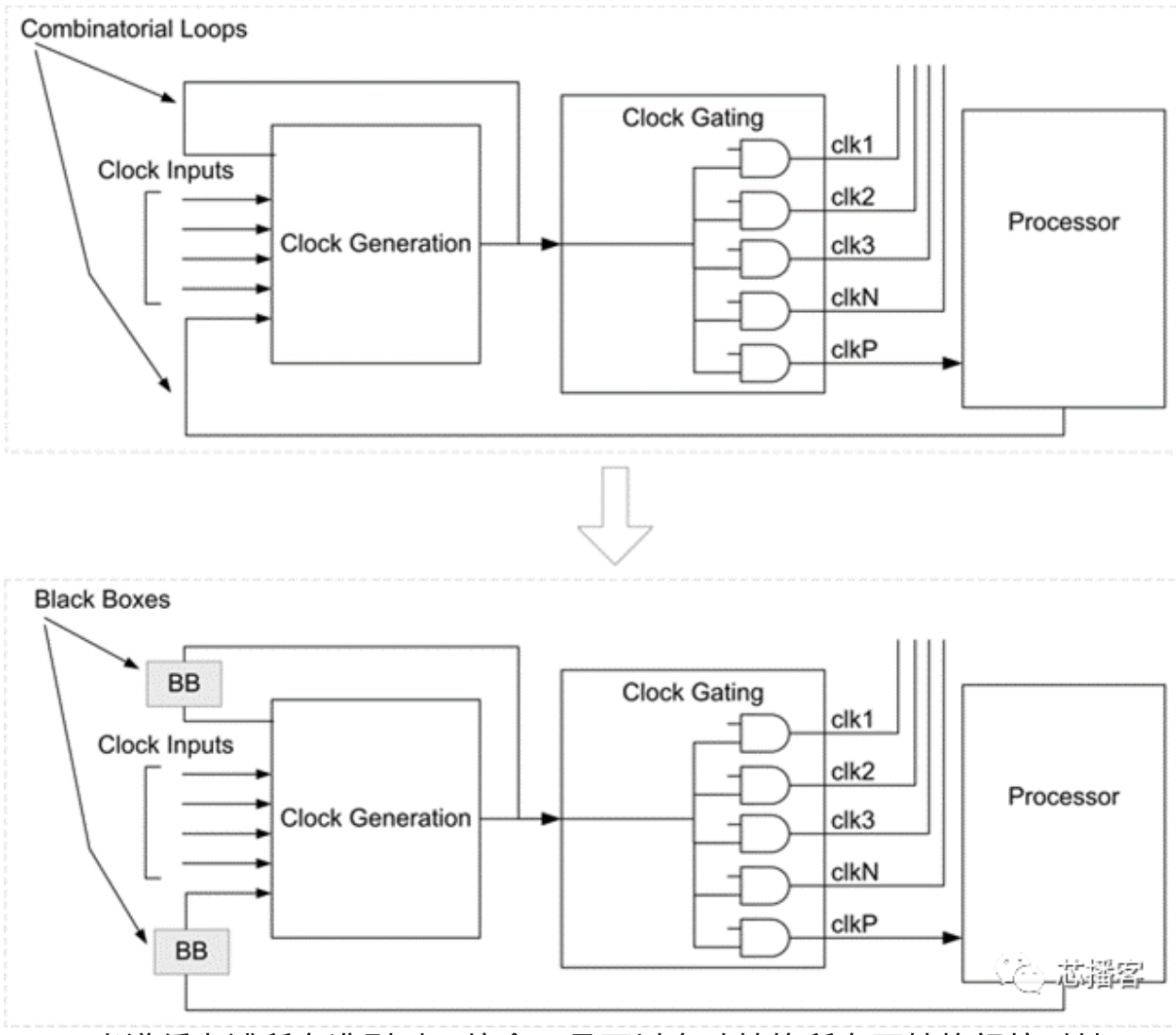

如果在时钟门控逻辑中存在组合回路,则组合回路应该被断开。这可以通过插入一个通路黑盒来实现,该黑盒是一个具有一个输入和一个输出的黑盒,位于组合环路路径中,如图所示。然后,我们可以为黑盒创建一个单独的网表,输出仅连接到输入。然后,必须在放置和布线期间将为黑盒创建的网表添加到设计中。

当遵循上述所有准则时,综合工具可以自动转换所有可转换门控时钟。

当满足以下所有条件时,门控时钟可转换。

1 对于选通信号的某些组合,选通时钟输出必须能够被禁用。

2 对于选通信号的其余组合,选通时钟输出应等于基准时钟或其反相值。

3 门控时钟仅基于一个基准时钟导出。

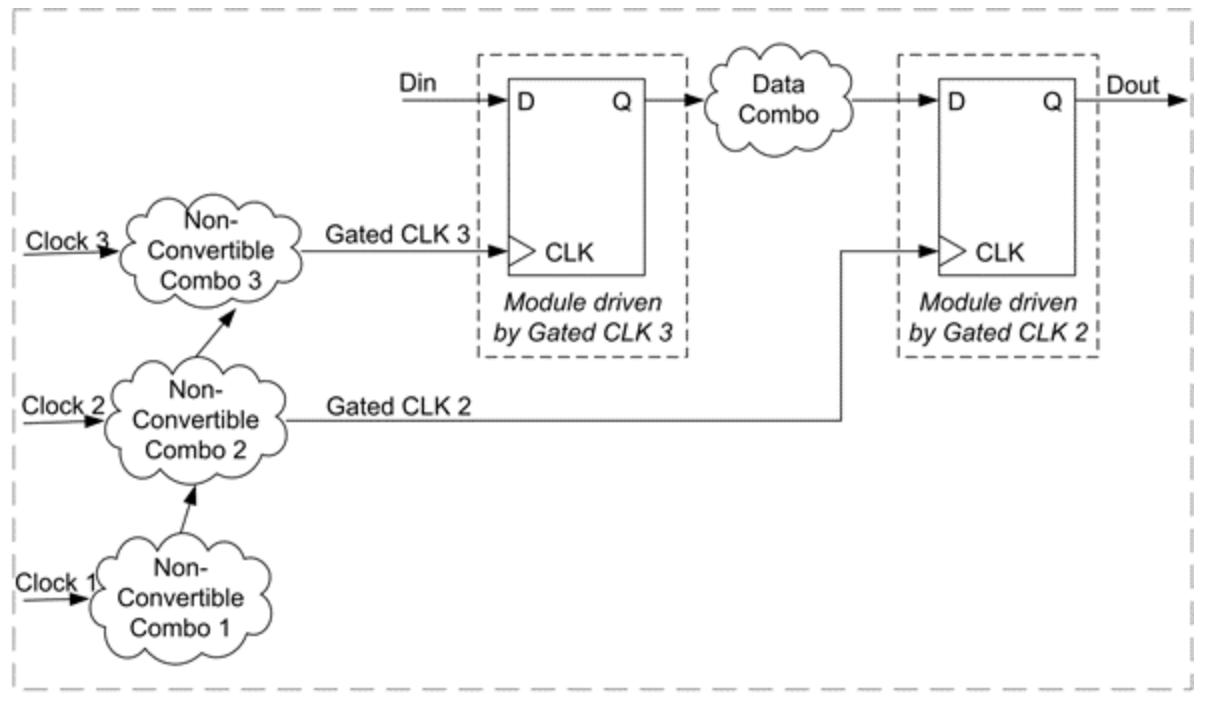

为了使SoC设计在基于FPGA的原型验证平台上可靠地工作,设计中的所有门控时钟都应该被转换。如果门控时钟是基于多个时钟导出的,或者门控逻辑是复杂的,那么合成工具不能进行门控时钟转换。然而,这些场景有时在SoC设计中很常见,这会导致许多设置和保持时间冲突。以下是处理这些场景的一些方法。如果适用,请共同使用所有这些方法。

如果在由基本时钟驱动的时序元件和未转换的门控时钟之间没有路径,则后者将不会产生任何跨域时序冲突。然而,它们在FPGA中的布线可能需要仔细控制,以避免上述竞争。

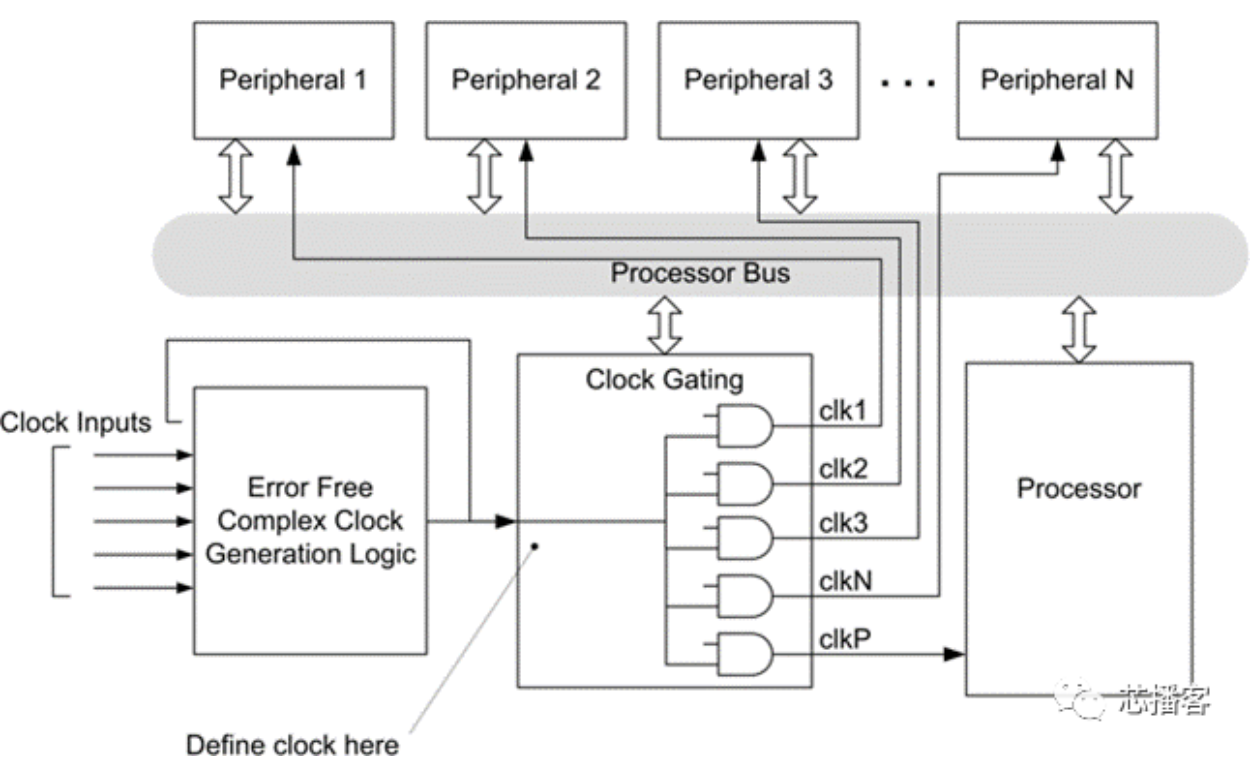

设计中的中间节点可以被识别并定义为基准时钟,使得由该节点驱动的门控逻辑是可转换的。通常,SoC设计将具有时钟生成逻辑块crg模块,该逻辑块具有复杂的逻辑以生成一个理想的时钟。该时钟将基于许多不同时钟之间的切换而创建。该生成的时钟将用作设计中具有单独选通逻辑的其余块的基准时钟。在时钟生成逻辑块的输出上定义时钟将确保基于该时钟创建的所有门控时钟将由FPGA综合工具转换。

如果一个基本时钟与其复杂门控时钟之间存在有效的定时路径,则尝试手动平衡这些路径之间的时钟路径。通过在

其中一个时钟路径中引入馈通LUT、时钟缓冲器、PLL和数字时钟管理器,可以实现平衡。

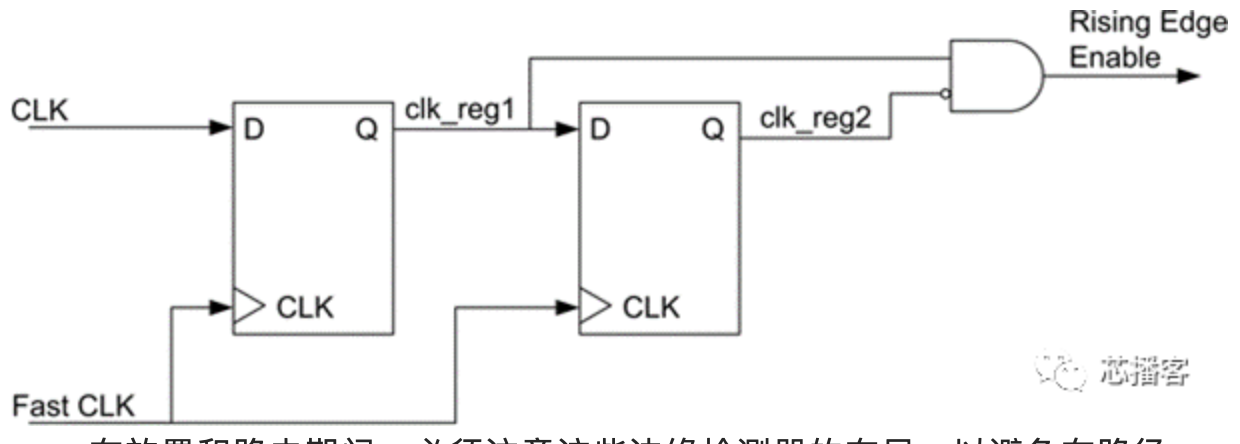

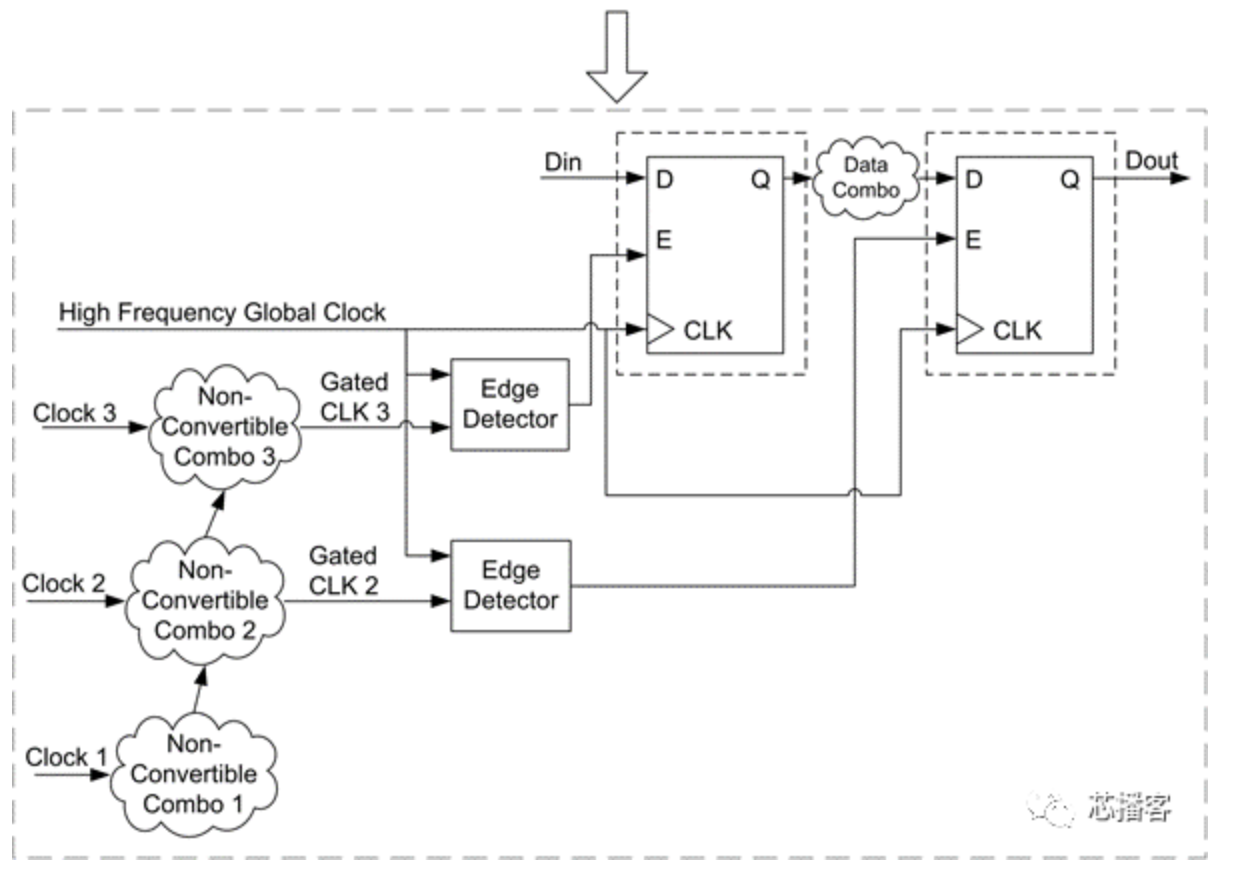

如果仍有一些门控时钟未被转换,并且存在巨大的有效时序冲突,则尝试以非常高的频率运行FPGA中的所有时序元件——大约是设计中最快时钟的10倍。对于设计中的所有门控时钟,插入相对于较快时钟的上升沿检测器。

该上升沿检测器可以通过使用更快的时钟对门控时钟信号进行双重注册(例如clk_reg1和clk_reg2),然后形成逻辑以检测从低到高的变化(~clk_reg2和 clk_reg_1)来设计,如果原始时钟驱动也在负边缘上工作的FF,则也需要负边缘检测器电路。

在放置和路由期间,必须注意这些边缘检测器的布局,以避免在路径clk_reg1和clk_reg2之间引入差分延迟。使用这些边缘检测器的输出作为所有顺序元件的启用,这些顺序元件最初由相应的门控/生成时钟驱动。

这样,整个FPGA由一个更快的时钟源驱动,如图所示。该时钟将使用FPGA中的专用全局路由资源,因此相关的时钟偏差将非常小,并且可以很容易地满足时序要求。

时钟门控在SoC设计中很常见,为了在FPGA上成功原型化SoC设计,应谨慎处理门控时钟。当受到适当约束时,现代FPGA综合工具会自动处理大多数的门控时钟。

-

AMD Vivado Design Tool综合中的门控时钟转换2025-05-14 2364

-

XOR自门控与时钟门控的不同之处2024-01-02 3438

-

门控时钟与多扇出问题解决方案2012-01-12 5730

-

fpga门控时钟问题2012-10-28 3719

-

FPGA的时钟门控是好还是坏?2019-02-21 5922

-

高频RFID芯片的FPGA原型验证平台设计及验证2019-05-29 2847

-

什么是时钟门控?如何去实线时钟门控的设计呢2022-12-19 1793

-

基于FPGA的时钟设计2011-09-21 4263

-

低功耗时钟门控算术逻辑单元在不同FPGA中的时钟能量分析2015-11-19 680

-

门控时钟2016-05-10 850

-

什么是门控时钟 门控时钟降低功耗的原理2021-09-23 15921

-

门控时钟实现低功耗的原理2022-07-03 3382

-

什么是门控时钟?如何生成门控时钟?2022-12-05 4017

-

FPGA原型平台到底能跑多快呢?2023-04-04 3434

-

FPGA原型验证系统的时钟门控2023-04-20 2330

全部0条评论

快来发表一下你的评论吧 !