FPGA设计:4位计数器代码及仿真程序

描述

大家好!今天给大家分享的是4位计数器的代码以及仿真程序。

4位计数器代码:

module count4(out,reset,clk); output [3:0] out; input reset,clk; reg [3:0] out; always @( posedge clk) begin if (reset) out<=0; // 同步复位 else out<=out+1; // 计数 end endmodule

4位计数器的仿真程序:

`timescale 1ns/1ns `include " count4.v " module coun4_tp; reg clk,reset; // 测试输入信号定义为 reg 型 wire [3:0] out; // 测试输出信号定义为 wire 型 parameter DELY=100; count4 mycount(out,reset,clk); // 调用测试对象 always #(DELY/2) clk = ~clk; // 产生时钟波形 initial begin // 激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end // 定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule

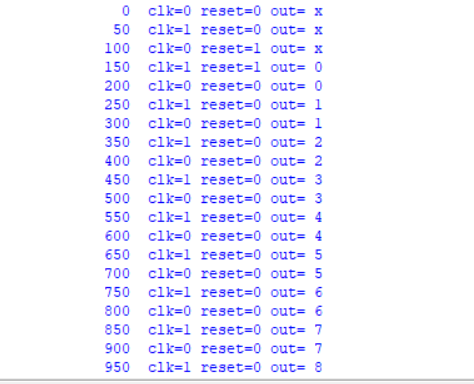

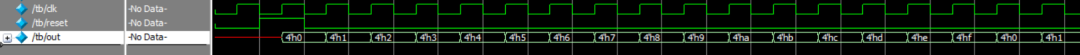

modelsim仿真结果:

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

用于4位计数器的SDK C程序怎么写2020-05-19 0

-

1602液晶的6位计数器程序2010-04-21 719

-

4位十进制可逆计数器电路2010-12-10 7479

-

基于FPGA的PWM计数器改进设计2012-04-06 1945

-

基于Multisim的计数器设计仿真2013-07-26 3292

-

基于Proteus的任意进制计数器设计与仿真2016-07-29 1824

-

计数器74LS161的Multisim仿真2018-01-17 65021

-

上百个Verilog HDL的程序设计实例代码合集免费下载2019-08-02 1550

-

四位计数器的程序和电路图及仿真等资料合集免费下载2019-09-09 1166

-

基于单片机定时器/计数器的时钟设计及计数设计2021-11-05 707

-

multisim仿真四位计数器2022-07-23 604

-

基于FPGA的十进制计数器2022-12-20 718

-

基于ATmega8单片机基于T_CO的计数器设计Proteus仿真源程序2023-05-05 285

-

FPGA设计:4位全加器代码以及仿真2023-05-23 4013

-

同步4位计数器数据表2024-05-15 108

全部0条评论

快来发表一下你的评论吧 !