数字信号处理-DDS IP应用实例

描述

前言

本文根据DDS的相关手册构建仿真工程,包括单通道工程、多通道工程、使用DDS进行混频操作。

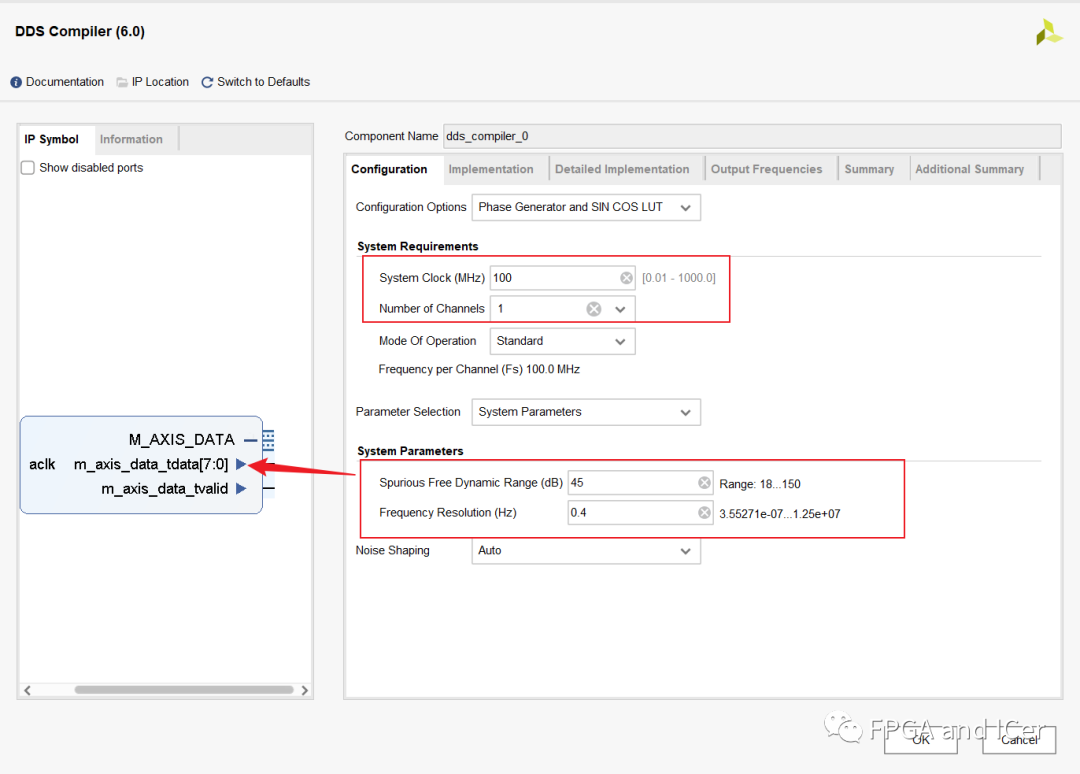

单通道IP配置

新建一个空白工程,FPGA型号任意,添加DDS IP到工程中,双击打开配置项界面。 该界面可以配置DDS的相关配置选项和基本的一些参数。 这里重点说下常配置的参数。

- 系统时钟:为DDS工作的系统时钟。

- 通道数量:根据设计需求选择通道数量。

- 无杂散动态范围(SFDR):这里输入对应数值可以进行计算出输出DDS数据的位宽,N代表DDS输出的位宽数。 利用下面公式可以对45进行换算,经过计算N=7.47,向上取整得到输出位宽为8。

- 频率分辨率 :频率分辨率用于控制最小的分辨辨精度。

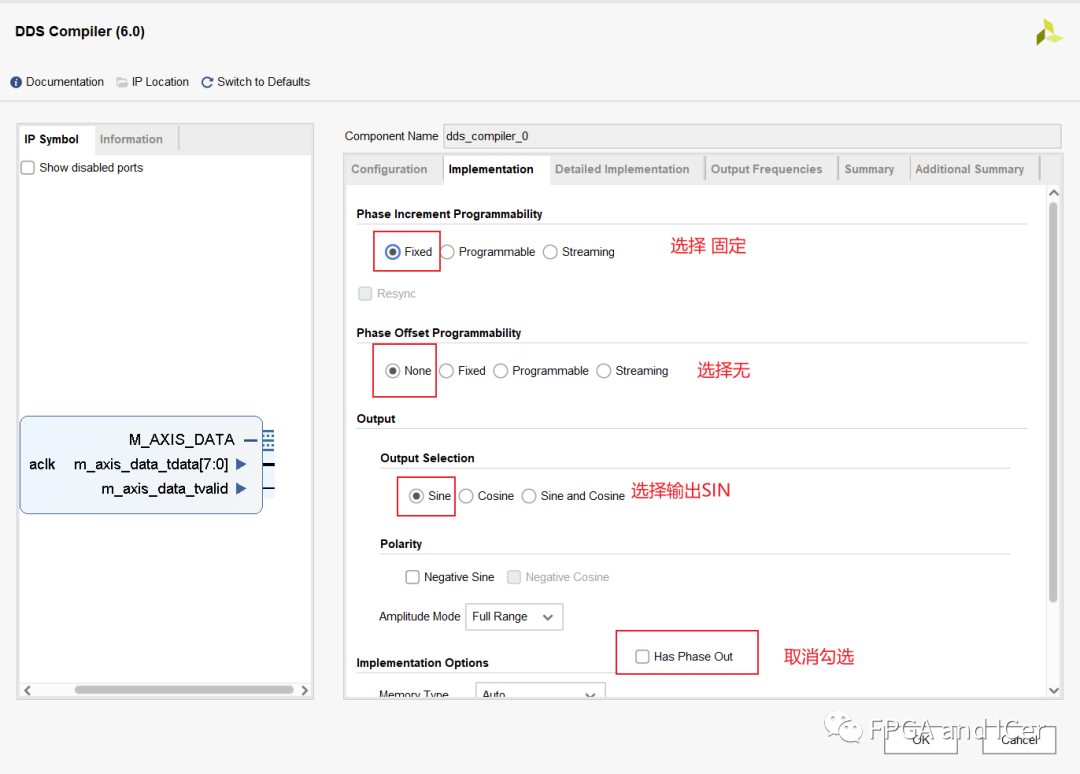

配置完成基本信息配置下一页,基本保持默认即可,这里只想查看波形,所以相位输出就关闭。

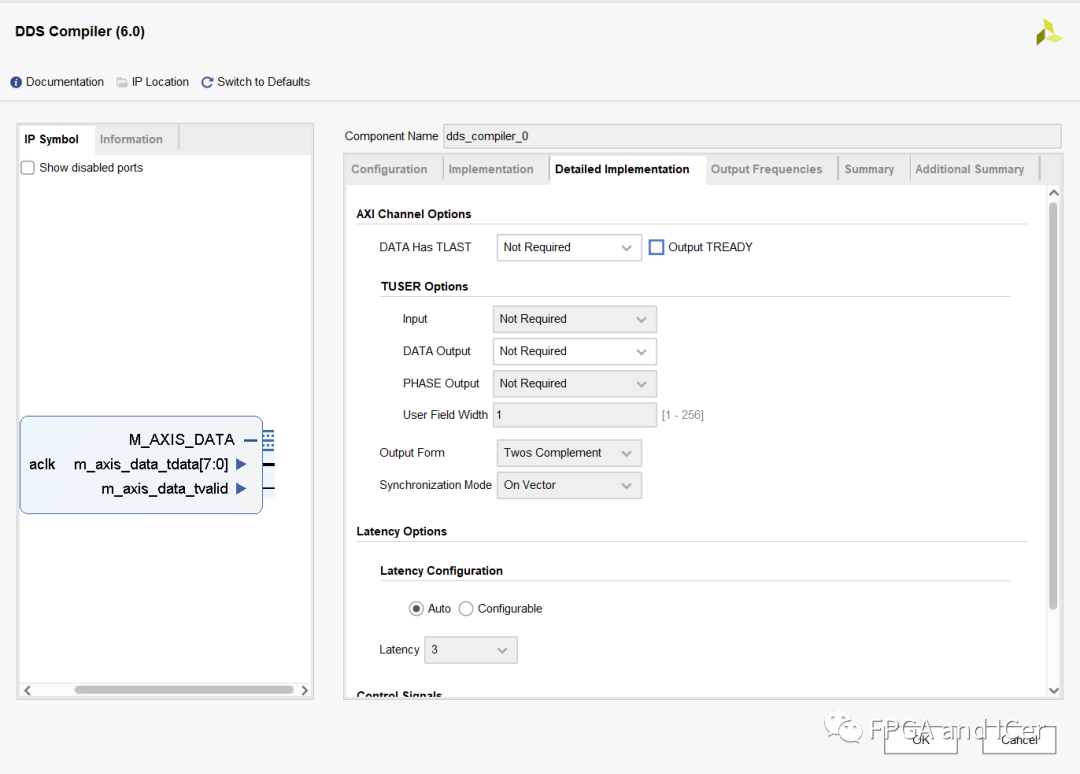

第三页配置保持默认即可。

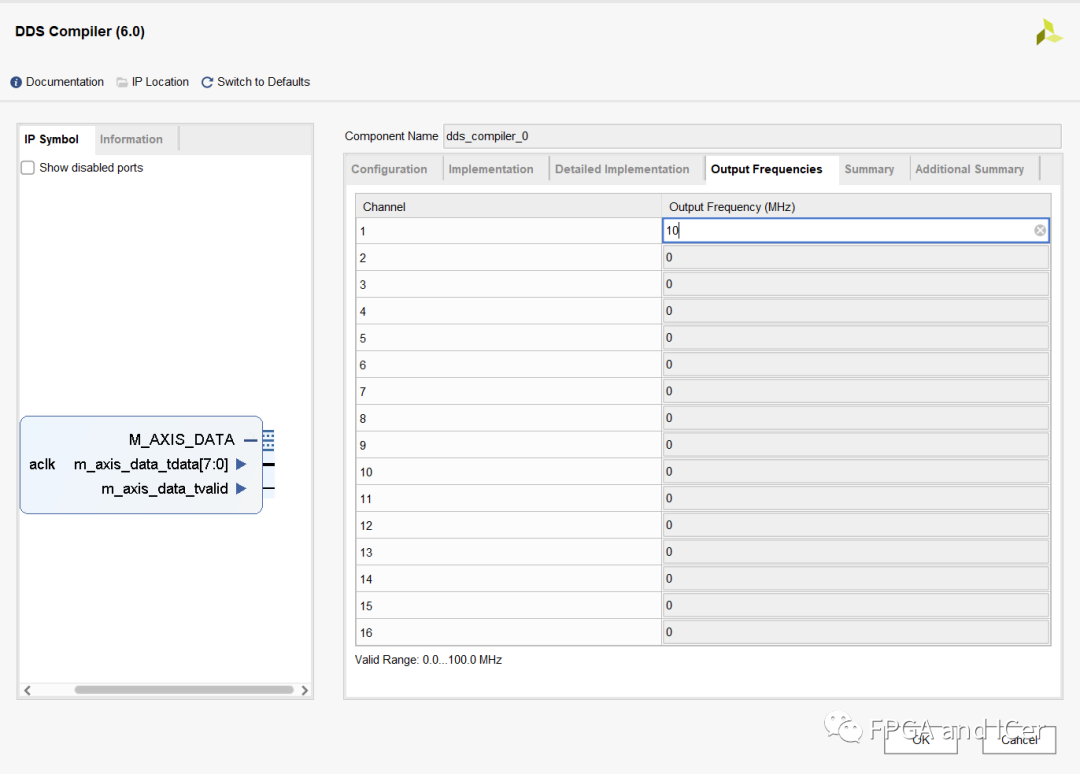

第四页输出频率配置,这里设置输出10M

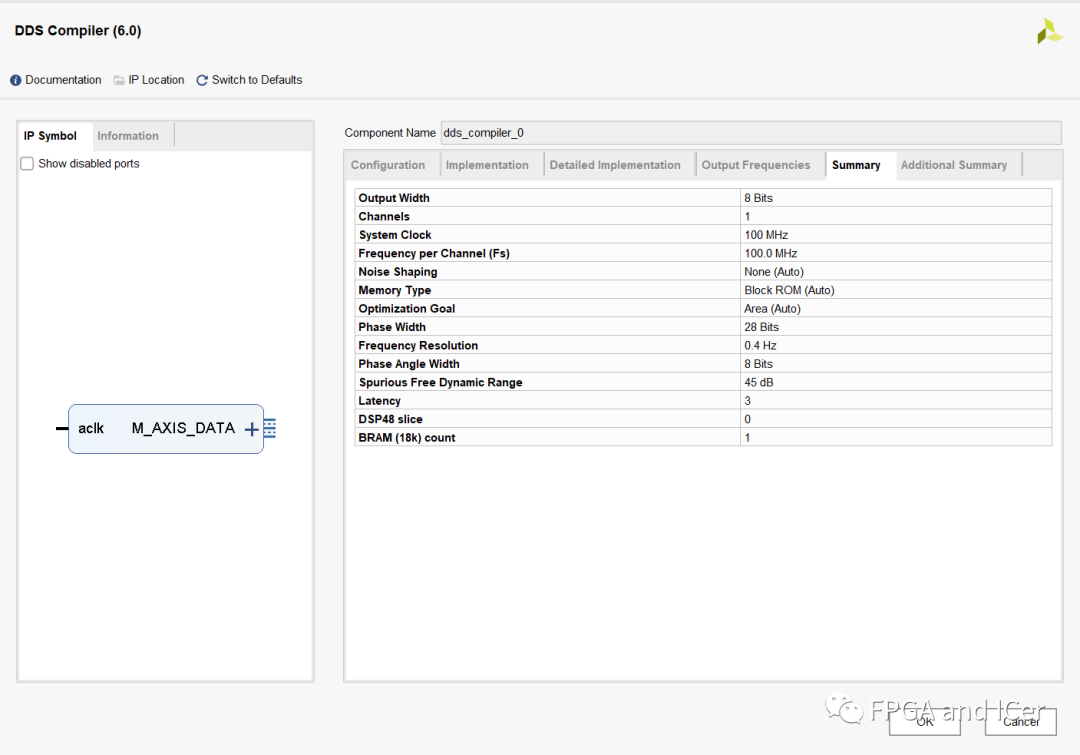

在总结也中可以看到输出信号的相关信息,这里可以简要计算下phase width的28Bits如何来的。 该参数和DDS的工作频率以及启用通道,还有频率分辨率有关。 通过下述式子,可以变形求得当前设置下Frequency Resolution。 DDS时钟为100MHz,通道为1,相位位宽28Bits,换算得到频率分辨率为0.37252902984619140625。 向上取整数,则得到当前设置的0.4Hz的分辨率。 已知频率分辨率也可以换算位宽,不过此时得到的位宽是按2的次方去取整。

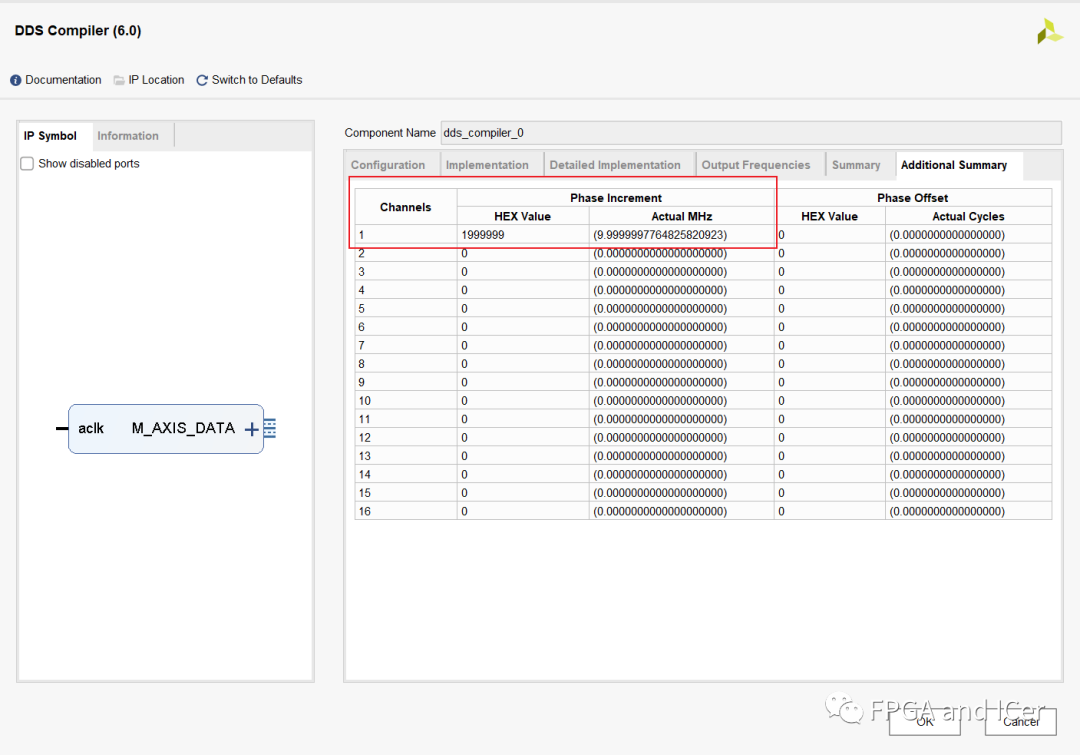

同时根据前面的相关参数可以计算向量增量。 带入设置的参数可计算到增量的数值大小。

单通道实例

顶层调用

按上述IP配置配置完成后在top层进行实例化,然后即可完成单通道DDS的调用使用。 顶层模块调用代码如下:

module top(

input clk

);

wire m_axis_data_tvalid_ch1;

wire [7:0] m_axis_data_tdata_ch1;

//单通道测试

dds_compiler_0 ch1_dds(

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_ch1), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata_ch1) // output wire [7 : 0] m_axis_data_tdata

);

endmodule

编写仿真

编写testbench,由于顶层只给了一个时钟的输入端口,所以只需要对时钟进行仿真设计,单通道DDS测试如下:

`timescale 1ns / 1ps

module tb_top;

// top Parameters

parameter PERIOD = 10;

// top Inputs

reg clk = 0 ;

// top Outputs

initial

begin

forever #(PERIOD/2) clk=~clk;

end

top u_top (

.clk(clk)

);

initial

begin

#10000;

$finish;

end

endmodule

编写完成后直接点击运行仿真测试即可。

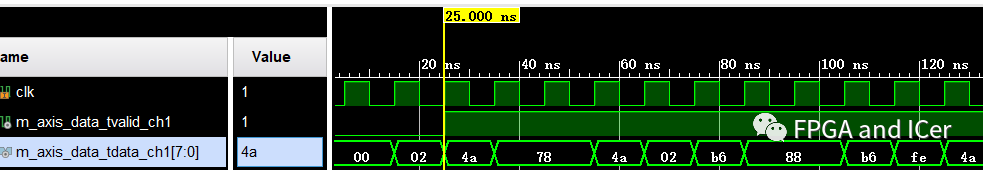

测试结果

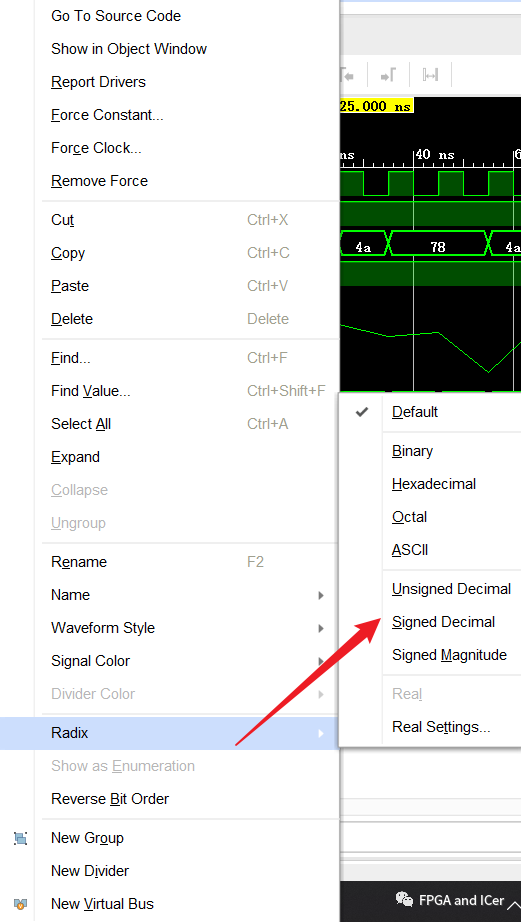

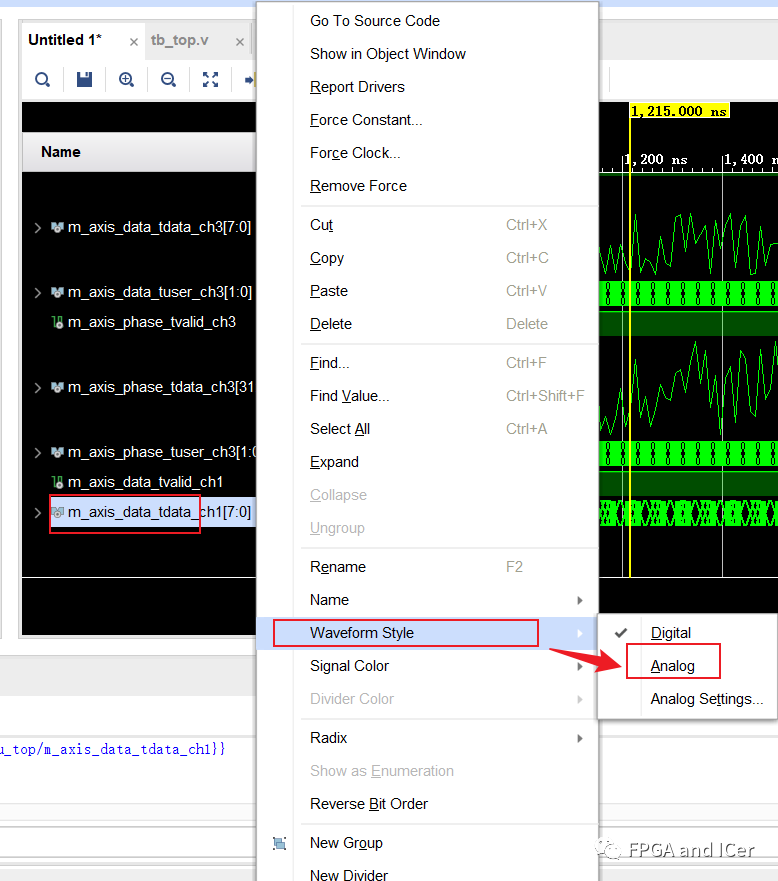

运行仿真查看波形结果,将顶层例化模块的波形添加到波形窗口,可以得到数字模式下的十六进制显示的数值,可将数值转化为波形显示方便观察。

设置下数据的进制格式和显示模式,这里修改通道数据为analog 模式,进制修改为有符号十进制。

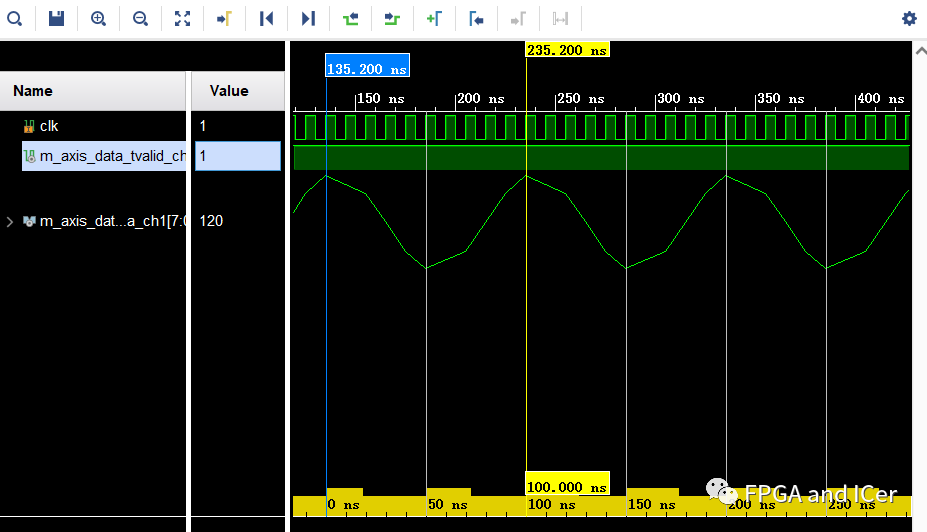

修改后添加游标,可以观察到输出波形周期为100ns,也即10MHz,输出波形频率和设置一致。

多通道实例

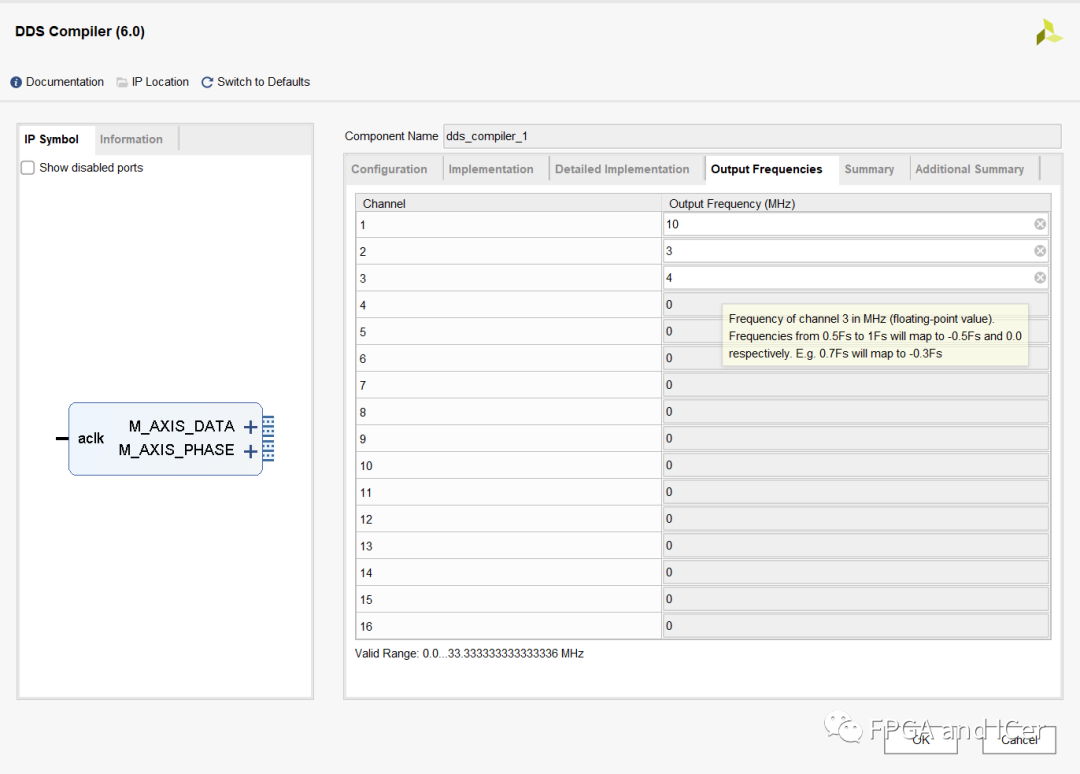

重新打开IP配置界面或者新建一个DDS IP,修改通道数,这里设置为3。 使能相位输出信号,查看下相位变化情况。 因为DDS的IP核多通道之间是分时复用的,所以在细节实现配置界面最好使能通道ID以供进行正常输出单个通道的信号波形。 其余可以保持默认。

配置输出频率为10MHz、3MHz、4MHz。

配置完成点击OK,对模块进行例化。

顶层调用

顶层模块调用代码如下:

module top(

input clk

);

wire m_axis_data_tvalid_ch1;

wire [7:0] m_axis_data_tdata_ch1;

wire m_axis_data_tvalid_ch3;

wire [7 : 0] m_axis_data_tdata_ch3;

wire [1 : 0] m_axis_data_tuser_ch3;

wire m_axis_phase_tvalid_ch3;

wire [31 : 0] m_axis_phase_tdata_ch3;

wire [1 : 0] m_axis_phase_tuser_ch3;

//多通道测试

dds_compiler_1 multi_ch_dds(

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_ch3), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata_ch3), // output wire [7 : 0] m_axis_data_tdata

.m_axis_data_tuser(m_axis_data_tuser_ch3), // output wire [1 : 0] m_axis_data_tuser

.m_axis_phase_tvalid(m_axis_phase_tvalid_ch3), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata_ch3), // output wire [31 : 0] m_axis_phase_tdata

.m_axis_phase_tuser(m_axis_phase_tuser_ch3) // output wire [1 : 0] m_axis_phase_tuser

);

仿真测试

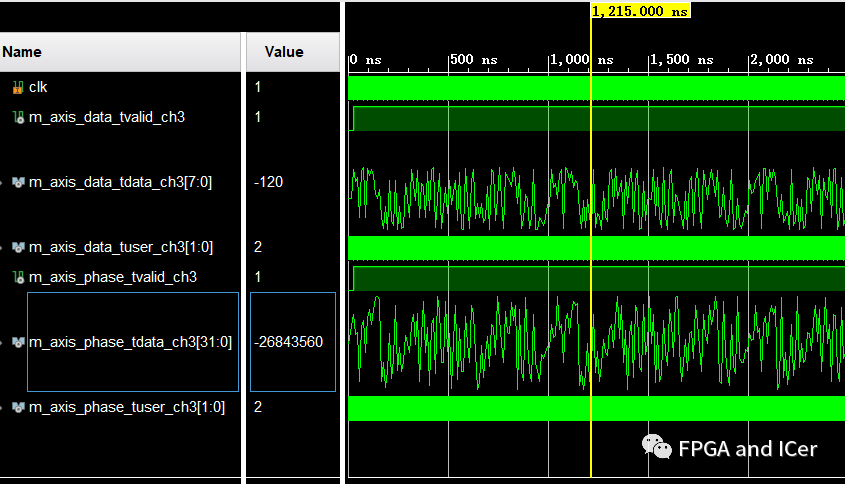

仿真文件可以保持单通道测试不变,点击运行行为级仿真,添加信号波形可观察到下面的情况。 数据并不是直接得到的正弦波形,而是杂乱无章的。

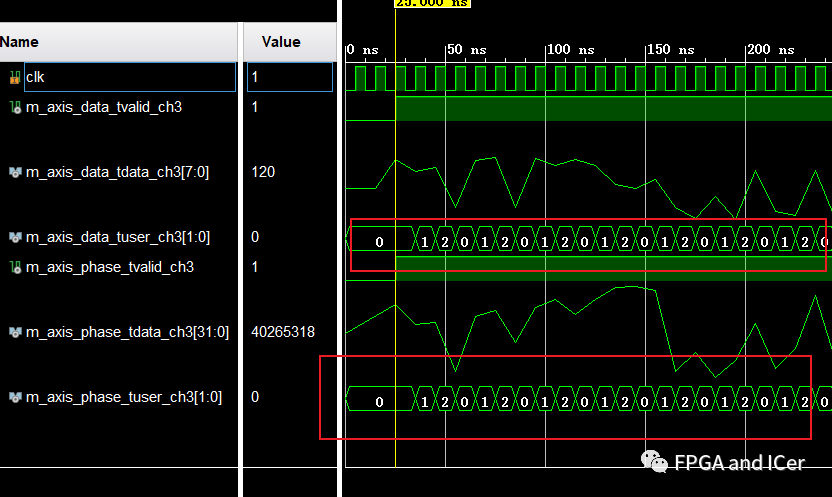

放大tuser信号可观察到,数据和相位通道的tuser信号是周期变化的,这里的tuser信号是代表IP设置中的chen ID,所以是分时复用输出3个通道的信号所以要编写简单逻辑对信号进行分选。

顶层模块修改

可根据tuser为判断条件对输出数据进行一步寄存,从而得到三个通道的波形数据。 代码如下:

module top(

input clk

);

//多通道测试

dds_compiler_1 multi_ch_dds(

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_ch3), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata_ch3), // output wire [7 : 0] m_axis_data_tdata

.m_axis_data_tuser(m_axis_data_tuser_ch3), // output wire [1 : 0] m_axis_data_tuser

.m_axis_phase_tvalid(m_axis_phase_tvalid_ch3), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata_ch3), // output wire [31 : 0] m_axis_phase_tdata

.m_axis_phase_tuser(m_axis_phase_tuser_ch3) // output wire [1 : 0] m_axis_phase_tuser

);

reg [7 : 0] data10MHz;

reg [7 : 0] data3MHz;

reg [7 : 0] data4MHz;

always @(posedge clk) begin

case(m_axis_data_tuser_ch3)

0:data10MHz<=m_axis_data_tdata_ch3;

1:data3MHz<=m_axis_data_tdata_ch3;

2:data4MHz<=m_axis_data_tdata_ch3;

endcase

end

reg [31 : 0] phase10MHz;

reg [31 : 0] phase3MHz;

reg [31 : 0] phase4MHz;

always @(posedge clk) begin

case(m_axis_data_tuser_ch3)

0:phase10MHz<=m_axis_phase_tdata_ch3;

1:phase3MHz<=m_axis_phase_tdata_ch3;

2:phase4MHz<=m_axis_phase_tdata_ch3;

endcase

end

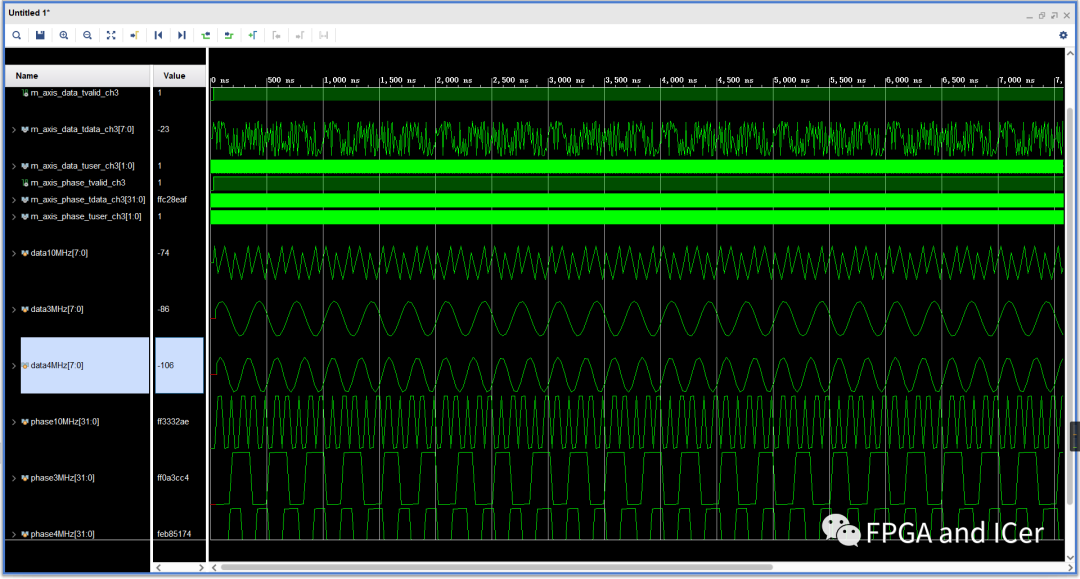

波形如下,从图中可看出,经过逻辑分选后,三个通道的波形输出正常,这里可看到相比单通道输出10MHz信号的正弦波,此时输出的波形不能从时域中看出正弦波形的周期,原因是当启用多个通道后,系统钟要除以通道数量才是对应通道的参考钟,此时设置了100MHz为工作时钟,使能3个通道, 所以单个通道的参考钟为33.333MHz,对于10MHz的信号来说,相当于一个周期仅有三个点,所以无法正常观察到时域特性,但是频域特性依旧存在。

混频实例

混频原理

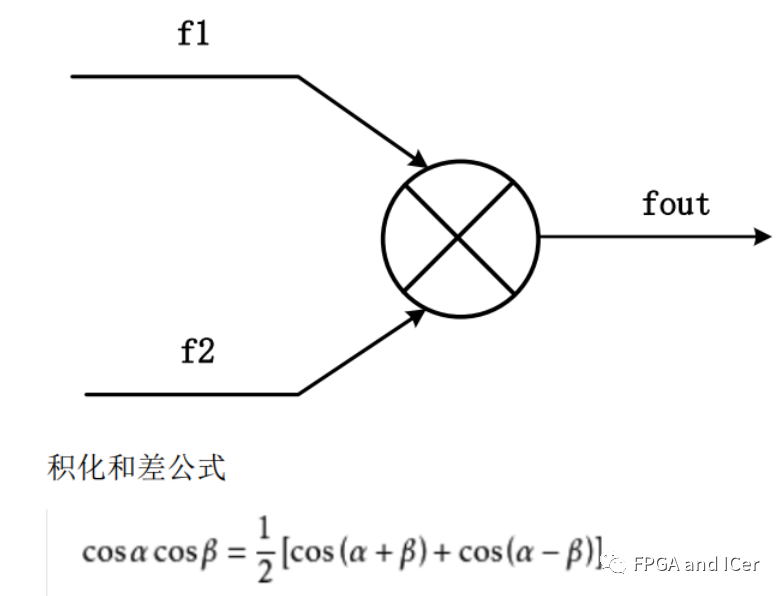

在对输入中频信号需要进行频谱搬移, 需要使用混频操作, 将频谱搬移到高频或者低频, 其实就好比一辆车开在高速路还是低速路, 高频低频就是载波, 承载信息的载体。 在数字信号处理中, 频谱的搬移就是将一个本震信号和一个输入信号, 进行混频, 这样就可以得到一个复合的信号, 这里通过公式开看这个复合信号。

这里的α和β就是指的两个频率信号,当互相相乘得到两个频率信号,一个是α + β,另一个是α – β。 上图的标识的 fout 信号应该是 f1+f2 和 f1-f2 的复合信号 。

使用多通道实例中输出的3MHz和4Mhz,进行混频操作,得到1MHz和7MHz的混合信号。 调用乘法器进行混频乘法操作。

顶层模块

module top(

input clk

);

wire m_axis_data_tvalid_ch3;

wire [7 : 0] m_axis_data_tdata_ch3;

wire [1 : 0] m_axis_data_tuser_ch3;

wire m_axis_phase_tvalid_ch3;

wire [31 : 0] m_axis_phase_tdata_ch3;

wire [1 : 0] m_axis_phase_tuser_ch3;

//多通道测试

dds_compiler_1 multi_ch_dds(

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_ch3), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata_ch3), // output wire [7 : 0] m_axis_data_tdata

.m_axis_data_tuser(m_axis_data_tuser_ch3), // output wire [1 : 0] m_axis_data_tuser

.m_axis_phase_tvalid(m_axis_phase_tvalid_ch3), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata_ch3), // output wire [31 : 0] m_axis_phase_tdata

.m_axis_phase_tuser(m_axis_phase_tuser_ch3) // output wire [1 : 0] m_axis_phase_tuser

);

reg [7 : 0] data10MHz;

reg [7 : 0] data3MHz;

reg [7 : 0] data4MHz;

always @(posedge clk) begin

case(m_axis_data_tuser_ch3)

0:data10MHz<=m_axis_data_tdata_ch3;

1:data3MHz<=m_axis_data_tdata_ch3;

2:data4MHz<=m_axis_data_tdata_ch3;

endcase

end

reg [31 : 0] phase10MHz;

reg [31 : 0] phase3MHz;

reg [31 : 0] phase4MHz;

always @(posedge clk) begin

case(m_axis_data_tuser_ch3)

0:phase10MHz<=m_axis_phase_tdata_ch3;

1:phase3MHz<=m_axis_phase_tdata_ch3;

2:phase4MHz<=m_axis_phase_tdata_ch3;

endcase

end

//混频测试

wire [15 : 0] mixer_singal;

mult_gen_0 mult_mixer (

.CLK(clk), // input wire CLK

.A(data3MHz), // input wire [7 : 0] A

.B(data4MHz), // input wire [7 : 0] B

.P(mixer_singal) // output wire [15 : 0] P

);

endmodule

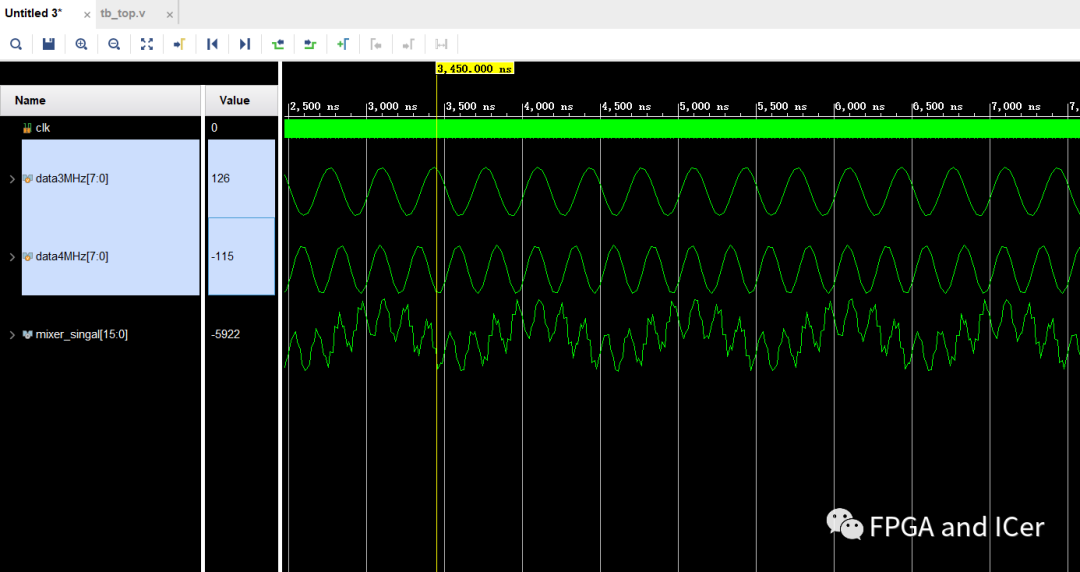

仿真测试

仿真文件可以保持单通道测试不变,点击运行行为级仿真,添加信号波形修改波形设置,可得到混频后的信号效果。

-

STM32数字示波器源码+数字信号处理教程、配套实例2025-05-28 293

-

数字信号处理器概论2023-08-07 13508

-

数字信号的产生及处理2018-04-09 998

-

数字信号处理选型和介绍2018-02-05 8438

-

数字信号处理实验指导书(MATLAB版)2016-04-18 806

-

数字信号处理教程2015-12-30 922

-

数字信号处理的FPGA实现2015-12-23 1049

-

数字信号处理及应用_王华奎_部分答案2015-11-17 2468

-

基于FPGA数字信号处理2015-10-30 1146

-

FPGA和DDS在信号源中的应用2015-06-02 10747

-

labview在数字信号中的应用实例2015-04-20 5514

-

数字信号处理器(DSP)2010-01-04 3761

全部0条评论

快来发表一下你的评论吧 !