FPGA AXI4协议学习笔记(一)

描述

1.关于AXI协议

AMBA AXI协议支持高性能、高频系统设计。

AXI协议:

•适用于高带宽和低延迟的设计;

•提供高频操作,无需使用复杂的连线桥接;

•满足多器件的接口要求;

•适用于具有高初始访问延迟的内存控制器;

•提供灵活的互连架构;

•向后兼容现有的AHB和APB接口。

AXI协议的主要特性是:

•独立的地址/控制和数据阶段

•使用字节控制支持不对齐的数据传输;

•使用基于突发的传输(burst),只需要发出起始地址;

•独立的读和写数据通道,可以提供低成本的直接内存访问(DMA);

•支持发出多个传输地址;

•支持乱序传输;

•允许轻松添加配置阶段,以提供定时关断(AXI支持低功耗扩展模式)。

2.AXI 架构

AXI协议是基于突发传输的(burst-based),并定义了以下独立的传输通道:

•读取地址传输通道

•读取数据传输通道

•写地址传输通道

•写入数据传输通道

•写响应传输通道

地址通道携带描述要传输的数据性质的控制信息。 数据在主从之间通过以下方式传输:

•写数据通道,用于将数据从主端传输到从端。 在写事务中,从端使用写响应通道向主机发送完成传输的信号。

•读取数据通道,将数据从从端传输到主机。

AXI协议:

•允许在实际数据传输之前发出地址信息;

•支持多个未完成的传输事务;

•支持乱序传输。

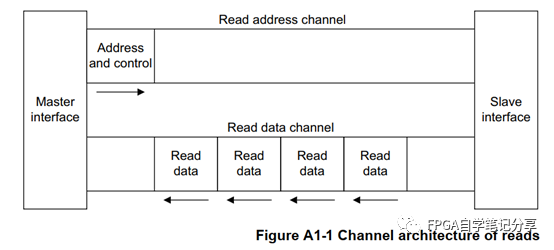

读传输使用读地址和读数据通道进行读操作的过程如下图所示:

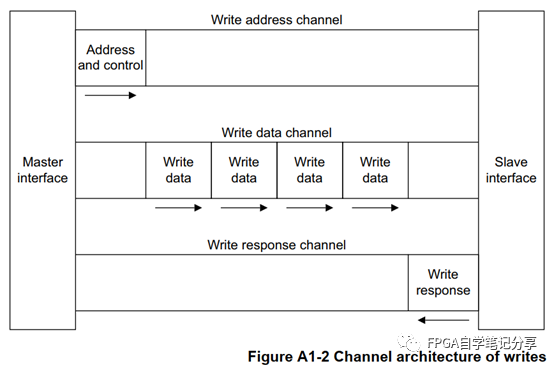

写传输使用写地址、写数据通道和响应通道进行读操作的过程如下图所示:

信息源端使用VALID信号来显示通道上何时有有效地址、数据或控制信息可用。 目的端使用READY信号来显示它何时可以接受信息。 读数据通道和写数据通道都包括一个LAST信号,以指示事务中最终数据项的传输。

读和写地址通道:

读写传输都有自己的地址通道。 适当的地址通道携带传输所需的所有地址和控制信息。

读数据通道:

读数据通道携带从端到主端的读数据和读响应信息,包括:

•数据总线,可以是8、16、32、64、128、256、512或1024位宽;

•一个读响应信号,指示读事务的完成状态。

写数据通道:

写数据通道携带从主机到从主机的写数据,包括:

•数据总线,可以是8、16、32、64、128、256、512或1024位宽;

•字节有效信号为每8个数据位,表明哪些字节的数据是有效的。

写数据通道信息总是被视为缓冲的,这样主端就可以执行写传输,而不需要等待从端确认。

写响应信道:

从端使用写响应通道来响应写传输。所有写传输都需要在写响应通道上发出完成信号。写传输完成时,写响应只对一个完全的传输发出响应信号,而不是对传输中的每个数据传输发出响应信号。

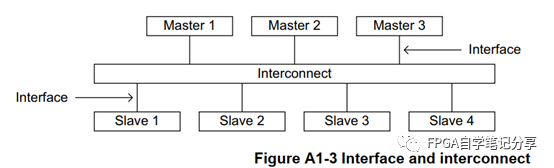

3.AXI总线的互联:

AXI协议提供了一个单独的接口定义,用于以下接口:

主机和互联接口之间的连接;

从机和互连接口之间的连接;

主机和从机之间连接;

AXI的连接接口如下:

AXI的拓扑结构,大多数系统使用AXI以下三种互连拓扑之一:

•共享地址和数据总线;

•共享地址总线和多个数据总线;

•多层,具有多个地址和数据总线;

在大多数系统中,地址通道带宽需求明显小于数据通道带宽需求。这样的系统可以通过使用多个数据总线的共享地址总线来实现并行数据传输,从而在系统性能和互连复杂性之间实现良好的平衡。

-

AMBA AXI4接口协议概述2024-10-28 1802

-

漫谈AMBA总线-AXI4协议的基本介绍2024-01-17 4598

-

SoC Designer AXI4协议包的用户指南2023-08-10 767

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3285

-

AXI4-Lite协议简明学习笔记2023-06-19 6005

-

FPGA AXI4协议学习笔记(二)2023-05-24 3101

-

AXI4协议五个不同通道的握手机制2023-05-08 2321

-

AXI3与AXI4写响应的依赖区别2023-03-30 2121

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3332

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 11016

-

深入AXI4总线一握手机制2021-03-17 1300

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7640

-

AXI4接口协议的基础知识2020-09-23 7300

全部0条评论

快来发表一下你的评论吧 !