FPGA AXI4协议学习笔记(二)

描述

上文FPGA IP之AXI4协议1_协议构架对协议框架进行了说明,本文对AXI4接口的信号进行说明:

1.全局信号

ACLK,ARESETn,AXI所有信号都在时钟的上升沿采样.

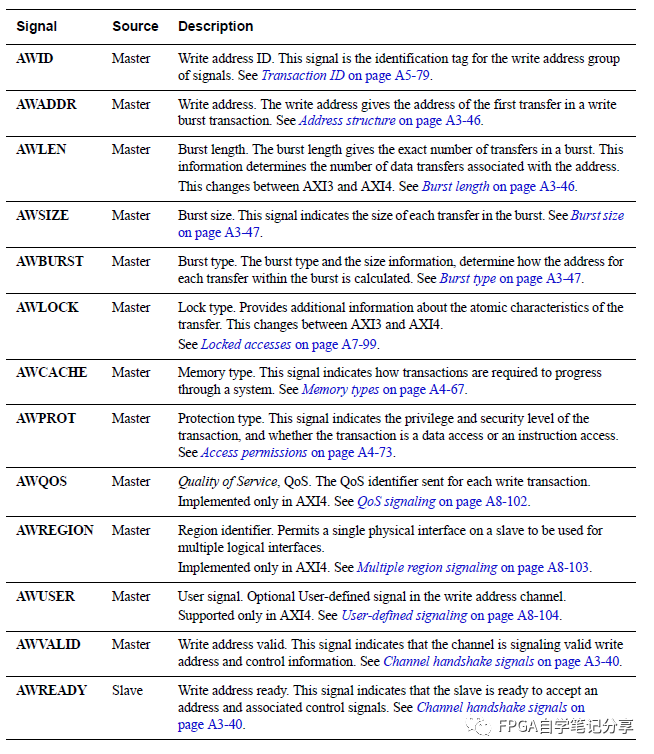

2.写地址通道信号

AWID Master 写地址ID。该信号是信号写地址组的标识标签。

AWADDR Master 写地址。写地址给出写突发事务中第一个传输的地址。

AWLEN Master爆发长度。突发长度给出了突发中传输的确切数量。此信息确定与该地址关联的数据传输数量。这在AXI3和AXI4之间发生变化。

AWSIZE Master 突发大小。这个信号表示脉冲中每个传输的大小。

AWBURST Master 爆发类型。突发类型和大小信息决定了如何计算突发中每个传输的地址。

AWLOCK Master 锁类型。提供有关传输的原子特性的附加信息。这在AXI3和AXI4之间发生变化。

AWCACHE Master内存类型。这个信号表明事务如何在系统中进行。

AWPROT Master 保护类型。该信号指示事务的权限和安全级别,以及该事务是数据访问还是指令访问。

AWQOS Master服务质量,QoS。为每个写事务发送的QoS标识符。仅在AXI4中实现

AWREGION Master区域标识符。允许从服务器上的一个物理接口用于多个逻辑接口。

仅在AXI4中实现。

AWUSER Master 用户信号。可选写地址通道中用户自定义的信号。仅在AXI4中支持。

AWVALID Master写地址有效。该信号表明通道正在发出有效的写地址和控制信息。

AWREADY Slave 写地址准备就绪。这个信号表明从机已经准备好接受一个地址和相关的控制信号。

官网文档如下:

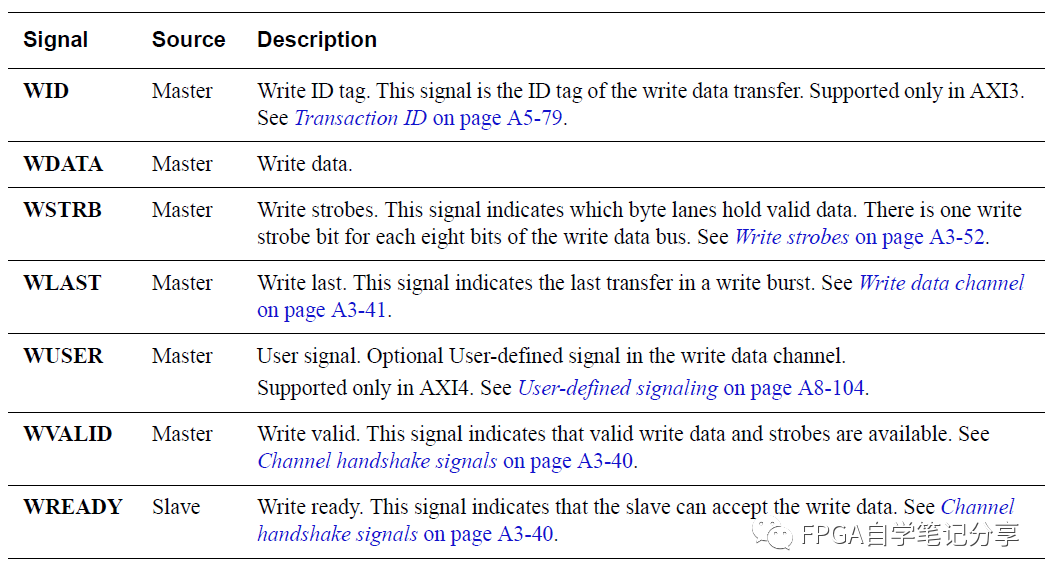

3.写数据通道信号

WID Master写ID标签。这个信号是写入数据传输的ID标记。仅在AXI3中支持。

WDATA Master写数据。

WSTRB Master写byte有效标注。这个信号指示哪些字节通道保存有效数据。写数据总线的每八位有一个写标志位。

WLAST Master最后写。这个信号表示写突发中的最后一次传输。

WUSER Master用户信号。可选写入数据通道中用户自定义的信号。仅在AXI4中支持。

WVALID Master写有效。此信号表示有效的写数据和频闪灯可用。

WREADY Slave 写准备就绪。这个信号表示从机可以接受写数据。

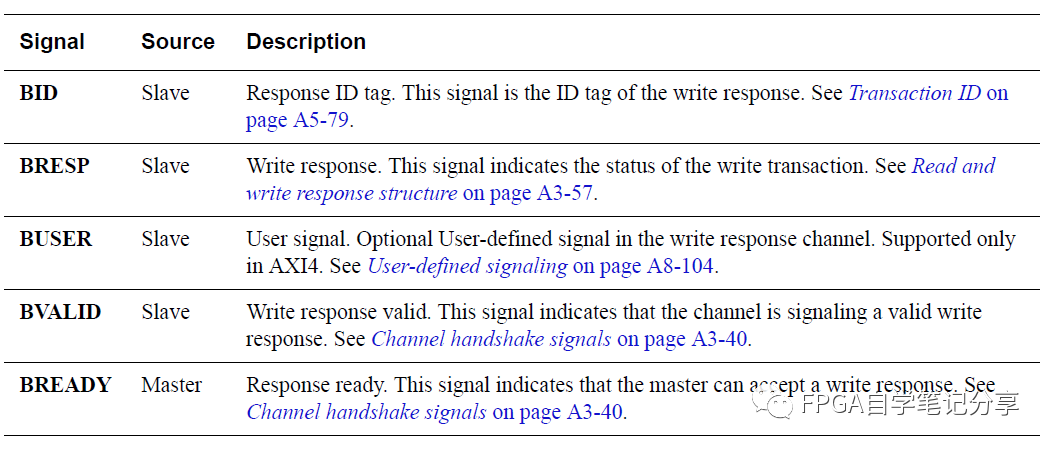

4.写响应通道信号

BID Slave响应ID标记。这个信号是写响应的ID标记。

BRESP Slave 写响应信号。这个信号指示写事务的状态。

BUSER Slave用户信号。可选写响应通道中用户自定义的信号。仅在AXI4中支持。

BVALID Slave写响应有效。此信号表示通道正在发出有效的写响应信号。

BREADY Master响应准备就绪。这个信号表明主机可以接受写响应。

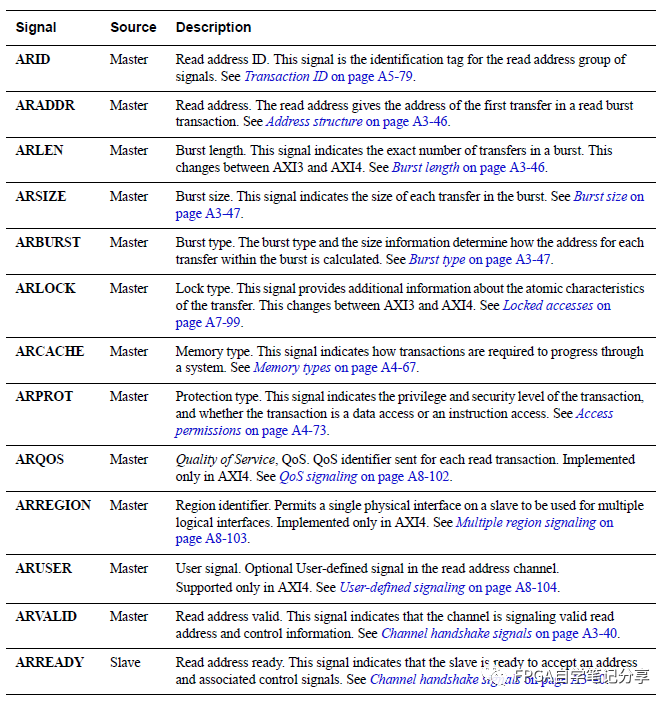

5.读地址通道

和写地址通道完全相同:

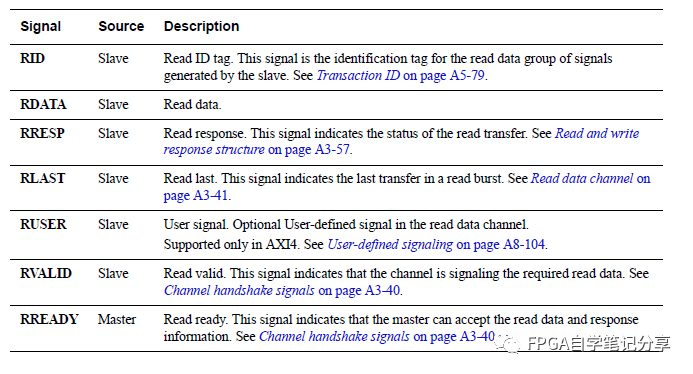

6.读数据通道信号

RID Slave读ID标签。这个信号是从机产生的信号的读数据组的标识标签。

RDATA Slave读数据。

RRESP Slave读响应。这个信号表示读传输的状态。

RLAST Slave最后读取。这个信号表示读突发中的最后一次传输。

RUSER Slave从用户信号。可选读数据通道中用户自定义的信号。仅在AXI4中支持。

RVALID Slave读有效。该信号表示通道正在发送所需的读取数据的信号。

RREADY Master读准备就绪。该信号表示主机可以接受读取数据和响应信息。

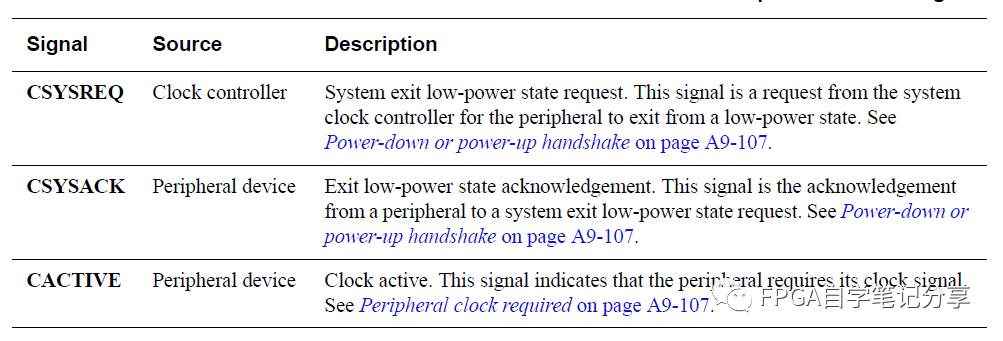

7.低功耗接口信号

CSYSREQ Clock controller 系统退出低电状态请求。这个信号是来自系统时钟控制器的一个请求,要求外设退出低功耗状态。

CSYSACK Peripheral device 退出低电状态确认。此信号是从外设到系统退出低功耗状态请求的确认。

CACTIVE Peripheral device 时钟有效。这个信号表明外围设备请求时钟信号。

-

AMBA AXI4接口协议概述2024-10-28 1748

-

SoC设计中总线协议AXI4与AXI3的主要区别详解2024-05-10 13969

-

漫谈AMBA总线-AXI4协议的基本介绍2024-01-17 4553

-

SoC Designer AXI4协议包的用户指南2023-08-10 744

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3250

-

AXI4-Lite协议简明学习笔记2023-06-19 5955

-

FPGA AXI4协议学习笔记(一)2023-05-24 2155

-

AXI4协议五个不同通道的握手机制2023-05-08 2274

-

AXI3与AXI4写响应的依赖区别2023-03-30 2069

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3298

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10927

-

ZYNQ中DMA与AXI4总线2020-11-02 5287

-

AXI4接口协议的基础知识2020-09-23 7235

全部0条评论

快来发表一下你的评论吧 !