FPGA AXI4协议学习笔记(三)

描述

上文FPGA IP之AXI4协议1_信号说明把AXI协议5个通道的接口信息做了说明,本文对上文说的信号进行详细说明。

1.时钟和复位

每个AXI接口使用一个时钟信号ACLK。所有输入信号都在ACLK的上升沿上采样,所有输出信号的变化都必须发生在ACLK上升沿之后。在主接口和从接口上,输入和输出信号之间不能出现组合逻辑路径。

AXI协议使用低有效的复位信号:ARESETn。复位信号可以异步使能,但是去使能必须与ACLK的上升边同步。在复位信号被拉低后,接口信号要做以下动作要求:

•主端必须驱动ARVALID, AWVALID和WVALID 为低

•从端必须驱动RVALID和BVALID 为低

•所有其他信号都可以被驱动到任意值。

复位信号拉高后,主控制器被允许开始驱动ARVALID、AWVALID或WVALID 变高的最早时间点是在ARESETn为HIGH后的上升ACLK边缘。

2.基本的读写操作

握手过程

所有五个事务通道都使用相同的VALID/READY握手过程来传输地址、数据和控制信息。这种双向流控制机制意味着主端和从端都可以控制信息在主和从之间移动的速率。当地址、数据或控制信息可用时,源端生成VALID信号。目的地生成READY信号,表示它可以接受该信息。只有当VALID和READY信号都为HIGH时,才会发生传输。

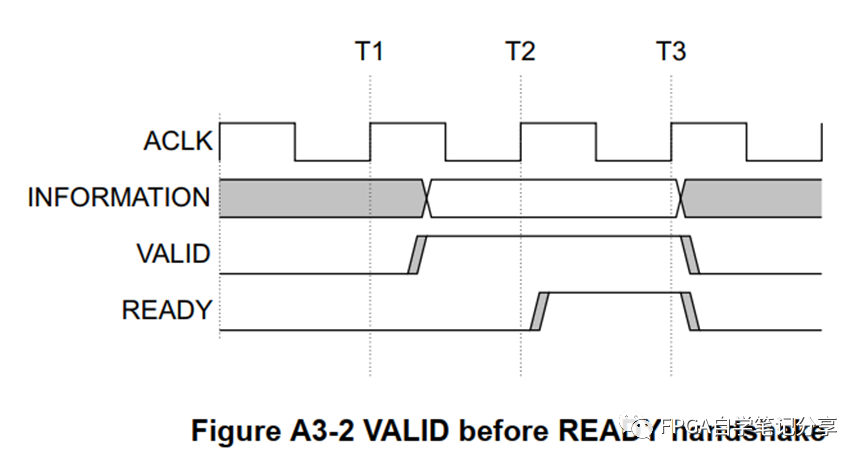

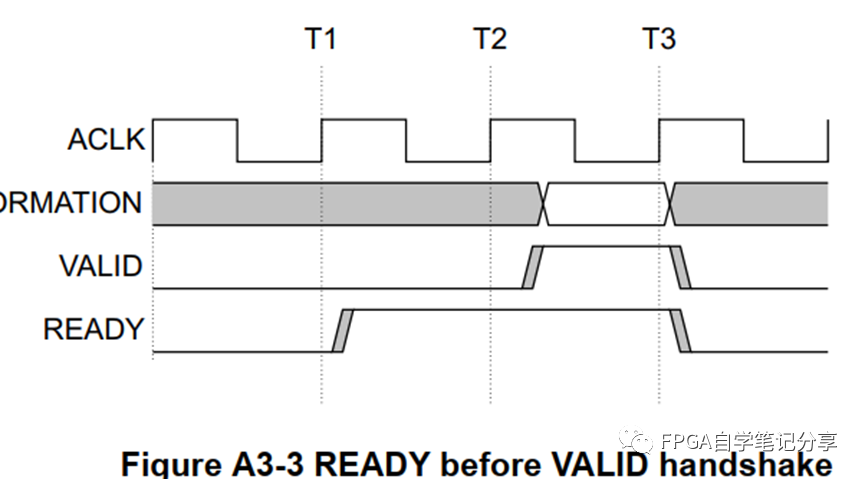

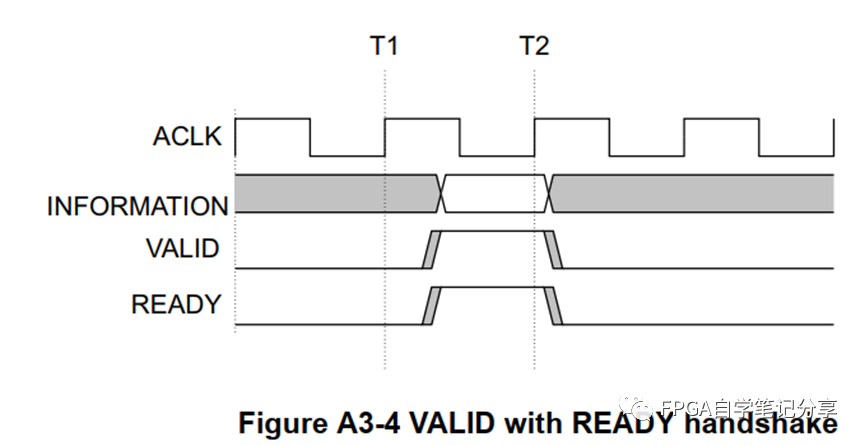

握手过程中的VALID/READY信号支持三种模式:VALID在READY之前、VALID在READY之后、VALID和READY同时到达:

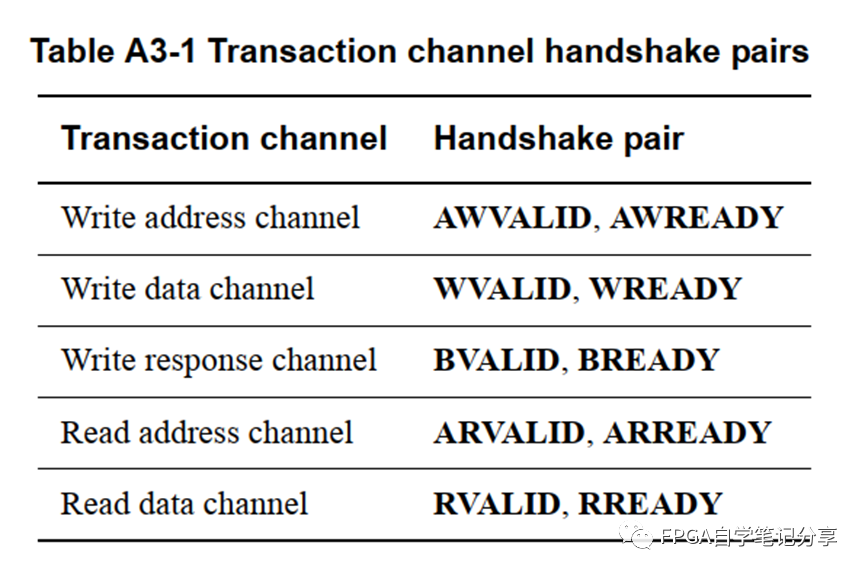

VALID和READY信号的握手过程是AXI协议最基本的要求,AXI协议5个通道均有自己的VALID和READY信号:

写地址通道 :只有当主端准备好有效的地址和控制信息后AWVALID信号才会被拉高,并将持续为高保持到从端的AWREADY信号拉高后才会拉低。AWREADY信号的默认状态可以是高或者低,协议推荐默认状态为高,当AWREADY为高时,slave必须能够接收有效的地址或者控制信号。(协议不推荐AWREADY信号默认状态为0是因为,默认状态为0时,完成一次握手至少需要2个clk才能完成)

写数据通道 :只有当主端准备好有效的地址和控制信息后WVALID信号才会被拉高,并将持续为高保持到从端的WREADY信号拉高后才会拉低。同样推荐WREADY信号的默认状态为高。当进行一个burst的最后一次传输时WLAST信号要被置高。

写响应通道、读地址通道、读数据通道的VALID和READY要求与上边的相同。

-

AMBA AXI4接口协议概述2024-10-28 1737

-

SoC设计中总线协议AXI4与AXI3的主要区别详解2024-05-10 13950

-

漫谈AMBA总线-AXI4协议的基本介绍2024-01-17 4540

-

SoC Designer AXI4协议包的用户指南2023-08-10 742

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3241

-

AXI4-Lite协议简明学习笔记2023-06-19 5950

-

FPGA AXI4协议学习笔记(一)2023-05-24 2142

-

AXI4协议五个不同通道的握手机制2023-05-08 2264

-

AXI3与AXI4写响应的依赖区别2023-03-30 2061

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3292

-

ZYNQ中DMA与AXI4总线2020-11-02 5277

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7541

-

AXI4接口协议的基础知识2020-09-23 7223

全部0条评论

快来发表一下你的评论吧 !