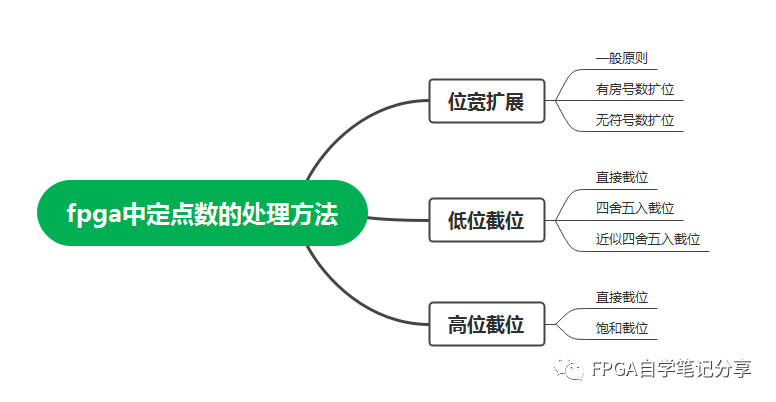

FPGA中定点数的处理方法

可编程逻辑

描述

FPGA中最常用的还是定点化数据处理方法,本文对定点化数据处理方法进行简要探讨,并给出必要的代码例子。

1、一般扩位原则:

1) 加减法运算:扩位位宽=ceil(log2(加法个数))

如:两个加法扩1位,三个四个加法扩2位…

2)乘法运算:结果扩位位宽=两个乘数位宽的和

如:15bit数与14bit相乘结果位宽应为29bit。

3)除法运算:结果扩位位宽=被除数位宽与除数位宽的差

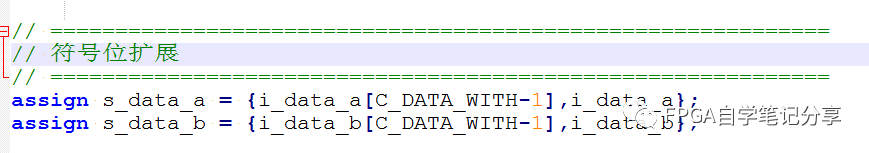

扩位时对于有符号数,高位扩展时扩展符号位,对于无符号数高位扩展时直接补零。因为有符号数高位是符号位,扩位补零会将负数扩展为错误的正数,而无符号数没有符号位,对位最高bit为1的无符号数,扩展符号位同样会导致数据异常。

符号位扩展:

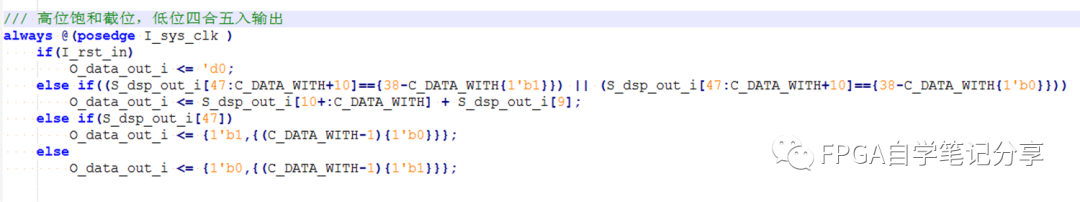

2、高位截位,分为饱和截位和直接截位:

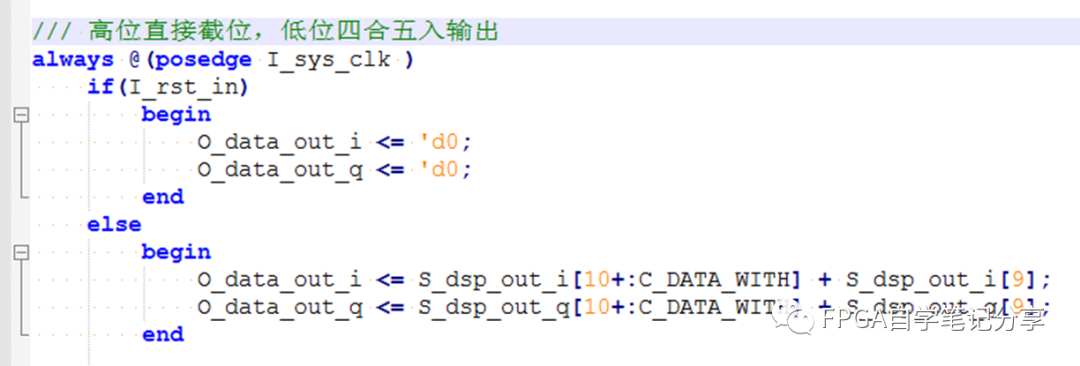

1)高位直接截位,直接抛掉高位保留低位,在确认信号不会溢出的模块使用直接截位的方法,节省资源;

2)高位饱和截位:对计算后的数据进行判断,如果超出位宽,正数输出为最大值,负数输出为最小值;判断方法就是看高位是否完全相同。

3、低位截位:

1)直接截位:功率计算等统计模块会使用,数字信号处理中不会使用,因为这种方式,频域会出现直流。

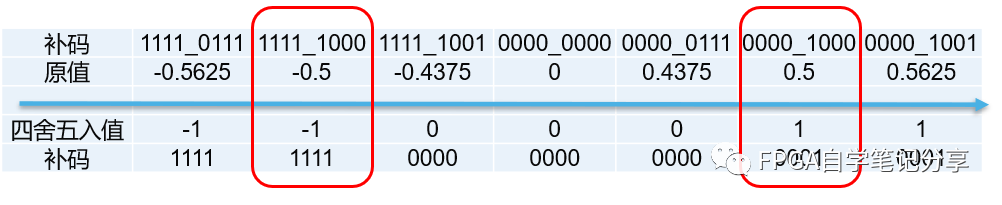

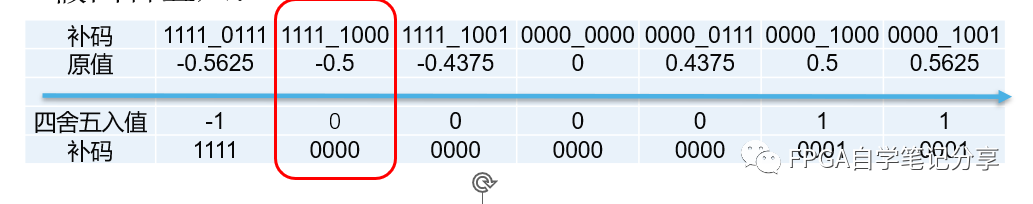

2)四舍五入:如下所示,上一篇文章中说了数据的表示(FPGA数字信号处理之数据的表示),看一看到对于补码,verilog中只针对负数的0.5进行特殊处理即可。

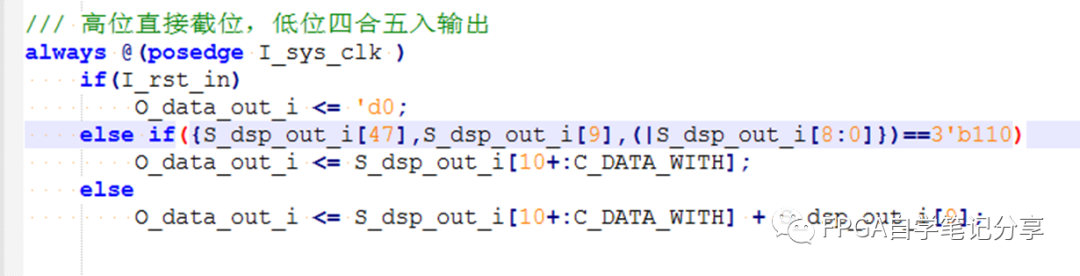

代码如下,代码中会判断信号是否是-n.5,进行处理。

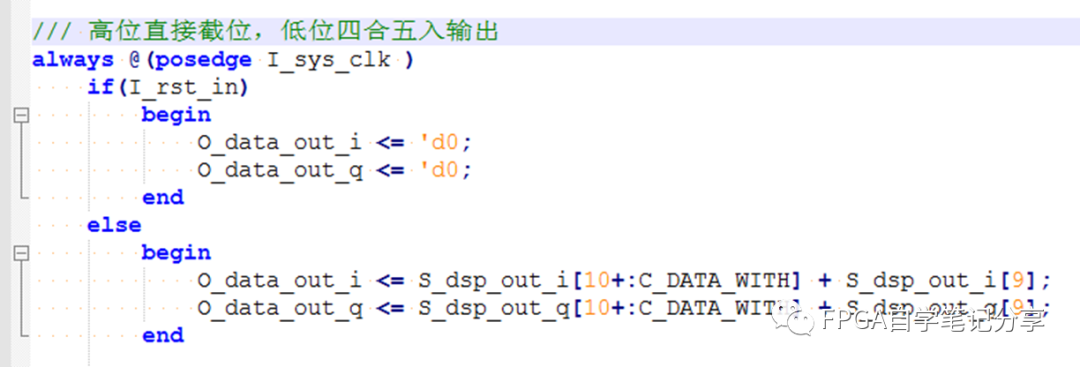

3)近似四舍五入,对于真四舍五入来说,对-0.5的判断逻辑较为复杂,而且有的数据处理对-0.5的要求也不高,此时可以采用近似四舍五入的方法,之前的代码中最常出现的就是这种处理方式:

可以看到这种处理方式下-0.5的值是偏大的。

另外,要注意上一篇文章中多次提到的IEEE 754浮点数标准里面,对于浮点数取整的规定如下

1.就近舍入Round to nearest (even)

2. 向零舍入(Truncate)

3.朝正无穷舍入Round up (toward +∞)

4.朝负无穷舍入Round down (toward −∞)

python等默认使用的就是 就近舍入Round to nearest (even) 处理方法,python中的计算结果为:

round(0.5)= 0

round(1.5)=2

这一点大家做算法时要注意一下。

-

详解FPGA定点数计算方法2025-12-02 678

-

定点数表示实数的方法以及定点数在硬件上的运算验证2025-10-28 192

-

固定点数运算案例的程序2025-12-12 94

-

浮点数与定点数2013-03-27 3344

-

【安富莱——DSP教程】第7章 DSP定点数和浮点数(重要)2015-06-03 9042

-

第7章 DSP定点数和浮点数2016-09-22 4387

-

6618虚拟定点数学库IQmath2018-06-21 2566

-

verilog程序定点数的资料2019-03-27 2408

-

DSP功能函数-定点数互转2021-08-11 1924

-

功能函数中的浮点数转换为定点数2021-08-17 1729

-

定点数和浮点数的区别是什么2022-02-21 2214

-

LabVIEW中定点数有什么用途?LabVIEW中定点数应用解析2017-11-16 10417

-

在FPGA里浮点数与定点数表示法原理展示2017-11-18 9360

-

定点数和浮点数在STM32单片机中使用傅里叶(FFT)变换的理解2021-12-24 1958

-

FPGA定点数截位的基本准则2023-06-19 2472

全部0条评论

快来发表一下你的评论吧 !