设计中的轨道分析是一件美丽的事情

描述

ASIC设计流程继续变得越来越复杂,进度压力继续增加,看不到尽头。与权力相关的考虑越来越不那么事后才想到。在过去,在实现设计目标时,满足性能和面积目标通常是设计周期早期阶段的主要目标。一旦获得一些信心,电源规划细节就变得更加重要,通常在流程的后期。事实上,过去芯片的电源完整性和可靠性在设计周期的最后阶段得到了照顾,因为它可以这样完成 - 有更多的时间和电源问题可以轻松解决 - 没什么大不了的。因此,电源完整性留给了“电源签核”专家。不幸的是,时代变了。随着对高功率器件的需求不断增加,以及不断缩小的几何形状和对激进先进工艺的支持,越来越需要更早地将电源完整性和可靠性设计到设计流程中。授权设计师尽早解决这些问题变得至关重要。

他们提到,他们通常在设计周期结束时执行电源完整性检查。但是,他们上一次的设计存在问题,因此他们需要重新思考和优化设计流程。他们错过了流片期限,需要重新启动芯片,因为与IR压降相关的电源完整性问题使几乎完成的ASIC设计无法正常工作。他们惊恐万分地得出结论,他们需要找到一种方法来进行早期的功率分析和修复。他们以前不这样做的原因是什么?这是因为没有好的实用解决方案来轻松进行设计中的轨道分析。

传统用户的流被打破。在没有设计内电源完整性分析且结果依赖于独立电源完整性检查的流程中,存在太多的痛苦,可归因于两个组件。

首先,分析步骤很痛苦,因为所需的数据需要从后端工具输出,然后输入到独立的电源签核工具中。设置很痛苦。第二个问题与获取这些结果并以有意义的方式将它们反馈到后端工具有关。为什么会痛呢?根据客户的投诉,他们最终要做的是编写脚本来解析和利用该信息来做一些有意义的事情,并在从日志和报告中提取和处理信息后做一些手动工作。用户一直说的是,这种痛苦是如此之大——“请创建一个设计中的解决方案。

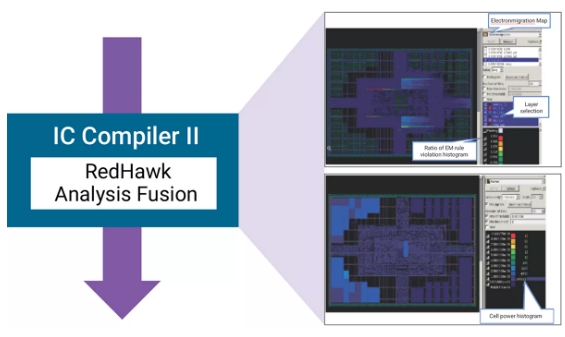

IC Compiler II的新功能是在引擎盖下调用RedHawk Analysis Fusion以运行设计中的轨道分析,就是为了解决这个问题而创建的。使用签核质量引擎,物理设计环境中的用户现在可以更早、更频繁地轻松执行分析,以帮助建立强大的电力网络基础,这样后期阶段就不会出现可能无法修复的缺陷。

通过与 IC 编译器 II 的无缝集成,自动设置可在后台创建必要的环境。由于物理设计和签核使用相同的引擎,因此相关性是完美的。此外,对于物理设计师来说,它易于学习和使用,因此可以毫不费力地尽早运行并经常运行。这种新的流程是设计团队的完美配方 - 这确实是一件多么美好的事情。

审核编辑:郭婷

-

[原创]每天做好一件事2010-05-31 412

-

收获RISC-V峰会潮牌T恤一件2021-07-16 2821

-

中国VR江湖2016年最后一件大事:中国VR体验店联盟成立2016-12-16 861

-

希捷就只做了一件事儿,对此,你怎么看?2018-10-21 1643

-

挖矿到底是一件什么样的事情2019-07-04 1380

-

AI机器学习项目成功的4件重要事情2020-05-04 2038

-

丢失手机后必做的五件事情2021-02-02 7517

-

军用万用表,一件70年前的古董资料下载2021-03-27 1390

-

为什么纳米线对电子产品来说可能是一件大事2022-12-30 1475

-

让上云变成一件简单的事情!华为云企业交换机支持无缝迁移上云2022-12-31 783

-

耐辐射产品系列如何应对近地轨道应用中的挑战2023-07-11 1557

-

把“上云”变成一件简单事情,华为云这款轻量应用服务器大有乾坤2023-11-12 945

全部0条评论

快来发表一下你的评论吧 !