高阻抗缓冲放大器的工作原理

描述

缓冲放大器在大多数应用中也像理想的前置放大器一样工作,但除了前置放大之外,它还起到信号输入级和功率放大器级之间的高阻抗缓冲器的作用。这尤其允许这些类型的前置放大器与极低电流输入信号一起使用,而这些信号无法承受其他低阻抗型前置放大器的负载。

此处所示的缓冲放大器在100kHz时的输入阻抗通常超过1 M,输入阻抗可以简单地调整到低于该点的任何可接受电平。电路的电压增益是单位的。

工作原理

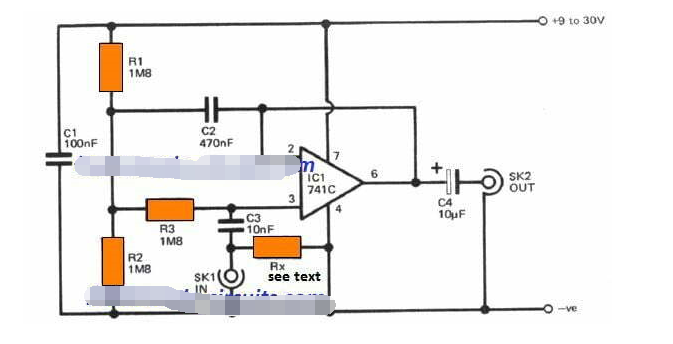

上图显示了高阻抗缓冲放大器的电路图,该单元本质上只是一个运算放大器,用作单位增益的同相放大器。通过将IC1的输出直接耦合到其反相输入,在系统上增加100%的负反馈,以实现所需的单位电压增益以及非常高的输入阻抗。

尽管如此,偏置电路(在这种情况下包括R1至R3)分流放大器的输入阻抗,使电路整体提供的输入阻抗远小于单独的IC1。输入阻抗约为 2.7

兆欧,对于大多数应用,这可能就足够了。

但是,可以消除偏置电阻的分流作用,这就是C2电容“自举”的目标。它将输出信号连接到三个偏置电阻结,因此输入电压的任何调整都通过IC1输出端和三个偏置电阻的交点处的相等电压偏移来平衡。

在IC1角色中,采用基本的741 C运算放大器,如前所述,这提供了通常在100 kHz时超过1兆欧的输入阻抗,这对于任何标准实现来说都足够了。

使用工作放大器实现的更高输入阻抗实际上并不具有任何实际意义,因此本电路中的大多数FET输入系统都存在一些缺点。

首先,当输入打开时,它们实际上具有振荡倾向(当输入连接到器件时,振荡被衰减并消除)。

另一个缺点是,许多FET输入器件的输入功率远高于741

IC等双极器件。通过这种分流动作,在大多数频率下,输入阻抗现在降低,而在低低音和中频下,输入阻抗更高。

为此,需要相对较低的输入阻抗(例如具有许多100

k欧姆和M欧姆的推荐电荷阻抗的拾音器),实现此目的的一种方法是消除C2并将R1的数量更改为R3以获得所需的输入阻抗。

零件清单

印刷电路板布局

-

jf_50240986

2024-01-29

0 回复 举报是否可以这样理解,缓冲器提供一个阻抗转换的通道,输入阻抗无穷大,输出阻抗无穷小,将信号源的信号全部转换成缓冲器的负载电压再转换成缓冲器的信号源? 收起回复

jf_50240986

2024-01-29

0 回复 举报是否可以这样理解,缓冲器提供一个阻抗转换的通道,输入阻抗无穷大,输出阻抗无穷小,将信号源的信号全部转换成缓冲器的负载电压再转换成缓冲器的信号源? 收起回复

-

什么是缓冲放大器2024-02-15 1952

-

缓冲放大器的工作原理和优点2024-01-31 3848

-

电压型缓冲放大器和电流型缓冲放大器的作用?2024-01-29 18652

-

TI技术专访:挖掘高带宽高阻抗缓冲放大器背后的特色技术设计2022-03-12 4390

-

请问怎么为ADC选择合适的缓冲放大器?2021-04-21 2309

-

求教怎样对高阻抗缓冲放大器的输入实现ESD保护?2021-04-20 1872

-

如何理解采样噪声和输出缓冲放大器噪声?2021-03-05 1609

-

高速高输入阻抗稳定缓冲放大器电路2011-10-18 4484

-

高输入阻抗AC缓冲放大器2009-09-28 1436

-

VFO缓冲放大器2009-09-11 1145

-

带缓冲放大器的放大电路图2009-07-13 3510

-

10倍缓冲放大器电路图2009-03-24 3499

-

高输入阻抗缓冲放大器2009-03-20 865

全部0条评论

快来发表一下你的评论吧 !