关于FPGA四输入、六输入基本逻辑单元LUT的一点理解

描述

我们知道FPGA由LUT、IO接口、时钟管理单元、存储器、DSP等构成,我觉得最能代表FPGA特点的就是LUT了。当然不同厂家、同一厂家不同阶段FPGA的LUT输入数量是不同的,随着技术的发展,LUT的输入数量也在增加。

作为FPGA最基本的电路单元,承担着各种电路功能的实现,如果能够理解LUT对电路的实现及影响,对我们进行FPGA开发及优化有着至关重要的作用。如果电路的输入数量远大于LUT的输入数量,LUT在实现电路时必然采用级联方式,级联数量必定会造成电路的延时,有时候会严重制约系统的最高运行频率。

如果我们能够理解好这一点,那么我们在设计电路的时候就要尽量避免级联级数太多,对电路进行优化,比如插入寄存器等方式来减少电路的延时,保证系统的正常运行。

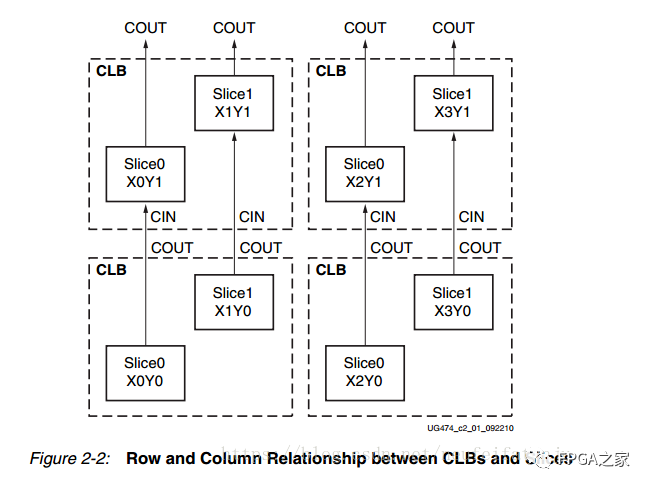

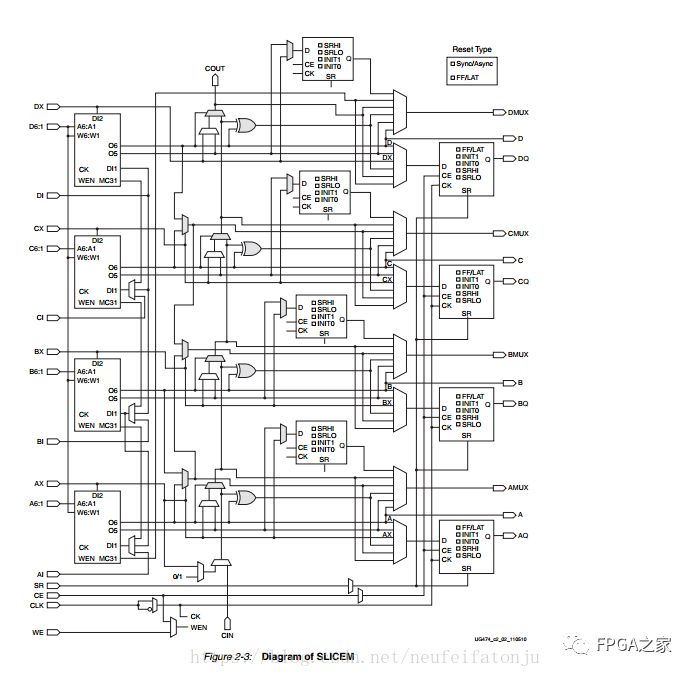

附XILINX 7Series基本逻辑单元框图

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

初识FPGA CLB之LUT实现逻辑函数2023-03-13 4868

-

深入理解 FPGA 的基础结构2024-04-03 3190

-

请教ALTERA的FPGA什么时候开始使用6输入LUT?2016-10-26 4686

-

FPGA基础知识0(查找表LUT和编程方式)2017-05-09 3636

-

FPGA中LUT设计2018-07-30 3500

-

如何在LUT和逻辑元件之间以及逻辑元件和逻辑单元之间进行交换2019-01-08 2661

-

Spartan 6 FPGA LUT中是否有pmos和nmos transisors?2019-08-09 2341

-

请问一下FPGA的LUT到底是如何实现逻辑功能的?2023-04-23 3208

-

#共建FPGA开发者技术社区,为FPGA生态点赞#+2023.11.8+FPGA设计的实践与经验分享2023-11-08 821

-

LUT如何构成逻辑函数2018-10-26 11494

-

vLUT表:写 读地址输入、数据输出 入这里面包括2019-07-13 4498

-

FPGA中实现LUT设计的简介2020-12-29 1637

-

解析数字电路的与、或、非等逻辑是通过 6 输入的查找表实现2021-06-12 7806

-

一文详解xilinx CLB基本逻辑单元2022-04-24 5562

-

逻辑器件四路二输入是什么意思2024-05-30 1664

全部0条评论

快来发表一下你的评论吧 !