GMII to RGMII IP核的一些参数

描述

大家好!今天给大家介绍一下GMII to RGMII IP 核的一些参数的含义。其他IP核参数请看文档pg160。

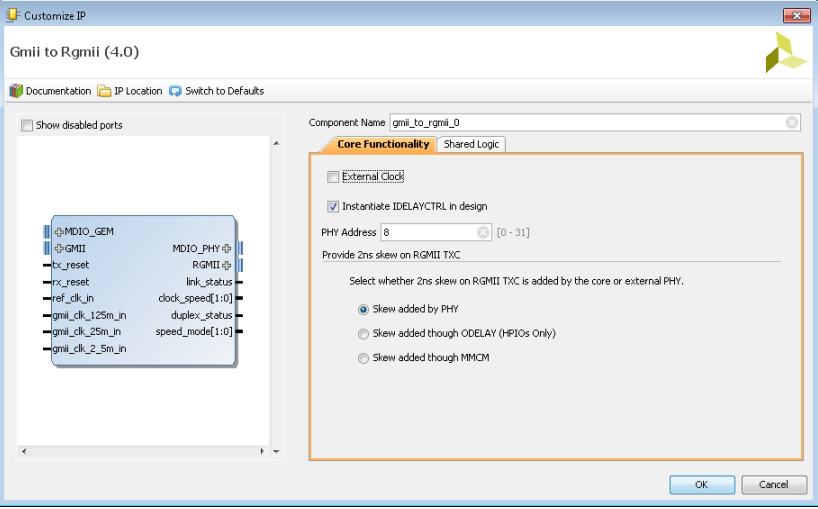

调出IP核后,首先看到的是这样一个界面:

这个界面上主要有以下参数:

组件名称-组件名称用作为核心生成的输出文件的基本名称。名称必须以字母开头,并且可以由以下字符组成:a到z、0到9以及下划线(_)。

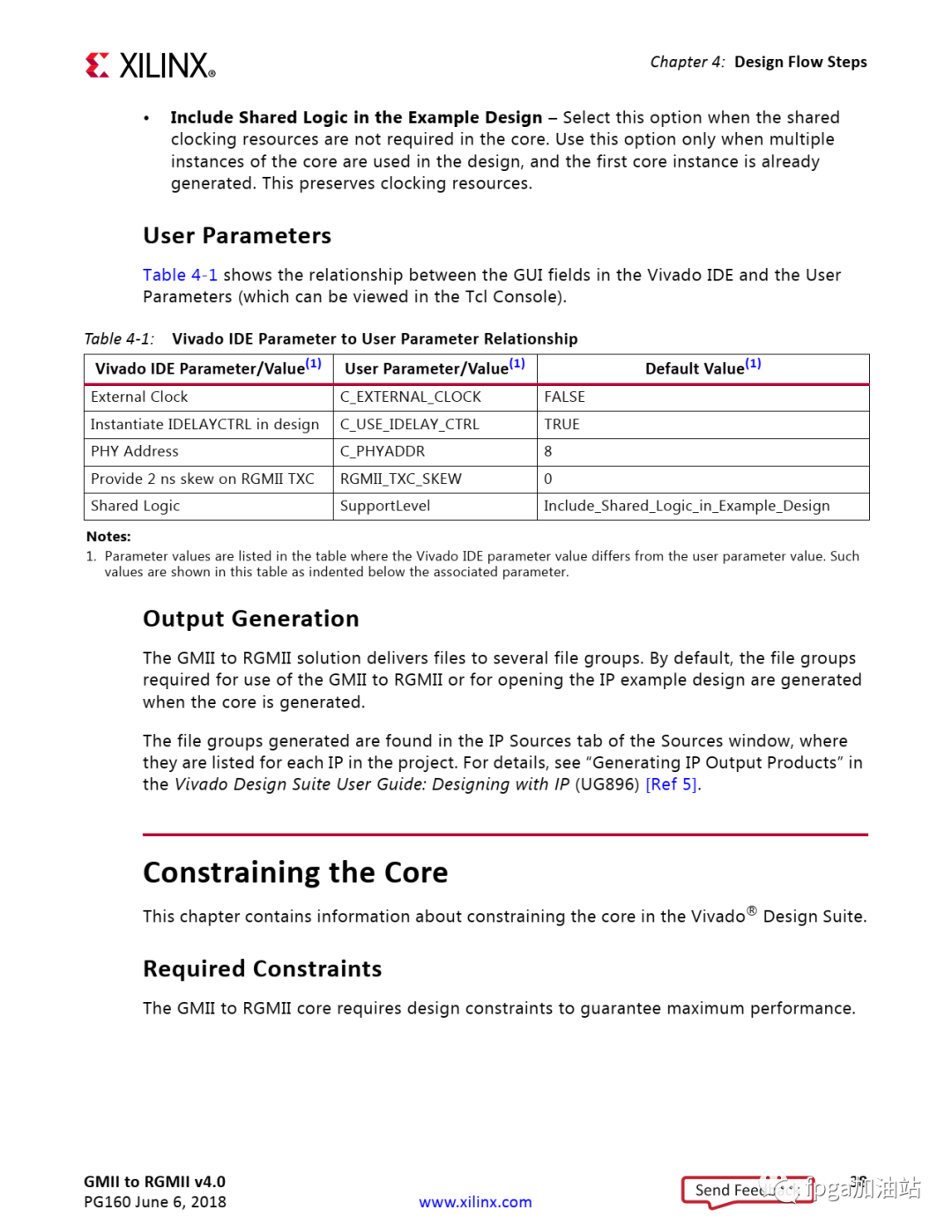

外部时钟-选择此选项可从外部获取GMll时钟。选择时,确保GMII时钟频率适合线路速率:10Mb/s为2.5MHz,100Mb/s为25MHz,1000Mb/s为125MHz。

默认情况下,GMll时钟是在内部生成的。GMll到RGMII IP有一个内置的inclock生成器,用于分别为10Mb/s、100Mb/s和1000Mb/s的操作速度提供2.5MHz、25MHz和125MHz的频率时钟。

在设计中实例化IDELAYCTRL-选择此选项可以实例化核心中的IDELAYCTRL基元。在设计中使用输入/输出延迟基元时,应实例化IDELAYCTRL基元。此核心使用它们,默认情况下选择此选项。

如果您的设计为RGMII I/O映射到的I/O bank实例化了IDELAYCTRL基元,那么您不应该选择此选项。

IDELAYCTRL基元被实例化为共享逻辑的一部分,并且是核心配置中包含共享逻辑的核心的一部分。如果在示例设计配置中的包含共享逻辑中只存在一个核心实例,则需要在设计中实例化IDELAYCTRL基元。

PHY地址-PHY地址是用于识别MDIO事务中的核心的5位地址。有效范围为0到31。此处的PHY地址必须与分配给板载PHY的地址不同。

在RGMII TXC上提供2 ns偏斜-选择此选项可选择RGMII TXC上相对于RGMII TXD添加2 ns偏斜的位置。如果在FPGA中添加偏斜,则可以通过ODELAY(仅存在于设备HPIO中)或通过MMCM添加。

重要提示:只有当RGMll TXC引脚映射到设备上的高性能I/o组时,才能使用ODELAY的选项。

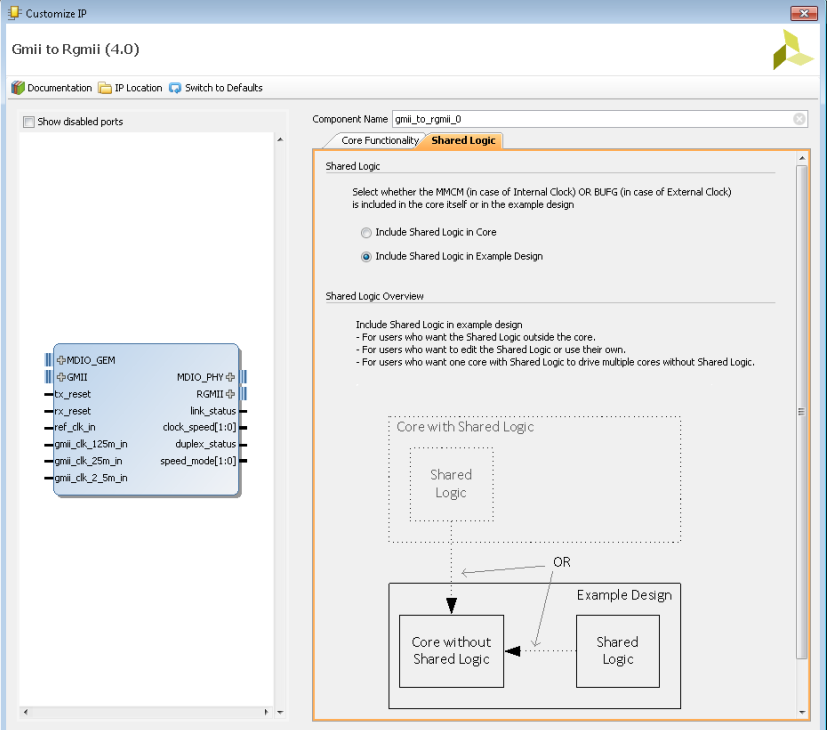

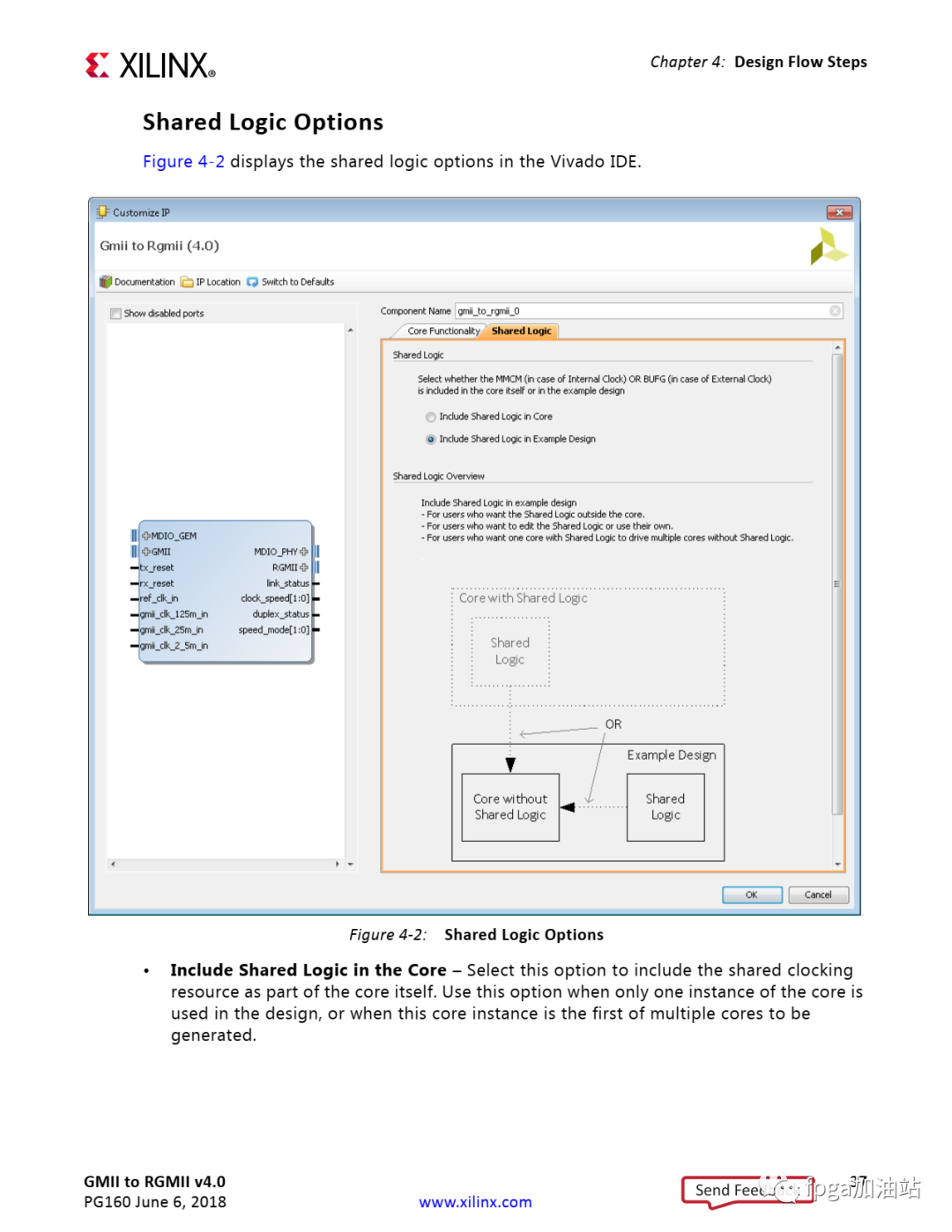

在核心中包括共享逻辑-选择此选项可将共享时钟资源作为核心本身的一部分包括在内。当设计中只使用一个核心实例,或者此核心实例是要使用的多个核心中的第一个时,请使用此选项生成。

在示例设计中包括共享逻辑-当核心中不需要共享锁定资源时,选择此选项。只有在设计中使用了核心的多个实例,并且第一个核心实例已经生成时,才使用此选项。这将保留时钟资源。

经验分享:

这个IP核在实际应用中使用到的频率还是比较高的。虽然它的参数很少,引脚接口大家都比较熟悉,但是在实际应用时却经常出问题。而且有时候明明两个工程师连线、配置一模一样,会出现一个能正常工作,一个不能正常工作的情况。最容易出问题的地方是PHY地址,还要注意要添加对引脚的时序约束。

温馨提示:PG160的中英文文档我已经免费提供给大家,有需要的去这个链接自行保存下载。PG | xilinx中英文文档(最新最全)

左右滑动查看:

-

关于FPGA IP核2024-04-29 0

-

IP核简介2011-07-06 0

-

使用ISE 13.3更改8.1 FIFO IP内核中的一些参数可能有什么问题?2019-06-26 0

-

如何在我的VHDL顶级模块中使用该IP核的一些示例?2020-05-21 0

-

无法摆脱有关GMII到RGMII IP的多时间定时警告?2020-08-26 0

-

GMII和RGMII主要的接口2021-07-29 0

-

RGMII的特点?RGMII与GMII转换电路设计2021-07-29 0

-

RGMII与GMII转换电路该怎样去设计呢2021-11-01 0

-

RGMII接口信号和帧格式_RGMII接口应用框图2020-09-30 31585

-

FPGA控制RGMII接口PHY芯片88E1512网络通信2020-10-15 22653

-

基于RGMII to GMII Bridge以太网接口的参考设计2021-01-10 828

-

VCS独立仿真Vivado IP核的一些方法总结2021-03-22 4231

-

RGMII接口转GMII接口的实现思路2023-06-09 2344

全部0条评论

快来发表一下你的评论吧 !