先进封装之TSV及TGV技术初探(二)

制造/封装

描述

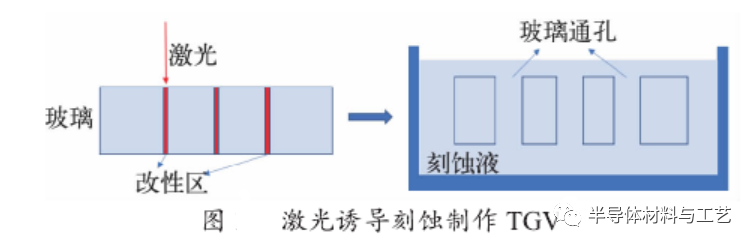

玻璃诱导刻蚀法如下:

1) 使用皮秒激光在玻璃上产生变性区域;2)将激光处理过的玻璃放在氢氟酸溶液中进行刻蚀。

1.2玻璃穿孔填孔技术

类似硅通孔的金属填充方案也可以应用在TGV上。

另外一个将TGV填实的方案是将金属导电胶进行TGV填实。利用金属导电胶的优点是固化后导电通孔的热膨胀系数可以调节,使其接近基材,避免了因CTE不匹配造成的失效。

除了TGV电镀填实外,TGV也可以采用通孔内电镀薄层方案实现电学连接。

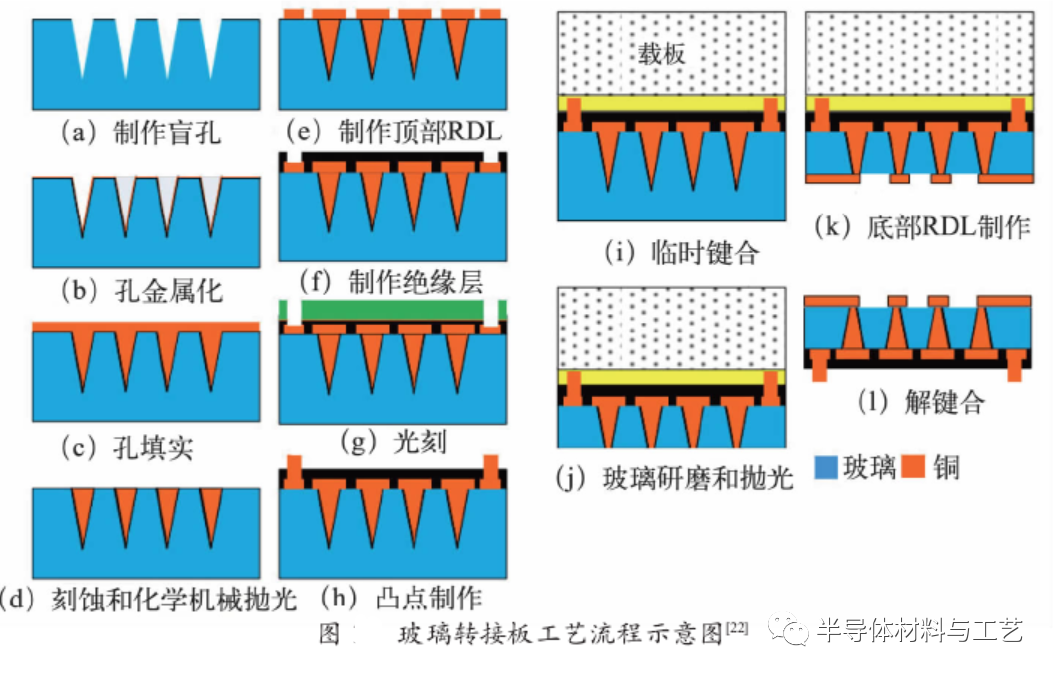

1.3玻璃通孔高密度布线

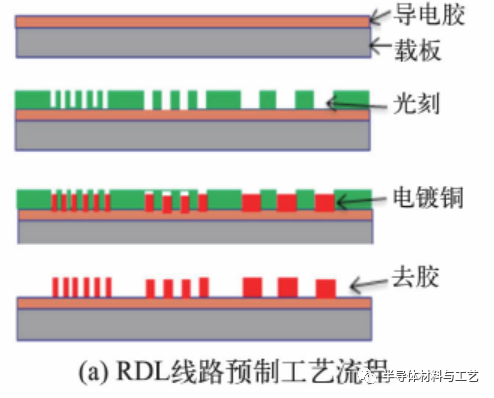

线路转移(CTT)和光敏介质嵌入法,是比较常用的方式。CTT主要包括两个过程。一是精细RDL线预制,每一RDL层可以在可移动载体上单独制造一层薄导电层,并在转移到基板上之前测试或检查细线成品率。精细线路的形成采用细线光刻和电解镀铜的方法,并且以薄铜箔作为镀层的种子层。工艺流程如下:

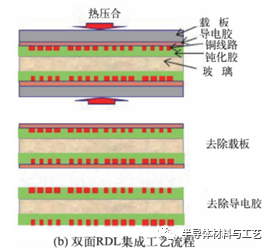

第二步就是将RDL层集成到基板上。RDL层被制造出来后,他们再使用热压合的同时被转移到核心层的两边。步骤如下:

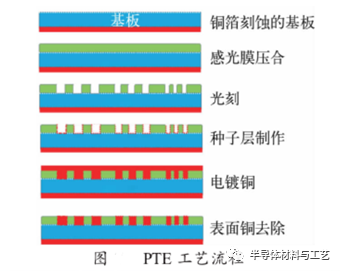

PTE工艺可分为两个不同的步骤,一是在光敏介质层总形成精细的沟槽;二是金属化,包括种子层沉积、电镀和表面除铜。工艺流程如下:

2、 国内外研究现状

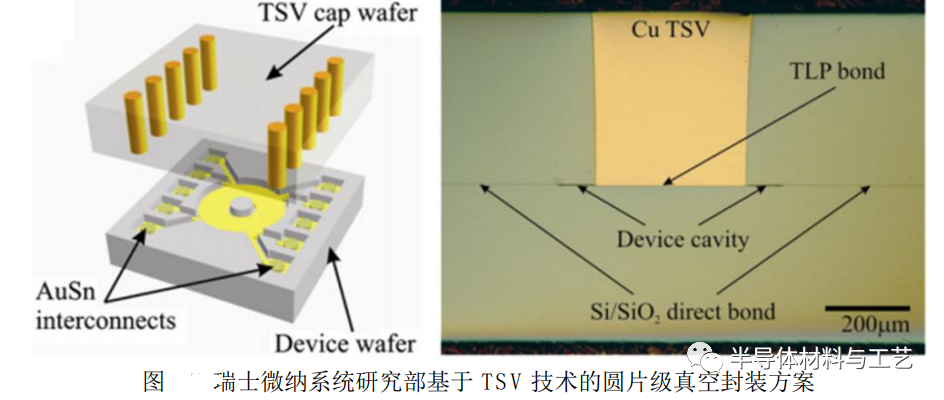

2011年,瑞士的微纳系统研究部提出了如下图所示的基于TSV技术圆片级真空封装方案。该方案由TSV封帽与器件层两部分构成,TSV封帽垂直导通柱是填充在硅通孔中的铜柱。器件层上制作有金锡电极与铜柱相连,从而把电信号从空腔内部的引到空腔外部,最后通过硅-硅直接键合实现密封。该方案气密性很好,但是TSV封帽制作工艺复杂,热应力大(铜柱与硅热失配大),且硅硅键合对键合表面要求质量很高,一般加工过的硅片很难达到此要求。

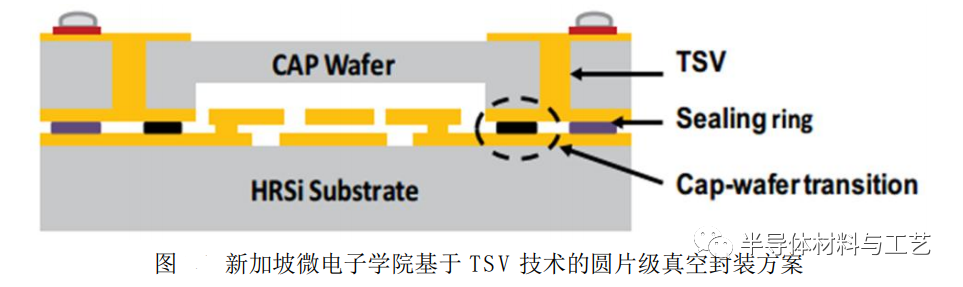

2013年,新加坡微电子学院提出如下图所示基于TSV技术的圆片级真空封装方案。该方案由TSV封帽、硅器件层组成,TSV封帽也是由硅通孔里的铜柱做垂直导通柱,硅器件层上制作有射频结构及金属电极,最后使用AuSn焊料键合实现气密封装。此方案虽然也存在TSV封帽制作工艺复杂,热应力大的问题,但采用焊料键合方式封装,尽管牺牲一定的密封性,但大大降低对TSV键合表面质量的要求,其工业应用范围更广。

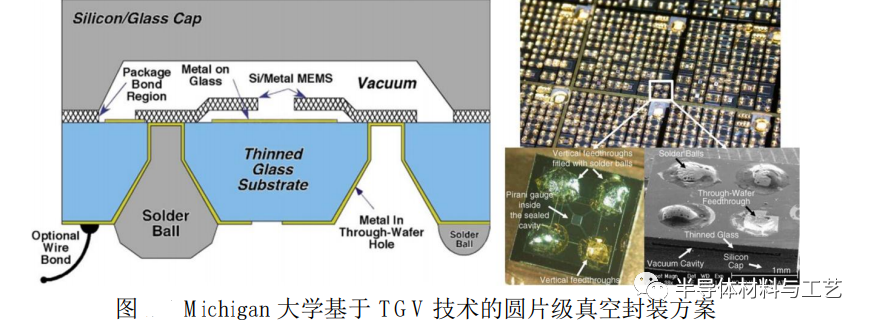

从以上两个TSV例子可以看出,TSV存在工艺复杂,热应力过大的缺点。为解决这些问题,更好实现真空封装,又提出了TGV技术。2008年,美国Michigan大学提出了的一种基于常规工艺TGV技术的圆片级真空封装方案,如下图所示。该方案由封帽,器件层以及基于常规工艺TGV技术衬底三部分构成。封帽可以为硅或玻璃,制作有空腔;器件层是硅结构层。

基于常规工艺TGV技术衬底是在玻璃片上制作电极和通孔,通孔表面沉积有金属层,有的通孔填充焊锡球,用以形成垂直导通柱,把电信号由密封腔中引出。最后通过阳极键合把器件层与TGV衬底键合在一起,形成密封。该方案优点是通过阳极键合形成密封,阳极键合密封性好、热失配小、污染小且一般硅片能达到阳极键合对表面质量的要求。

2010年,挪威的Sensonor Technologies AS提出了结构如下图所示的一种基于玻璃回流TGV技术圆片级真空封装方案封装蝶翼式硅微陀螺。为减少结构应力,提高陀螺仪灵敏度,采用三层对称结构设计,上下两层均为TGV衬底,中间夹硅结构层。基于玻璃回流TGV衬底,是通过高温玻璃回流,然后双面CMP加工制成的。

TGV衬底垂直导通柱即为由回流玻璃隔离出来的硅柱,衬底上不制作金属电极,直接用硅做电极。硅结构层采用Silicon-on-Insulator (SOI)材料和干法刻蚀制作而成,空腔制作在硅可动结构层上,通过硅-玻璃将三者阳极键合在一起,分别有两次,形成密封环境。该封装方案优势凸出,不仅封装应力低,而且TGV衬底工艺简单,密封性好,热适配小,寄生电容小。

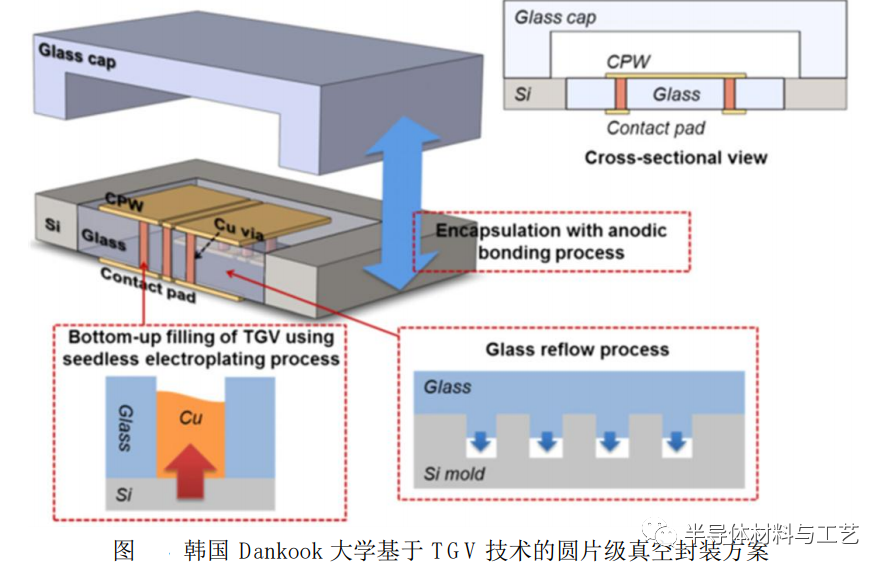

2013年,韩国Dankook大学开发出结构如图所示的TGV技术圆片级真空封装方案。该方案包括玻璃封帽、CPW器件层以及TGV衬底,腔体制作在玻璃封帽上。其TGV衬底与众不同,先后采用玻璃回流工艺与电镀铜工艺制作。简而言之,为先利用玻璃回流工艺制作硅导通柱,然后去除硅导通柱,用电镀铜作导通柱。CPW器件层制作在衬底密封环范围内,最后封帽与衬底通过硅-玻璃阳极键合形成密封腔,并制作外部的金属焊盘完成引线及封装。该方案电学性能优良,但工艺复杂。

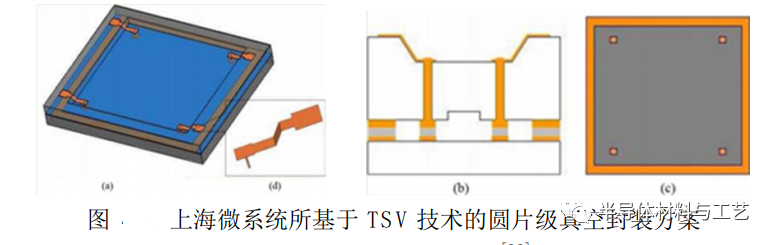

2009年,上海微系统所提出了一种结构如图所示基于TSV技术的圆片级真空封装方案。该方案由TSV封帽与硅衬底两部分组成:TSV封帽采用湿法和干法刻蚀出通孔,通孔中填充铜作为导通柱,导通柱与硅通过隔离层隔离,腔体制作在TSV封帽上。硅衬底上制作有结构,通过Cu-Sn焊料键合与TSV封帽实现密封封装。该方案简单易行,但焊料键合用在圆片级真空封装上会显得键合密封性不够,污染过大。

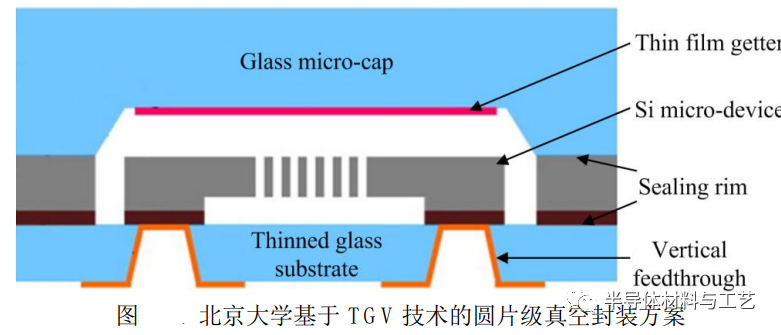

2012年,北京大学提出了结构如图所示一种基于常规工艺TGV技术的圆片级真空封装方案。该方案是典型的三明治式架构,由玻璃封帽、硅可动结构层、TGV衬底三层组成。硅可动结构采用干法刻蚀出可动结构;基于常规工艺TGV衬底采用湿法腐蚀出通孔与金属沉积导通柱等工艺制作而成;空腔制作在封帽上,空腔顶部沉积有吸气剂,保持腔体真空度。最后玻璃封帽、硅可动结构层、TGV衬底通过两次硅-玻璃阳极键合封装在一起。

3、 TGV技术的应用

3.1玻璃基板的三维集成无源元件

玻璃基板具有优异的高频电学性能,因此被广泛的应用于集成无源器件(IPD)之中。2010年,乔治亚理工的封装中心率先完成了基于TGV的滤波器设计与制造,并与相同的硅基电感对比,展现了更好的电学特性。2017年,日月光集团在玻璃基板上实现了面板级的IPD制作工艺。该方案板材翘曲可控制在1mm以内,并且无明显结构剥落分层现象。

3.2嵌入式玻璃扇出与集成天线封装

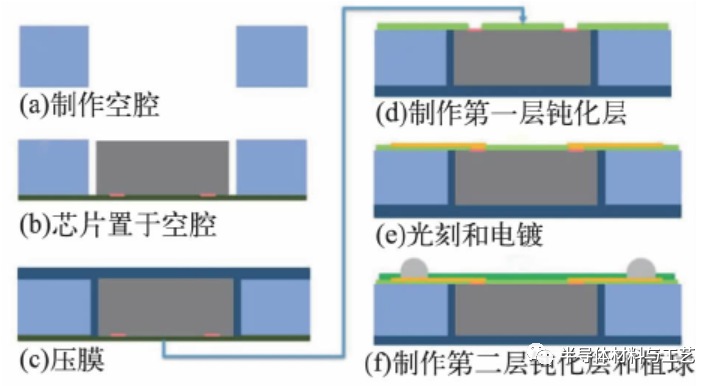

玻璃通孔还可以在玻璃上制作空腔,进而为芯片的封装提供一种嵌入式玻璃扇出(eGFO)的新方案。2017年乔治亚理工率先实现了用于高I/O密度和高频多芯片集成的玻璃面板扇出封装。该技术在70um厚、大小为300mm*300mm的玻璃面板上完成了26个芯片的扇出封装,并有效的控制芯片的偏移和翘曲。2020年云天半导体采用嵌入式玻璃扇出技术开了77GHz汽车雷达芯片的封装,并在此基础上提出了一种高性能的天线封装(AiP)方案。工艺流程如图所示:

在厚度为180um的玻璃晶片中,先采用激光诱导玻璃变性和化学腐蚀工艺形成玻璃空腔,然后将175um高的芯片放入玻璃空腔总。通过复合材料将芯片和玻璃之间的缝隙填压而不产生空隙,同时保护芯片的背面。对晶圆的顶面进行剥离,形成铜RDL,最后进行后续线路制作、球栅阵列(BGA)制作以及晶圆切片。

3.3基于玻璃通孔的MEMS封装

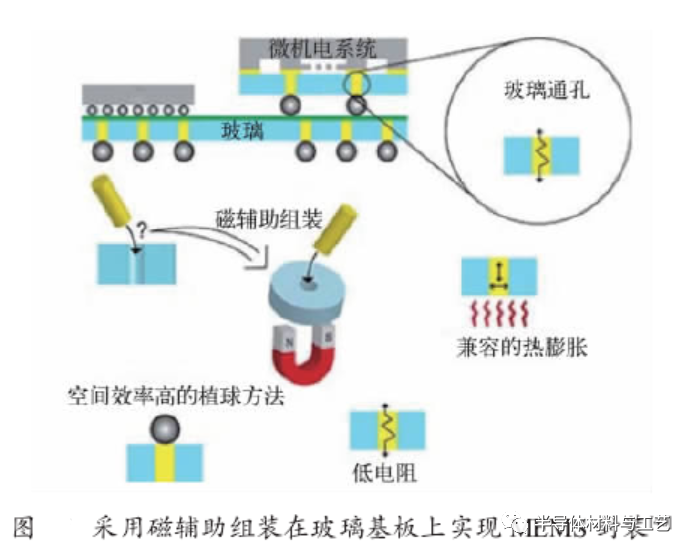

2013年,LEE等利用玻璃穿孔技术实现射频MEMS器件的晶圆级封装,采用电镀方案实现通孔的完全填充,通过该方案制作的射频MEMS器件在20GHz时具有0.197dB的低插入损耗和20.032dB的高返回损耗。2018年,LAAKSO等创造性地使用磁辅助组装的方式来填充玻璃通孔,并用于MEMS器件的封装中。

3.4基于TGV的集成天线

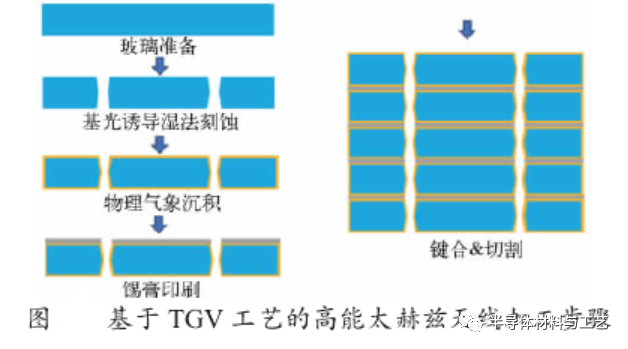

厦门大学的张淼创造性的引入TGV加工波导缝隙天线。首先采用激光诱导刻蚀制备波导缝隙阵列天线玻璃衬底,通过激光在玻璃上诱导产生连续性的变性区,后将变性后的玻璃在稀释氢氟酸总进行刻蚀,由于激光作用处的玻璃氢氟酸中刻蚀速率较快,所以玻璃会成块脱落从而形成目标通孔结构。最终刻蚀后的玻璃穿孔精度为±5μm,远远高于传统机加工的精度。其次,采用物理气相沉积对每层波导缝隙阵列天线玻璃衬底溅射铜层,经过氧等离子体清洗以彻底清除焊盘表面的有机物等颗粒,并使晶圆表面产生一定的粗糙度,为种子层的良好附着创造条件。清洗后的晶圆在烤箱150℃下烘烤60min彻底去除水汽。然后在磁控溅射设备中,晶圆表面溅射一层厚度约为5μm的铜层。最后,采用技术焊料键合技术将5片晶圆键合。用刮刀以及丝网将10μm厚度的锡焊料印刷到晶圆表面,然后在键合机的真空腔室中以240℃的温度加热,以40N的压力压合5min使焊料融化或相互扩散以达到键合的目的。工艺流程度如图:

3.5多层玻璃基板

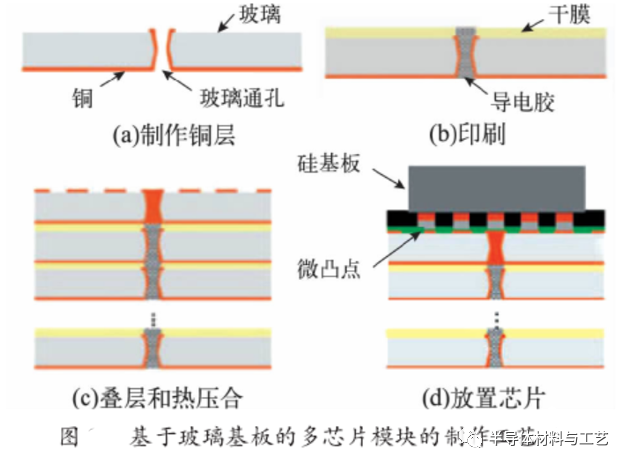

2018年IWAI等使用导电胶填充玻璃通孔,从而实现多层玻璃基板堆叠,在回流过程中,通过该方案制作的多层玻璃基板的翘曲比传统有机基板要小,通过该技术可以实现高密度布线,同时具有较高的可靠性。2019年,IWAI等在多层玻璃基板的技术基础上,完成了一个多芯片封装的结构。其工艺流程如图:

五、目前主要厂商的先进封装进展

目前,国内外主要的代工厂和封测厂都有布局相应的先进封装产能,国外的代工厂和封测厂在技术实力上处于领先地位,在2.5D/3D先进封装的细分领域,在TSV工艺上,台积电和英特尔处于领先地位,在TGV工艺上,领先的是康宁和德国LPTK。国内的封测厂商如长电、华天、通富微都有相关技术的研究储备。半导体各细分子行业中,国内企业在封测领域与国际巨头的差距相对较小,同时,国内新建的晶圆厂逐渐进入量产阶段,产能较大幅度地提升将成为国内封测企业步入快速发展通道的有效驱动力,从国内几家领先封测企业的扩产来看,预计国内先进封测企业的高端先进封装将进一步扩大量产规模。同时,经过多年的技术和经验积累,封测行业进入门槛逐渐提升,领先企业迎发展黄金期。

1、 台积电

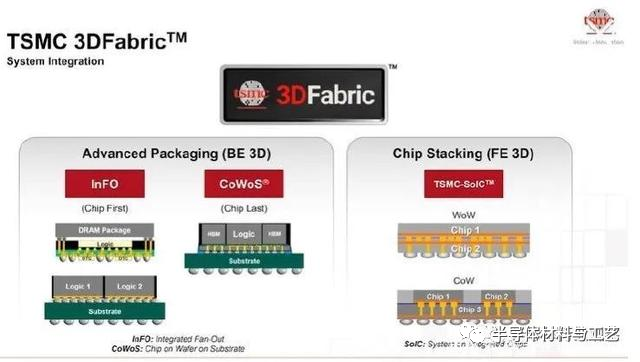

2012 年,TSMC 与 Xilinx 一起推出了当时最大的 FPGA,它由四个相同的 28 nm FPGA 芯片并排安装在中间层上。他们还开发了硅通孔(TSV),微凸点和再分布层(re-distribution-layer:RDL),以将这些组件连接在一起。台电基于其构造,封装这种封装解决方案,称为CooS(Chip-on-Wafer-Substrate)。支持的封装技术已成为高和高功率设计的实际行业标准。

台积电于2017年推出了InFO(Integrated FanOut technology)技术。它使用聚酰胺薄膜代替了CoWoS中的中间层,从而降低了单体成本和高度,这也是台积电成功应用的重要标准。货了海量用于智能手机的InFO设计。

台积电于2019年又推出了集成芯片系统(SoIC)技术。 借助前端(国外工厂)设备,台积电可以非常合理的压地,然后使用大量的吸塑的铜吸附进行焊(压焊)设计,以更小的形状因数,装扮和能力。这两种技术就逐渐演成了今天的 3D Fabric。

台积电将他们的 2.5D 和 3D 封装产品合并为一个单一的、全面的品牌3DFabric。

其中,2.5D封装技术CoWoS可分为 CoWoS 和 InFO 系列。首先看CoWoS技术,可以分为以下几种:

1)、CoWoS-S

用于die到die再分布层 (redistribution layer:RDL) 连接的带有硅中介层的“传统”基板上晶圆上芯片(chip-on-wafer-on-substrate with silicon interposer )正在庆祝其大批量制造的第 10 年。

2)、CoWoS-R

CoWoS-R 选项用有机基板中介层取代了跨越 2.5D die放置区域范围的(昂贵的)硅中介层。CoWoS-R 的折衷是 RDL 互连的线间距较小——例如,与 CoWoS-S 的亚微米间距相比,有机上的间距为 4 微米。

3)、CoWoS-L

在硅 –S 和有机 –R 中介层选项之间,TSMC CoWoS 系列包括一个更新的产品,具有用于相邻die边缘之间(超短距离)互连的“本地”硅桥。这些硅片嵌入有机基板中,提供高密度 USR 连接(具有紧密的 L/S 间距)以及有机基板上(厚)导线和平面的互连和功率分配功能。

再看2.5D封装技术InFO。

据介绍,InFO 在载体上使用(单个或多个)裸片,随后将这些裸片嵌入molding compound的重构晶圆中。随后在晶圆上制造 RDL 互连和介电层,这是“chip first”的工艺流程。单die InFO 提供了高凸点数选项,RDL 线从芯片区域向外延伸——即“扇出”拓扑。如下图所示,多die InFO 技术选项包括:

InFO-PoP:“package-on-package”

InFO-oS:“InFO assembly-on-substrate”

台积电的3D封装技术则是SoIC。据台积电介绍,公司的3D 封装与 SoIC 平台相关联,该平台使用堆叠芯片和直接焊盘键合,面对面或面对背方向 -表示为 SoIC 晶圆上芯片(chip on wafer)。硅通孔 (TSV) 通过 3D 堆栈中的die提供连接。SoIC 开发路线图如下所示——例如,N7-on-N7 芯片配置将在 21 年第四季度获得认证。

2、英特尔

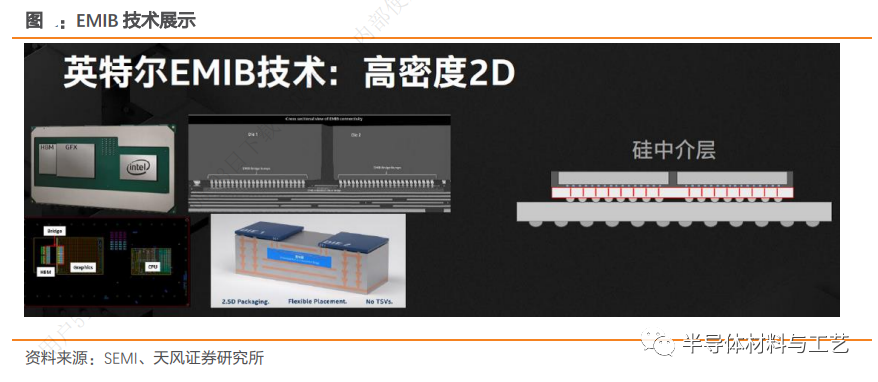

在2D的平面多芯片封装,英特尔独有的竞争优势是嵌入式多芯片互连桥接(EMIB)技术,可以实现更好的导线密度。在硅中介层硅通孔上放不同的裸片连接到整个基板,只需在局部进行高密度布线,而不必在全部的芯片上进行高密度布线,使成本大幅降低同时性能也得到优化。

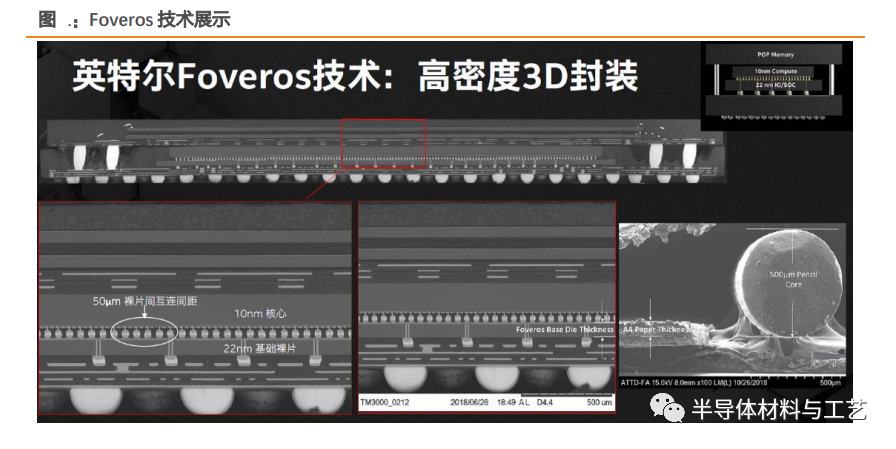

而在3D高密度微缩方面,英特尔的Foveros技术将多个单片连接到基础裸片,然后进行底层填充实现中间互连并进行注塑来保护整个芯片,使用焊接的技术已经可以做到20-30微米,而通过无焊料铜与铜的接口互连可突破20微米的瓶颈。

而在未来,封测技术相比较于现有的Foveros技术会更进一步。相比较于现有的技术,未来的凸块间距将会由50um缩小至10um,电路将更小更简洁,能耗也会更低。

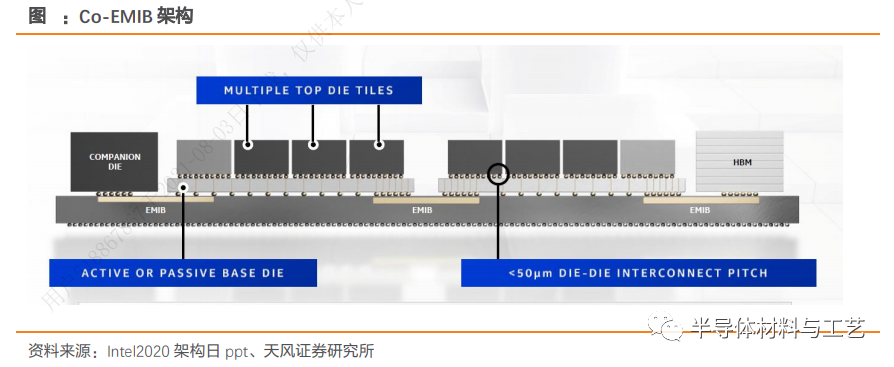

Foveros技术与EMIB集成产生了Co-EMIB(通过EMIB和Foveros两个技术之间的集成把2D和3D芯片进行融合)。Co-EMIB可以把超过两个不同的裸片进行水平和垂直方向叠加,以实现更好的灵活度。

全方位互连(ODI)改变了常规叠加方式下基础裸片尺寸必须大于上面叠加所有小芯片总和的限制。ODI的架构通过传统的硅通孔技术,使顶层小芯片可以与下方的芯片互连,这样就可以通过底层封装直接对上方小芯片进行供电,并保持上、下方裸片间直接互连。Adel Elsherbini介绍,通过这种并排互连形式延迟可下降2.5倍,功耗可以降低15%,带宽可以提高3倍。根据英特尔对先进封装的路线预测,在未来凸块间距将缩小至10um级别,密度将达到10000每平方毫米,能耗也会降低至0.05pj/bit。而ODI和CO-EMIB技术的应用,也会使先进封测进一步扩展应用范围。

先进封装的制程演进同先进制造工艺的制程呈现出同步趋势。在台积电等半导体制造厂制程逐渐进入5nm以下之际,先进封装的凸块间距也会逐渐进入10-20um区间。

3、 康宁

康宁公司是全球顶尖材料科学创新公司之一,在逾160年间提出多项玻璃解决方案,包括用于电子应用方面的液晶显示器(LCD)基板,以及用于电视机、智慧型手机和平板电脑等消费性电子装置,极为耐用的保护玻璃。

熔融制程为康宁的专利创新技术核心。这项高度精准且自动化的熔融下拉制程,生产出表面极为纯净光滑又平坦,且尺寸稳定的玻璃基板——这刚好是3DIC基板所要求的特性。

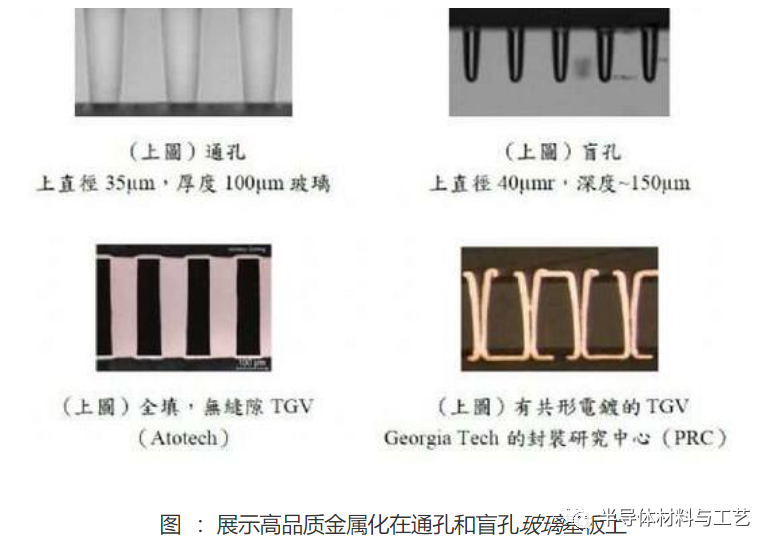

能够利用现有晶圆和面板设备制程是非常重要的一件事,盲孔填满金属化是最适用于现行以晶圆为基础的设备,而通孔金属化则最适合用于许多以面板为基础的制程。康宁已开发出制作高品质孔洞的先进制程,能在薄型(像是100μm)和厚型(例如700μm)玻璃上制作通孔和盲孔(请上图)。

再者,康宁已与产业领导厂商进行密切合作,运用以晶圆与面板为基础的金属化方式来填充玻璃孔洞。TGV基板的填充方式与终端应用息息相关,成本、生产能力、导电性、密闭度等要求会影响到金属化的方式。因此康宁与产业多个单位合作,像是RTI、Atotech、i3Electronics、工研院(ITRI)、GeorgiaTech的封装研究中心等,证明出完整的金属化技术的适用性和可用性。此用来验证的玻璃基板晶片测试结果显示出,相对于矽基板,使用玻璃孔洞能达到更好的电性、热和可靠性表现(请见上图)。

利用面板相关制程来达到经济规模制造的能力,是另一项落实成本效益的重要因素。目前业界已有许多设备能被应用来制造面板形式的穿孔玻璃载板和其对应的电子元件,包括填孔步骤和微影制程。

日前康宁已与RudolphTechnologies、i3Electronics与Atotech完成合作,证明出运用现有机台设备来制造面板形式的穿孔玻璃载板和其电子元件,包括填孔步骤和微影制程。RDL(RedistributionLayers)的结果显示出,能准确将金属镀在玻璃上(请见上图)。

据麦姆斯咨询报道,Corning Incorporated(康宁)和Menlo Micro(以下简称Menlo)近日联合宣布,Menlo革命性数字微开关(DMS)技术平台的开发实现了重要的里程碑,Menlo将重塑电子系统最基本的构建模块——电子开关。两家公司共同发布展示了成功整合的玻璃通孔(TGV)封装技术,使Menlo的高性能RF和功率产品扩展至超小型晶圆级封装。

TGV相比传统的键合封装技术,使Menlo的产品尺寸缩小了60%以上,使其更理想地适用于那些信道密度增长,同时尺寸、重量、功率和成本降低的非常重要应用。Menlo将在本周于美国费城举办的IEEE MTT国际微波会议上展示这项技术。

此外,除了显著的尺寸减小,TGV还为Menlo的DMS产品带来的重要的性能优势。通过更短且良好控制的金属化通孔替代键合,现在Menlo得以降低75%以上的封装寄生效应。这将帮助Menlo的产品支持更高的频率,这对于先进的无线通讯系统、测试仪器以及众多的航空和国防应用,正变得越来越重要。与此同时,玻璃相比硅等传统的基板材料具有独特的性能,可实现更低的RF损耗和更高的线性度,意味着系统将获得更低的功耗和更高的整体效率。

通过利用TGV封装技术,Menlo正在开发覆盖DC~18 GHz带宽的RF产品,并有能力逐步扩展至50 GHz以上。其DMS平台可为RF和AC/DC产品实现数十种高价值应用,包括电池管理、家居自动化、电气化汽车、军事和专业无线电、无线基站以及物联网等广泛市场。

4、 德国LPKF

LPKF深耕激光领域多年,对于如何将激光作为工具集成为功能强大的设备有着丰富的技术经验。LPKF激光系统立足于助力高科技领域的进步。无论是移动系统、通信系统、电力以及数字娱乐等,最终目标都是加工产品的速度更快、尺寸更小、更节能。德国LPKF始终保持着在激光技术领域的领先地位。我们的激光系统在印刷电路板、微芯片、汽车零部件、太阳能电池板以及许多其他零部件的工艺制造中都起着至关重要的作用。

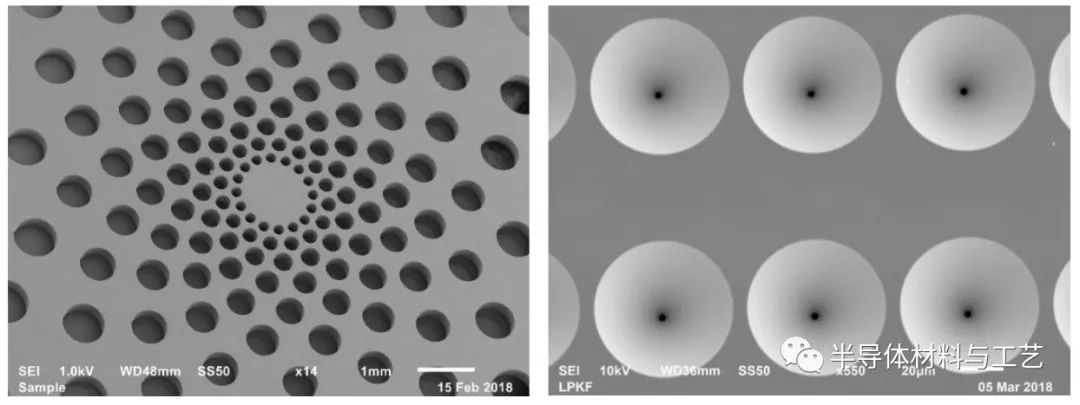

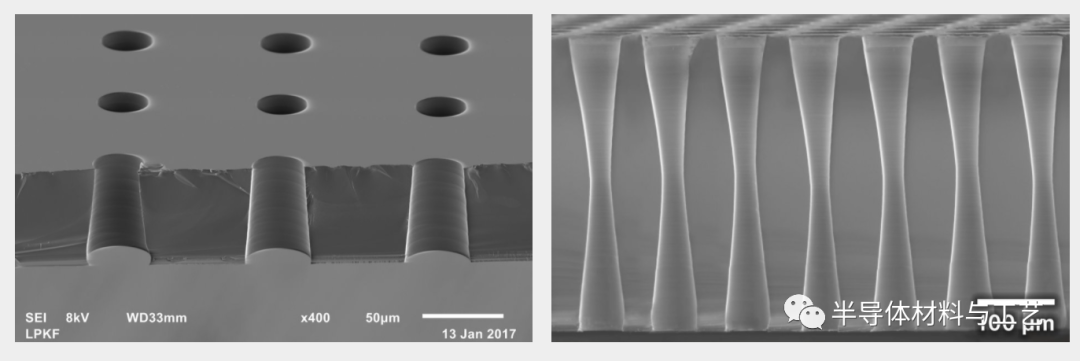

凭借几十年的激光加工经验,LPKF提供了前沿的技术解决方案,具有更高的精度、成品率和成本效率等系统优势,引领不断走向小型化的趋势。该产品包含许多优势:一种新型玻璃通孔(TGV)加工工艺全面开启了薄片玻璃作为封装基板的潜力。厚度介于50微米至500微米之间的薄片玻璃是一种非常适用于高密度高频应用的封装基板材料。LPKF运用激光这种非接触精密加工工具开发的创新LIDE 工艺能够以无以伦比的效率和质量微加工玻璃通孔。

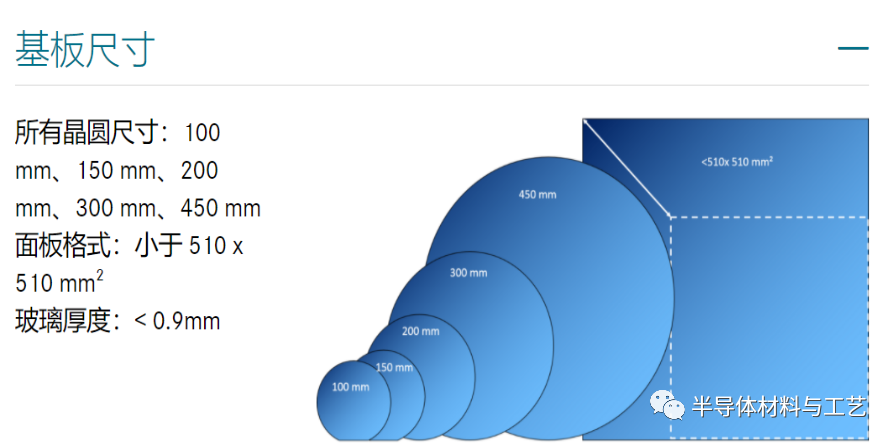

LPKF的最小通孔直径为10 µm。通常,一个基板上的所有微孔都显示相同的直径。通过应用多次蚀刻运行,不同的直径是可能的。纵横比在 1:10 的范围内,但根据玻璃类型,它也可以高达 1:50。LIDE 生成的微孔侧壁光滑、无裂纹、无碎屑和无应力,可实现可靠的金属化。锥角在0.1°-30°之间。LIDE 制造的微孔通常呈沙漏形状。通过将蚀刻限制为仅从先前修改过的玻璃的一侧进行,V 形微孔是可能的。加工的尺寸选择如图:

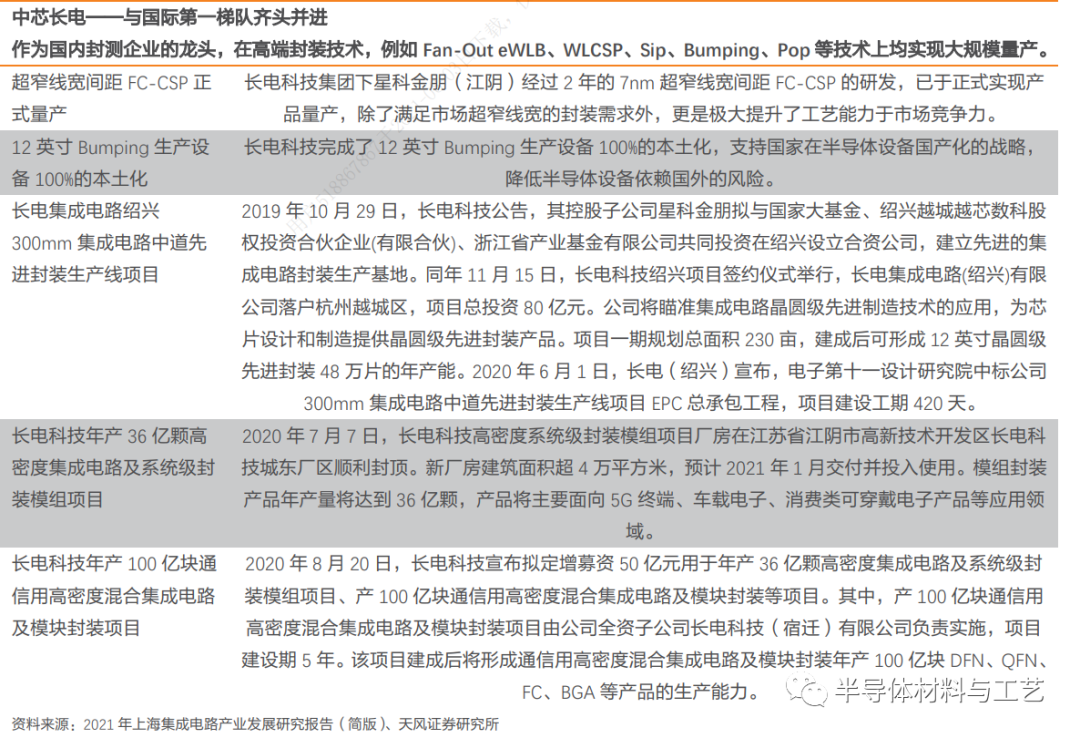

5、 中芯长电

长电科技是全球领先的封测厂商,聚焦关键应用领域,在5G通信类、高性能计算、消费类、汽车和工业等重要领域,业务覆盖高/中/低端全品类,已成为中国第一大和全球第三大封测企业。公司封测产能多地布局,互为补充,各具技术特色和竞争优势;公司在主要封装领域内掌握多项核心技术,在先进封装技术覆盖度上与全球第一的日月光集团旗鼓相当,具备行业领先的SiP、WL-CSP、FC、eWLB、PiP、PoP及2.5/3D等高端封装技术,并定增50亿元加码SiP、QFN、BGA等高端封装产能。公司与中芯国际战略互通,可实现代工+封测一体化协同发展。

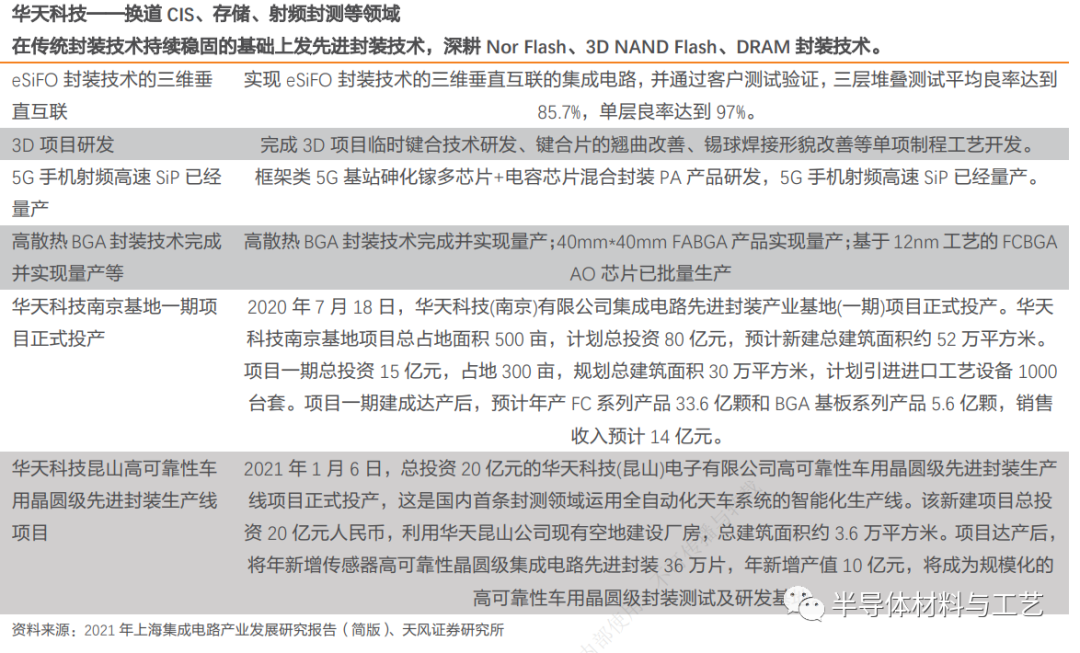

6、 华天科技

公司在产业布局方面,积极推进先进封装基地建设,近年来先后投资扩建了昆山、宝鸡、南京等基地,打通了CIS芯片、存储器、射频等多种高端产品的生产线。2020年7月18日华天科技南京基地举行了一期项目投产仪式,一期项目已竣工面积16.3万平方米,实现FC和BGA系列产品年封测量可达40亿只,今年可实现产值2亿元以上。

研发方面公司重视新产品、新技术、新工艺的研发,研发支出金额逐年增加,已自主研发出了SiP、FC、TSV、MEMS、Bumping、Fan-Out、WLP等高端封装技术和产品。自2019下半年来,国内半导体封测行业逐步回暖,未来有望随着新型应用领域和先进封测技术的发展进入新一轮增长。华天科技作为国内领先的集成电路封测企业,产品线布局丰富,技术水平行业领先,有望持续受益行业景气度及国产替代加速影响,未来发展前景广阔。

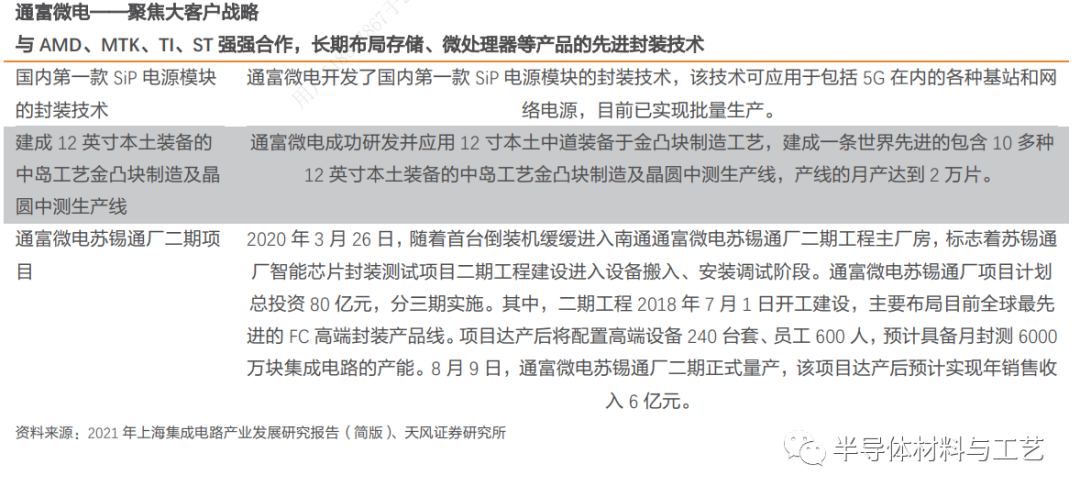

7、通富微电

通富微电为半导体封测龙头,与AMD、MTK等大客户共同成长。公司为全球第五大、国内第二大封测厂商,在封测技术上布局全面。早期公司以传统封装技术为主,2016年收购AMD苏州、槟城两大封测厂,得以深度绑定AMD供应链并占据AMD封测订单的大部分份额。同时公司凭借在高端封装领域的实力,成为MTK在中国大陆的重要封测合作方。展望未来,公司有望伴随大客户份额的提升和市场整体规模的扩大而迎来加速成长。

先进封装因5G、AI的应用迎来快速成长,公司技术领先有望充分受益。传统封测市场近年增速较为平稳,2011-2018年市场年复合增速在3%,至2018年空间达560亿美元。然而,随着摩尔定律的放缓,半导体性能的提升越来越多依赖于封装技术的进步,从而对封装技术提出更高要求。具体来看,随着5G、AI芯片的大规模应用,以及终端设备小型化趋势的演绎,全球先进封装市场有望快速成长:据Yole预计,先进封装市场至2024年有望达440亿美元,2018-2024年CAGR达8%。公司通过对AMD苏州、槟城厂的收购,增强了先进封装的技术实力,未来有望充分受益于先进封装市场的快速增长。

审核编辑:刘清

-

先进封装之TSV及TGV技术初探2023-05-23 5977

-

先进封装关键技术之TSV框架研究2023-08-07 3582

-

先进封装中的TSV分类及工艺流程2025-07-08 4793

-

玻璃基板时代,TGV技术引领基板封装2024-05-30 5977

-

什么是TSV封装?TSV封装有哪些应用领域?2018-08-14 93053

-

先进封装之TSV、TGV技术制作工艺和原理2023-04-13 29146

-

什么是先进封装技术的核心2023-08-05 1142

-

什么是先进封装?先进封装技术包括哪些技术2023-10-31 4230

-

开启高性能芯片新纪元:TSV与TGV技术解析2024-04-03 6900

-

高性能半导体封装TGV技术的最新进展2024-12-06 5458

-

先进封装中的TSV/硅通孔技术介绍2024-12-17 4405

-

先进封装技术蓬勃兴起:瑞沃微六大核心技术紧随其后2024-12-03 1775

-

玻璃通孔(TGV)技术深度解析2025-02-02 8474

-

先进封装中TSV工艺需要的相关设备2025-02-19 2554

-

TGV和TSV技术的主要工艺步骤2025-06-16 2333

全部0条评论

快来发表一下你的评论吧 !