FPGA设计中如何防止信号被优化

描述

本文分别对quartus和vivado防止信号被优化的方法进行介绍。

为什么要防止信号被优化

在FPGA开发调试阶段,经常遇到这样的情况,需要临时添加信号,观察信号变化,用来定位代码中存在的问题,很多时候这些临时添加的信号会被综合工具优化掉,为了防止这种情况的发生,可以使用添加虚拟引脚(quartus)和代码中添加属性(vivado)。

下面分别对两种方法进行说明,在原有代码中加入如下代码,观察cnt信号是否被优化,能否通过逻辑分析仪进行观测。

reg [3:0] cnt;

always@(posedge clk,negedge locked)

begin

if(!locked)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

Quartus中如何设置虚拟引脚

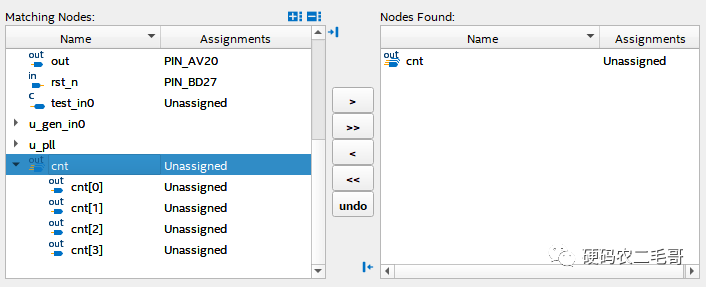

在quartus中加入上述代码后,将cnt信号设置成输出引脚。 下面将cnt信号设置为虚拟引脚。

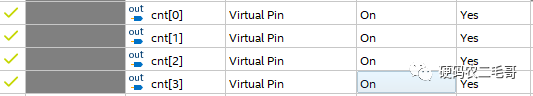

方法1:

在qsf文件中添加如下内容:

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[0]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[1]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[2]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[3]

编译后,添加signal tap,cnt信号可以添加,说明没有被优化。

方法2:

将cnt信号设置成输出后,打开Assignment Editor,进行如下设置。

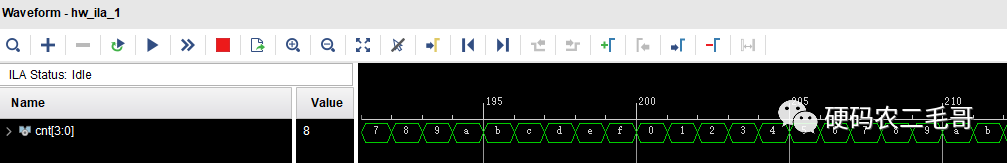

Vivado中防止信号被优化

在代码中加入(* dont_touch = "true" *) 。

(* dont_touch = "true" *) reg [3:0] cnt;

always@(posedge clk,negedge locked)

begin

if(!locked)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

重新编译后,使用ila观测cnt,ila中有信号,证明信号没有被优化。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

数字IC/FPGA设计中的时序优化方法2025-12-09 3654

-

浅谈寄存器被优化的原因2023-09-26 2544

-

FPGA在线调试信号被优化原因分析及防止优化方法总结2023-06-20 3642

-

今日说“法”:如何防止reg、wire型信号在使用逻辑分析仪时被优化2023-05-16 1037

-

PCB设计中的高速信号传输优化技巧2023-05-08 3283

-

如何使用Xilinx的FPGA对高速PCB信号实现优化设计2021-01-13 1307

-

STM32F745通过FMC访问FPGA顺序被优化2020-04-15 2657

-

信号管脚任务可进行多个FPGA的I/O优化2019-10-14 3944

-

Vivado防止信号被综合掉的三种方法2018-06-01 14147

-

怎样防止手机被屏蔽2017-12-21 59112

-

FPGA信号处理算法设计、实现以及优化(南京)2016-12-26 867

-

FPGA中的I_O时序优化设计2012-08-12 2429

-

防止Wi-Fi信号被截获的墙纸(英国开发)2010-01-14 2013

-

如何有效防止FPGA设计被克隆?2010-01-04 1729

全部0条评论

快来发表一下你的评论吧 !