复位电路设计分析

电子说

描述

复位对数字电路的重要性

我们在数字电路设计时,为了使系统在上电后处于 已知的确定状态 ,常使用复位电路来实现这一目的。复位是数字逻辑电路所必须的,无论是最简单的数字时序逻辑门电路,还是复杂的 MCU、ARM、DSP、FPGA 系统,凡是有时序要求的数字逻辑电路系统,都需要复位信号。复位状态通常是一个电路系统的初始条件,复位信号的有效使电路的状态进入设计者预先设定的状态,通常在系统初始化时或者系统死机硬重启时有效。通常复位信号还与系统的启动时序密切相关,它与系统各电源域的时序必须满足一定的先后关系,系统才能正常运行。可见,复位信号在系统中具有十分重要的地位。

最简单的复位电路分析

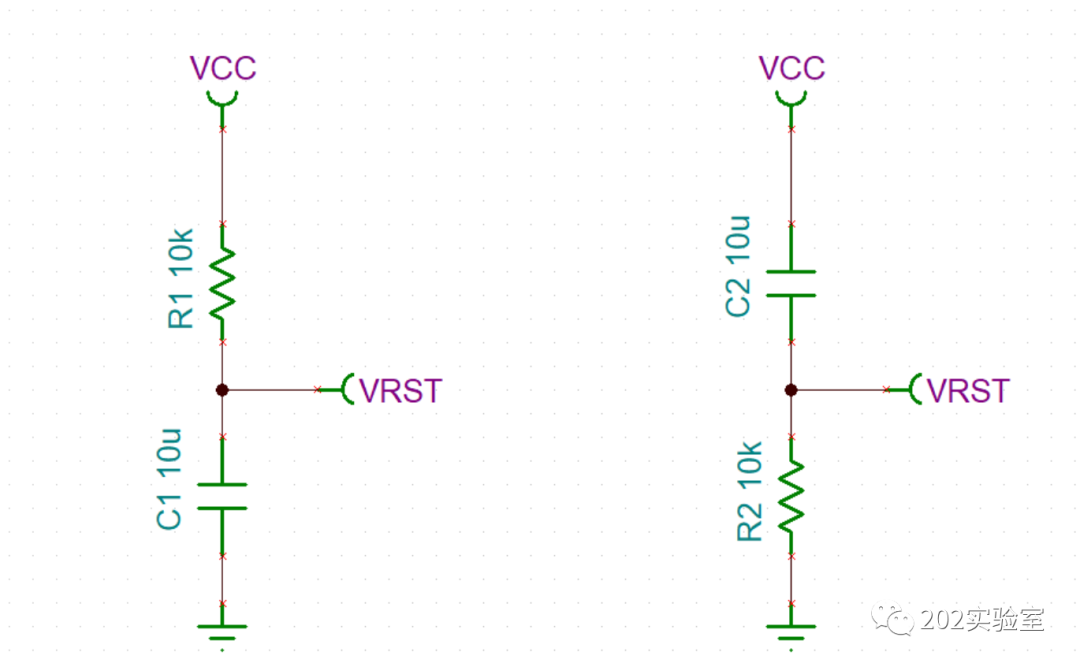

在一些时序和可靠性要求不高的场合,RC 电路是最为常用的复位电路形式。复位信号一般有高有效和低有效两种形式,对应的电路形式如下图所示,下图的左侧为低有效形式,而右侧为高有效形式。

RC复位电路

下面对左侧低有效电路做简要分析。根据电路的零状态(电路中所有的源为 0 的状态)响应特点,当电路上电时,电源电压 VCC 立即达到稳定值,电容 C1 两端电压为 0V;随后电路通过 R1 对 C1 充电,随着时间推移,C1 电压逐渐上升。当 VRST 的电压达到芯片的 时,芯片复位完成,进入正常工作状态。

我们把 RC 叫作 RC 电路的时间常数,若令 **\\tau=RC**,根据电路理论,可以推导出 RC 电路中电容两端电压(VRST)随充电时间 t 的变化关系。其公式如下:

可见,随着时间的推移,VRST 将逐渐接近 VCC,但理论上永远不能达到 VCC。一般当 时电压可上升到 0.63VCC; 时,VRST=0.86VCC; 时,VRST=0.95*VCC; 时,VRST=0.98*VCC; 时,VRST=0.99*VCC;工程上一般认为到了 就算充电完成了。

下图是串联 RC 电路的仿真结果验证,其中,R=10Kohm,C=10uF,也即 ,可见,其结果与理论分析完全吻合。

RC充电时间常数

简单复位电路的改进

上述复位电路虽然简单,但也存在一定的缺陷,如前所述,其只能用于时序和可靠性要求不高的场合。当电路掉电时,电容 C 两端电压接近 VCC,而电源电压则从 VCC 开始跌落直到 0V。由于芯片的 RST 引脚通常为高阻态,电容 C1 只能通过电阻 R1 放电,放电时电容两端电压与时间满足关系:

对于上述电路,其放电波形及对应的时刻如下如:

RC放电时间常数

可见,放电过程比较缓慢, 时,VRST=0.37*VCC。如果电路在短时间内发生掉电,并立即上电,那么可能存在由于电容两端的电量没有放尽,导致此时虽然电源已经重新上电,但由于复位电平不够低,复位并未可靠起效,引起系统状态紊乱。

如何通过电路设计改进该问题呢?其实改动也很简单,由于此时限制放电速度的是充电电阻,因此,只需要在电阻两端反向并联一只二极管,此二极管在电路上电时反偏,不影响电容充电。而当电源掉电时,二极管正偏导通,将短接电阻两端,形成电容的快速放电通路。电路如下所示:

改进的RC复位电路

下面我通过搭建实际电路,测试了没有放电二极管和增加放电二极管时电路充放电状态的对比,分别如下图所示:

RC复位上电对比

RC复位掉电对比

图中黄色曲线为 VCC 电压,而紫色曲线为 VRST 电压,左边为未加二极管的曲线,右边为增加后的情况,可见,该二极管对充电过程没有影响,只对掉电时的 VRST 下降速率有帮助。不过,这里也发现当 VRST 下降到一定值后仍然会比电源下降略慢,这是由于我这里使用的是高速开关二极管 1N4148,该二极管具有较高的正向导通压降(Max.=1V),因此,会在导通时致使 VRST 与电源间存在压差,这里最好使用 肖特基二极管 ,能够保证足够低的正向压降,更有利于 VRST 的快速掉电。

使用专用复位芯片

在一些要求比较高的场合,由于 RC 电路的时间常数受器件的离散型和温度影响较大,复位时间波动较大,RC 电路也不能实现电源轨的监控,因此简单的 RC 电路并不能满足电路性能的要求。这时候就需要使用专用的复位芯片来达到更可靠的复位。

一般专用的复位芯片在功能方面都比较全面。比如支持手动复位,支持单/多电源域监控(电源看门狗),支持开漏/推挽输出,支持复位释放时间可调(如 LM8365)等。

电压监控器是监控系统内一个或多个电源轨的器件。电压监控器可以检测欠压事件(电压低于某个阈值)或过压事件(电压超过某个阈值)。根据器件状态的不同,当受监控的电压轨电压低于或高于预设的阈值电压时,电压监控器会将信号置为使能、禁用或复位其他器件。

部分电压监控器可以同时监控欠压和过压情况,称为 窗口检测器 。电压监控器旨在确保系统正常上电,防止处理器发生欠压,同时实时监控系统,避免因电压轨超出规范而产生性能问题或系统故障。其工作原理通过下图表征:

电压监控器原理

带有电压监控器功能的复位 IC,能够保证复位的释放发生在电源供应正常之后,从而确保可靠复位。同时,若电源出现过压或跌落故障,芯片还能及时保护处理器,并在电源恢复后执行可靠复位重启。

为了适应不同的应用,复位 IC 通常还支持可选的高电平有效或低电平有效,推挽或开漏输出。推挽和开漏指的是输出驱动的类型,推挽输出在输出端使用两个晶体管。当顶部晶体管导通时,输出设置为高电平;底部晶体管导通时,输出设置为低电平。开漏输出仅使用一个晶体管,通过其将输出设置为低电平,同时另外使用一个上拉电阻代替顶部晶体管设置高电平输出。下图展示了开漏和推挽两种输出类型:

开漏和推挽输出

推挽式输出的优点是速度快并且功耗低。然而,开漏输出可以将多个监控器件的输出连接在一起,形成或/与逻辑输出配置,方便多电源轨的监控控制。

下图展示了来自 TI 的 LM3710 的典型应用电路和对应的时序图,除标准复位功能外,LM3710 还支持手动复位(MR)、电源故障输入(PFI)、看门狗输入(WDI)、看门狗定时器和低电压线路输出,支持为众多应用提供所需的灵活性。

上图中所示的应用电路使用 R1 和 R2 作为与 VIN2 相连的分压器,以便设置电源故障的复位阈值,实现对第二电源的监控。如果第二电源的电压降至电源故障复位阈值以下,PFI 引脚将变为低电平,PFO 引脚也随之降至低电平。

此引脚与 MR 引脚相连,因此将触发复位。如果在 WDI 引脚上的看门狗窗口内未检测到任何“喂狗”活动,也会发生复位。WDI 引脚可以与微处理器相连,通过使微处理器发送间歇性脉冲,检测其是否仍然正常工作。

当 VCC 处的电源电压降至比复位电压阈值低 2%左右时,低电压线路输出(LLO)引脚将变为低电平。LLO 引脚可以连接微处理器进行检测。当此引脚进入激活状态后,发送到微处理器的信号可能触发其他操作,例如向另一器件发送信号,或以 LED 闪烁等形式向用户报警。

时序图所示为监控第二电压输入(VIN2)的示例。当与 PFI 引脚相连的 VIN2 变为低电平后,PFO 引脚也将变为低电平,进而导致 MR 引脚降为低电平,随即触发复位。使用电源故障和手动复位功能的方法多种多样,用户可以根据应用需求自行选择。

总结

复位电路在数字系统中必不可少,看似简单的复位电路,其实在设计中也有许多关键点需要考虑,有时候更是决定了系统的可靠性与功能。如今很多芯片都内置了基本的复位电路,如 POR(上电复位),并支持一定的可配置。复位电路作为系统的敏感信号,在原理图设计和 Layout 时都需要格外小心,做好防护,防止受到如 ESD 之类的干扰。

针对最简单的 RC 复位电路,本文给出了一种通过增加肖特基二极管而实现的高性价比的优化方案,并对电路性能做了实验分析。如果你的系统需要更高的可靠性,那么,选用专用的复位和监控 IC 将是不错的选择,这些芯片通常具备丰富的功能和足够的灵活性,能够为系统提供更完整的可靠性保障,当然,这些是需要付出成本的。

-

PMOS电路设计分析2025-07-21 3565

-

资料下载:LED背光驱动电路设计分析2016-01-28 4217

-

组合逻辑控制器电路设计分析2007-12-18 848

-

复位电路设计选型指南2010-04-02 581

-

Excel进行电路统计分析2009-01-22 2444

-

滤波电路设计分析研究2009-11-30 1205

-

VHDL实用电路模块设计分析2011-03-02 929

-

51单片机几种实用的复位电路设计2016-03-14 925

-

高可靠性复位电路设计(电路设计与分析)2017-12-02 8395

-

使用OrCAD PSpice实现放大电路的设计分析2019-12-24 2064

-

电源电路设计分析实例(经典分析)2021-04-16 1305

-

stm32复位电路设计2022-06-26 1286

-

stm32f722参考电路设计分析2023-01-10 763

-

FPGA内部自复位电路设计方案2023-04-06 2398

-

STM32复位电路用复位芯片和阻容复位电路区别2024-08-06 4203

全部0条评论

快来发表一下你的评论吧 !