PCIe管道接口的电源管理

描述

最近,我们看到了串行数据传输代替并行数据传输的趋势,以提高性能和数据完整性。这方面的一个例子是从PCI / PCI-X迁移到PCI Express。两个器件之间的串行接口可减少每个器件封装的引脚数。这不仅降低了芯片和电路板设计成本,还降低了电路板设计的复杂性。由于串行链路的时钟速度比并行链路快得多,因此它们在性能方面具有高度可扩展性。

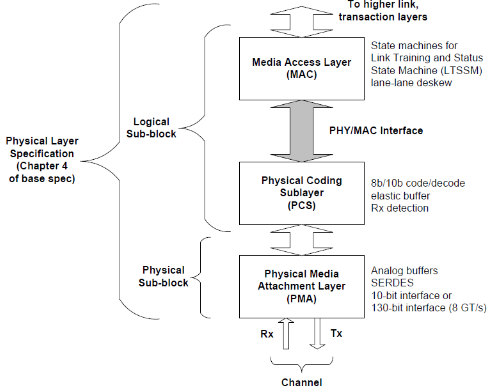

然而,为了加速基于 PCI Express 的子系统的验证并加快 PCI Express 端点的开发时间,PIPE(PCI Express 架构的 PHY Interface 由英特尔定义,并于 2002 年发布以供行业审查。PIPE 是在处理较低级别的串行信令的 PHY 子层和处理寻址/访问控制机制的媒体访问层 (MAC) 之间定义的标准接口。下图说明了 PIPE 在为 PCI Express 的 PHY 层分区中所扮演的角色。

分区物理层(来源:PCI Express 架构规范的 PHY 接口,版本 2.00)

借助此接口,开发人员可以验证其设计,而不必担心与 Phy 接口相关的模拟电路。对于MAC内核验证,PHY总线功能模型(BFM)将直接连接到它。如果没有PIPE,则需要将PHY和Serdes(序列化器/解串器)组合以及根复合体BFM一起使用。此外,用户必须确保 PHY 和 SerDes 行为以及串行接口的正确性。

鉴于PIPE接口的价值,它现在被广泛使用。在我们最近的经验中,我们观察到 PIPE 接口中的不同电源状态可能会在它们的解释方面造成一些混乱。这篇博文和下一篇将阐明此接口的不同电源状态。希望这将导致对相同的更好理解。这里的假设是读者对 PCIe LTSSM 有很高的了解。

管道的电源状态

电源管理信号使PHY能够最大限度地降低功耗。为此接口定义了四种电源状态:P0、P0、P1 和 P2。P0 状态是 PHY 的正常运行状态。当它从P0过渡到低功耗状态时,PHY可以立即采取适当的节能措施。

所有电源状态都由信号断电 [2:0](MAC 输出)表示。位表示形式如下:

2] [1] [0] 描述

0 0 0 P0,正常运行

0 0 1 P0s,低恢复时间延迟,省电状态

0 1 0 P1,恢复时间延迟更长,功耗状态更低

0 1 1 P2,最低功耗状态。

PIPE 接口电源状态可以与基本规范中提到的 LTSSM 的电源状态相关联。

P0 等效于数据/订单集可以传输的 LTSSM 状态

P0s 相当于 LTSSM 的 L0

P1 等效于禁用、所有检测和 L1。LTSSM 的空闲状态

P2 相当于 LTSSM 的 L2

在 P0、P0 和 P1 状态中,需要 PHY 来保持 PCLK 正常运行。对于这三种状态之间的所有状态转换,PHY 指示通过 PhyStatus 的单周期断言成功转换到指定的电源状态。

MAC 可能导致 PHY 进行一组有限的合法电源状态转换。参考基本规范中 LTSSM 的主状态图以及前面段落中描述的 LTSSM 状态到 PHY 电源状态的映射,这些法律转换是:

P0 到 P0s

P0 至 P1

P0 至 P2

P0s 到 P0

P1 至 P0

P2 至 P1

审核编辑:郭婷

-

家用电脑的PCIe接口如何设计PCB?2024-11-05 5749

-

PCIe总线的电源管理之去耦电容2020-12-22 9562

-

FPGA的PCIE接口应用需要注意哪些问题2024-05-27 3441

-

嵌入式接口通识知识之PCIe接口2025-08-21 2005

-

VisualNet地税管道资源管理系统2014-01-16 1831

-

VisualNet地税管道综合资源管理系统2014-02-22 2307

-

PCIE接口的REFCLK的如何设计?2018-06-21 6281

-

请问DSP6678的PCIe接口怎么使用?2018-08-02 4314

-

如何使用AXI配置的ILA调试PCIe AXI接口?2019-09-25 3520

-

PCIe 5.0的接口设计有多难?2021-06-17 2275

-

如何使用电源管理接口2021-12-30 1173

-

常见PCIe电源管理简介2023-12-16 7869

-

pcie4.0和pcie3.0接口兼容吗2024-07-10 16663

-

PCIe接口的工作原理 PCIe与PCI的区别2024-11-06 6378

-

pcie接口类型及其应用2024-11-13 6435

全部0条评论

快来发表一下你的评论吧 !